13.根据本公开,关于半导体集成电路装置,能够充分抑制闩锁现象的发生。

附图说明

14.图1是示意性地示出实施方式所涉及的半导体集成电路装置的整体结构的俯视图;

15.图2是第一实施方式所涉及的输出电路的电路结构图;

16.图3是第一实施方式所涉及的输出电路的平面版图构造之例;

17.图4是esd保护二极管的版图构造之例;

18.图5是esd保护二极管的版图构造之例;

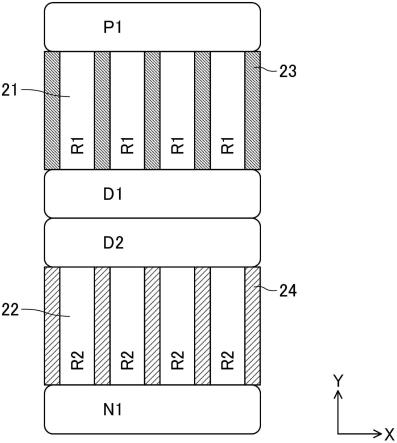

19.图6是保护电阻的版图构造之例;

20.图7是保护电阻的版图构造之例;

21.图8是输出晶体管的版图构造之例;

22.图9是输出晶体管的版图构造之例;

23.图10是用于说明如何抑制闩锁现象的发生的图;

24.图11是第一实施方式所涉及的输出电路的平面版图构造的另一例;

25.图12是第二实施方式所涉及的输出电路的电路结构图;

26.图13是第二实施方式所涉及的输出电路的平面版图构造之例;

27.图14中的(a)、(b)是第二实施方式所涉及的输出电路的平面版图构造的另一例。

具体实施方式

28.下面,参照附图对实施方式进行说明。需要说明的是,在下述说明中,“vddio”、“vss”是指电源电压或电源本身。此外,晶体管是指形成在p型衬底和n型阱上的晶体管。需要说明的是,晶体管可以形成在p型阱上,也可以形成在n型衬底上。

29.(第一实施方式)

30.图1是示意性地示出实施方式所涉及的半导体集成电路装置的整体结构的俯视图。图1所示的半导体集成电路装置1包括形成有内部核心电路的核心区2和设在核心区2的周围且形成有接口电路(i/o电路)的i/o区3。在i/o区3,以环状包围半导体集成电路装置1的周边部的方式,形成有i/o单元列10a。在i/o单元列10a中,排列有构成接口电路的多个i/o单元10,在图1中简化图示。在半导体集成电路装置1中,布置有多个外部连接焊盘,在图1中省略图示。

31.图2是i/o单元10中包括的输出电路11的电路结构图。需要说明的是,在实际的输出电路中,还包括图2所示的电路要素以外的要素,在图2中省略记载。

32.图2所示的输出电路11包括外部输出端子out、输出晶体管p1、n1、esd(electrostatic discharge)保护二极管d1、d2以及保护电阻r1、r2。输出晶体管p1是p导电型的晶体管,输出晶体管n1是n导电型的晶体管。

33.输出晶体管p1、n1根据栅极接收的信号,向外部输出端子out输出输出信号。输出晶体管p1的源极与vddio相连,输出晶体管p1的漏极通过保护电阻r1与外部输出端子out相连。输出晶体管n1的源极与vss相连,输出晶体管n1的漏极通过保护电阻r2与外部输出端子out相连。保护电阻r1、r2例如由布线电阻构成,通过形成在扩散层、栅极布线层或金属布线

层上的布线、它们的组合来实现布线电阻的布线。

34.esd保护二极管d1设在vddio与外部输出端子out之间,esd保护二极管d2设在vss与外部输出端子out之间。如果高压噪声输入外部输出端子out,则电流通过esd保护二极管d1、d2流入vddio、vss,这样一来,输出晶体管p1、n1就受到保护。

35.图3是示出本实施方式所涉及的输出电路11的平面版图构造的一例的简图。x方向(附图中横向)是i/o单元10的排列方向,y方向(附图中纵向)是从核心区2朝向芯片端的方向。附图中上侧是核心区2侧,附图中下侧是芯片端侧。对图3的各区,标注与图2的电路图中所对应的电路要素相同的符号。

36.esd保护二极管d1、d2布置在y方向上的中央部。输出晶体管p1布置在esd保护二极管d1的附图中上侧且与esd保护二极管d1分离。输出晶体管n1布置在esd保护二极管d2的附图中下侧且与esd保护二极管d2分离。

37.保护电阻r1布置在输出晶体管p1与esd保护二极管d1之间。保护电阻r1分在多个区域(电阻区)21形成。在图3的例子中,保护电阻r1呈沿y方向延伸的矩形状,且分成在x方向上排列的四个电阻区21。抽头区23以夹住各电阻区21的方式布置,在抽头区23形成有向p型衬底供给vss的抽头。

38.保护电阻r2布置在输出晶体管n1与esd保护二极管d2之间。保护电阻r2分在多个区域(电阻区)22形成。在图3的例子中,保护电阻r2呈沿y方向延伸的矩形状,且分成在x方向上排列的四个电阻区22。抽头区24以夹住各电阻区22的方式布置,在抽头区24形成有向n型阱供给vddio的抽头。

39.需要说明的是,在esd保护二极管d1、d2的上层,有未图示的焊盘,该焊盘分别与半导体集成电路装置的外部相连。

40.下面说明各电路要素的版图构造的详情。

41.(esd保护二极管的版图构造)

42.图4示出esd保护二极管d2的版图构造例。不过,省略布线层等的图示。

43.如图4所示,esd保护二极管d2形成在中央部的p衬底区域。esd保护二极管d2包括由p导电型的鳍32形成的阳极部31和由n导电型的鳍34a、34b形成的阴极部33a、33b。鳍32、34a、34b沿x方向延伸。阳极部31与vss相连,阴极部33a、33b与外部输出端子out相连。在p导电型的鳍32与n导电型的鳍34a、34b之间形成有二极管。

44.此外,在esd保护二极管d2的周围形成有保护环81。保护环81包括形成在n阱的n导电型的鳍82。鳍82沿x方向延伸。鳍82与vddio相连。

45.在阳极部31的鳍32和阴极部33a、33b的鳍34a、34b上,形成有虚设栅极41。在保护环81的鳍82上,形成有虚设栅极42。虚设栅极41、42沿y方向延伸。通过设置虚设栅极41、42,来提高半导体集成电路装置的栅极图案的均匀性,由此,提高半导体集成电路装置的可靠性和成品率。

46.需要说明的是,也可以不设置虚设栅极41、42。此外,也可以不形成保护环81。

47.图5示出esd保护二极管d1的版图构造例。不过,省略布线层等的图示。

48.如图5所示,esd保护二极管d1形成在中央部的n阱。esd保护二极管d1包括由n导电型的鳍37形成的阴极部36和由p导电型的鳍39a、39b形成的阳极部38a、38b。鳍37、39a、39b沿x方向延伸。阴极部36与vddio相连,阳极部38a、38b与外部输出端子out相连。在n导电型

的鳍37与p导电型的鳍39a、39b之间形成有二极管。

49.此外,在esd保护二极管d1的周围形成有保护环83。保护环83包括形成在p衬底区域的p导电型的鳍84。鳍84沿x方向延伸。鳍84与vss相连。

50.在阴极部36的鳍37和阳极部38a、38b的鳍39a、39b上,形成有虚设栅极43。在保护环83的鳍84上,形成有虚设栅极44。虚设栅极43、44沿y方向延伸。通过设置虚设栅极43、44,来提高半导体集成电路装置的栅极图案的均匀性,由此,提高半导体集成电路装置的可靠性和成品率。

51.需要说明的是,也可以不设置虚设栅极43、44。此外,也可以不形成保护环83。

52.(保护电阻的版图构造)

53.图6示出保护电阻r2的版图构造例。不过,省略布线层等的图示。

54.如图6所示,也如图3所示,保护电阻r2构成为分成在x方向上排列的四个电阻区22。在各电阻区22,形成有栅极布线51,通过由未图示的布线连接栅极布线51来构成一个或多个电阻。栅极布线51形成在n型阱上。

55.抽头区24以夹住各电阻区22的方式布置。在各抽头区24,n导电型的鳍52形成在n阱上,鳍52成为抽头。各鳍52沿x方向延伸,且与vddio相连。在各鳍52上,形成有沿y方向延伸的虚设栅极45。

56.需要说明的是,虽然将构成保护电阻的栅极布线51形成在n型阱上,但也可以形成在p型衬底上。此外,也可以是:抽头区24的抽头是形成在p型衬底上的p导电型的鳍,且与vss相连。

57.图7示出保护电阻r1的版图构造例。不过,省略布线层等的图示。

58.如图7所示,也如图3所示,保护电阻r1构成为分成在x方向上排列的四个电阻区21。在各电阻区21,形成有栅极布线53,通过由未图示的布线连接栅极布线53来构成一个或多个电阻。栅极布线53形成在n型阱上。

59.抽头区23以夹住各电阻区21的方式布置。在各抽头区23,p导电型的鳍54形成在p型衬底上,鳍54成为抽头。各鳍54沿x方向延伸,且与vss相连。在各鳍54上,形成有沿y方向延伸的虚设栅极46。

60.需要说明的是,虽然将构成保护电阻的栅极布线53形成在n型阱上,但也可以形成在p型衬底上。此外,也可以是:抽头区23的抽头是形成在n型阱上的n导电型的鳍,且与vddio相连。

61.需要说明的是,在本例中,保护电阻由栅极布线构成,但不限于此,也可以由鳍、金属布线等构成。或者,也可以由栅极布线、鳍、金属布线等的组合来构成电阻。

62.此外,也可以不设置虚设栅极45、46。

63.此外,此处,虽然抽头具有鳍构造的扩散区,但不限于此。

64.(输出晶体管的版图构造)

65.图8示出输出晶体管n1的版图构造例。不过,省略布线层等的图示。

66.如图8所示,在位于中央部的输出晶体管n1的区域,形成有分别沿x方向延伸且沿y方向排列布置的多个n导电型的鳍61和分别沿y方向延伸且沿x方向排列布置的多个栅极布线62。俯视时重合的鳍61和栅极布线62形成晶体管。各晶体管通过未图示的布线并联连接。各晶体管的漏极通过保护电阻r2与外部输出端子out相连。

67.此外,在输出晶体管n1的周围形成有保护环85。保护环85包括形成在p衬底的p导电型的鳍86。鳍86沿x方向延伸。鳍86与vss相连。在鳍86上,形成有虚设栅极47。

68.需要说明的是,也可以不设置虚设栅极47。此外,也可以不形成保护环85。

69.图9示出输出晶体管p1的版图构造例。不过,省略布线层等的图示。

70.如图9所示,在位于中央部的输出晶体管p1的区域,形成有分别沿x方向延伸且沿y方向排列布置的多个p导电型的鳍66和分别沿y方向延伸且沿x方向排列布置的多个栅极布线67。俯视时重合的鳍66和栅极布线67形成晶体管。各晶体管通过未图示的布线并联连接。各晶体管的漏极通过保护电阻r1与外部输出端子out相连。

71.此外,在输出晶体管p1的周围形成有保护环87。保护环87包括形成在n阱的n导电型的鳍88。鳍88沿x方向延伸。鳍88与vddio相连。在鳍88上,形成有虚设栅极48。

72.需要说明的是,也可以不设置虚设栅极48。此外,也可以不形成保护环87。

73.根据本实施方式,输出晶体管p1与和外部输出端子out相连的esd保护二极管d1分离布置,且在输出晶体管p1与esd保护二极管d1之间布置有保护电阻r1。输出晶体管n1与和外部输出端子out相连的esd保护二极管d2分离布置,且在输出晶体管n1与esd保护二极管d2之间布置有保护电阻r2。这样一来,施加到外部输出端子out的噪声在到达输出晶体管p1、n1之前,被保护电阻r1、r2衰减。此外,保护电阻r1分在多个电阻区21形成,在电阻区21彼此之间的抽头区23,形成有向p型衬底供给vss的抽头。保护电阻r2分在多个电阻区22形成,在电阻区22彼此之间的抽头区24,形成有向n型阱供给vddio的抽头。这样一来,施加到外部输出端子out的噪声会通过抽头被吸收。因此,能够抑制作为闩锁现象发生原因的噪声的传播。并且,由于抽头区23、24分散成多个,所以能够更均匀地得到吸收噪声的效果。

74.使用图10,说明如何抑制闩锁现象的发生。图10是本实施方式所涉及的半导体集成电路装置的示意性剖视图。从附图中右侧起依次排列有esd保护二极管d2、保护电阻r2和阱抽头部(省略图示保护电阻r2)、输出晶体管n1以及其他晶体管。

75.此处,假设噪声施加到外部输出端子out(图10的a)。如果该噪声在未被充分减小的情况下传播到输出晶体管n1、其他晶体管的区域,则由于传播过来的噪声,电流会流入寄生双极晶体管的基极。因此,产生由寄生晶体管导致的闩锁现象,在vddio、vss之间产生大电流(图10的b)。

76.另一方面,根据本实施方式所涉及的结构,通过夹在esd保护二极管d2与输出晶体管n1之间的保护电阻r2,使二极管d2与其他晶体管之间的距离拉开,噪声被衰减。此外,通过设在保护电阻r2的区域的抽头,外部输出端子out的噪声(图10的a)被图10的d的路径吸收,能够抑制寄生双极晶体管的基极节点(图10的c)的电位变动。这样一来,能够抑制传播到输出晶体管n1、其他晶体管区域的噪声,能够抑制闩锁现象的发生。

77.(变形例)

78.图11是示出输出电路11的平面版图构造的另一例的简图。在图11的例子中,保护电阻r1呈沿x方向延伸的矩形状,且分成在y方向上排列的四个电阻区21a。抽头区23a以夹住各电阻区21a的方式布置,在抽头区23a形成有向p型衬底供给vss的抽头。

79.保护电阻r2呈沿x方向延伸的矩形状,且分成在y方向排列的四个电阻区22a。抽头区24a以夹住各电阻区22a的方式布置,在抽头区24a形成有向n型阱供给vddio的抽头。

80.在本变形例中,也能够得到与上述实施方式相同的作用和效果。即,施加到外部输

出端子out的噪声在到达输出晶体管p1、n1之前,被保护电阻r1、r2衰减。此外,施加到外部输出端子out的噪声会通过形成在抽头区23a、24a的抽头被吸收。因此,能够抑制作为闩锁现象发生原因的噪声的传播。并且,由于抽头区23a、24a分散成多个,所以能够更均匀地得到吸收噪声的效果。

81.需要说明的是,在图3中,保护电阻r1、r2在x方向上被分割开,在图11中,保护电阻r1、r2在y方向上被分割开,但也可以同时具有不同的分割方向。例如,也可以是保护电阻r1在x方向上被分割开且保护电阻r2在y方向上被分割开的版图。

82.(第二实施方式)

83.图12是本实施方式所涉及的输出电路12的电路结构图。图12的电路结构与图2的电路结构基本相同,但保护电阻的插入位置不同。即,在图12的输出电路12中,设有保护电阻r3来代替图2的保护电阻r1、r2。在图12中,输出晶体管p1、n1的漏极彼此相连,保护电阻r3设在外部输出端子out与输出晶体管p1、n1的漏极之间。

84.图13是示出本实施方式所涉及的输出电路12的平面版图构造的一例的简图。x方向(附图中横向)是i/o单元10的排列方向,y方向(附图中纵向)是从核心区2朝向芯片端的方向。附图中上侧是核心区2侧,附图中下侧是芯片端侧。对图13的各区,标注与图12的电路图中所对应的电路要素相同的符号。在esd保护二极管d1、d2的上层,有未图示的焊盘,该焊盘分别与半导体集成电路装置的外部相连。

85.esd保护二极管d1、d2在y方向上相邻布置。输出晶体管p1、n1在y方向上相邻布置。esd保护二极管d1、d2布置在y方向上的附图中的下部。输出晶体管p1、n1布置在esd保护二极管d1、d2的附图中的上侧且与esd保护二极管d1、d2分离。

86.保护电阻r3布置在输出晶体管p1、n1与esd保护二极管d1、d2之间。保护电阻r3分在多个区域(电阻区)121形成。在图13的例子中,保护电阻r3是沿y方向延伸的矩形状,且分为沿x方向排列的四个电阻区121。在电阻区121彼此之间,布置有形成有向p型衬底供给vss的抽头的抽头区122和形成有向n型阱供给vddio的抽头的抽头区123。在图13的例子中,抽头区122和抽头区123在y方向上交替地布置。即,在电阻区121彼此之间的单一区域(single region),形成有向p型衬底供给vss的抽头和向n型阱供给vddio的抽头。

87.根据本实施方式,输出晶体管p1、n1与和外部输出端子out相连的esd保护二极管d1、d2分离布置,且在输出晶体管p1、n1与esd保护二极管d1、d2之间布置有保护电阻r3。这样一来,施加到外部输出端子out的噪声在到达输出晶体管p1、n1之前,被保护电阻r3衰减。此外,保护电阻r3分在多个电阻区121形成,在电阻区121彼此之间的抽头区122,形成有向p型衬底供给vss的抽头,在电阻区121彼此之间的抽头区123,形成有向n型阱供给vddio的抽头。这样一来,施加到外部输出端子out的噪声会通过抽头被吸收。因此,能够抑制作为闩锁现象发生原因的噪声的传播。并且,由于抽头区122、123分散成多个,所以能够更均匀地得到吸收噪声的效果。

88.需要说明的是,形成有向p型衬底供给vss的抽头的抽头区122用于吸收来自esd保护二极管d1的噪声,形成有向n型阱供给vddio的抽头的抽头区123用于吸收来自esd保护二极管d2的噪声。

89.需要说明的是,esd保护二极管d1、d2的位置可以互换。此外,输出晶体管p1、n1的位置可以互换。

90.(变形例)

91.图14中的(a)、(b)是示出输出电路12的平面版图构造的另一例的简图。在图14中(a)的例子中,在电阻区121彼此之间,抽头区122a和抽头区123a在x方向上交替地布置,在抽头区122a形成有向p型衬底供给vss的抽头,在抽头区123a形成有向n型阱供给vddio的抽头。

92.在图14中(b)的例子中,保护电阻r3呈沿x方向延伸的矩形状,且分成在y方向上排列的四个电阻区121a。在电阻区121a彼此之间,布置有形成有向p型衬底供给vss的抽头的抽头区122b和形成有向n型阱供给vddio的抽头的抽头区123b。在图14中(b)的例子中,抽头区122b和抽头区123b在x方向上交替地布置。

93.需要说明的是,在图14中(b)的例子中,抽头区122b和抽头区123b也可以是在y方向上交替地布置。

94.在本变形例中,也能够得到与上述实施方式相同的作用和效果。即,施加到外部输出端子out的噪声在到达输出晶体管p1、n1之前,被保护电阻r3衰减。此外,施加到外部输出端子out的噪声会通过形成在抽头区122a、123a或抽头区122b、123b的抽头被吸收。因此,能够抑制作为闩锁现象发生原因的噪声的传播。并且,由于抽头区122a、123a或抽头区122b、123b分散成多个,所以能够更均匀地得到吸收噪声的效果。

95.需要说明的是,在上述实施方式中,保护电阻r1、r2、r3被分割为四个电阻区,但电阻区的数量不限于四个。

96.需要说明的是,在上述实施方式的输出电路中,p导电型晶体管和n导电型输出晶体管均为一级晶体管,但不限于此,例如也可以是二级、三级等多级晶体管串联连接而成的结构。此外,上述实施方式的输出电路也可以是包括输入电路的输入输出电路。

[0097]-产业实用性-[0098]

在本公开中,关于半导体集成电路装置,能够充分抑制闩锁现象的发生,所以有助于例如提高半导体芯片的性能。

[0099]-符号说明-[0100]1ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体集成电路装置

[0101]

11、12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出电路

[0102]

21、21a、22、22a

ꢀꢀ

电阻区

[0103]

52、54

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

鳍

[0104]

121、121a

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电阻区

[0105]

out

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

外部输出端子

[0106]

p1、n1

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

输出晶体管

[0107]

d1、d2

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

esd保护二极管

[0108]

r1、r2、r3

ꢀꢀꢀꢀꢀꢀꢀꢀ

保护电阻

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。