技术特征:

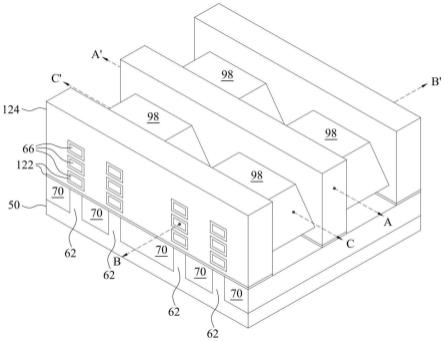

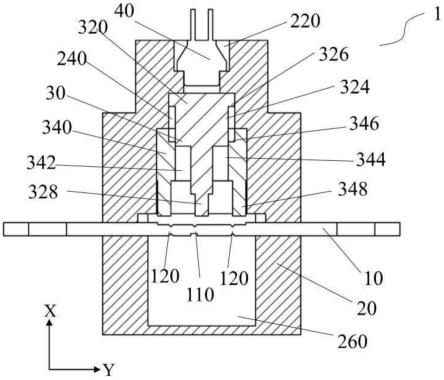

1.一种半导体器件,包括:第一纳米结构;第二纳米结构;栅极电介质层,其环绕所述第一纳米结构和所述第二纳米结构;无钨功函数调整层,其环绕所述栅极电介质层;含钨功函数调整层,其环绕所述无钨功函数调整层,所述第一纳米结构和所述第二纳米结构之间的区域被所述含钨功函数调整层、所述无钨功函数调整层和所述栅极电介质层的相应部分完全填充;以及填充层,其位于所述含钨功函数调整层上。2.根据权利要求1所述的半导体器件,其中,所述含钨功函数调整层的第一材料的电阻率低于所述无钨功函数调整层的第二材料的电阻率。3.根据权利要求1所述的半导体器件,其中,所述含钨功函数调整层包括无氟钨。4.根据权利要求1所述的半导体器件,其中,所述含钨功函数调整层包括氮化钨、碳化钨或碳氮化钨。5.根据权利要求1所述的半导体器件,其中,所述含钨功函数调整层是含钨材料的单个连续层。6.根据权利要求1所述的半导体器件,其中,所述含钨功函数调整层包括:第一含钨材料的第一层,其环绕所述无钨功函数调整层;以及第二含钨材料的第二层,其环绕所述第一含钨材料的第一层,所述第二含钨材料不同于所述第一含钨材料。7.根据权利要求6所述的半导体器件,其中,所述含钨功函数调整层还包括:所述第一含钨材料的第三层,其环绕所述第二含钨材料的第二层。8.一种半导体器件,包括:p型晶体管,该p型晶体管包括:第一沟道区域;第一栅极电介质层,其位于所述第一沟道区域上;含钨功函数调整层,其位于所述第一栅极电介质层上;以及第一填充层,其位于所述含钨功函数调整层上;以及n型晶体管,该n型晶体管包括:第二沟道区域;第二栅极电介质层,其位于所述第二沟道区域上;无钨功函数调整层,其位于所述第二栅极电介质层上;以及第二填充层,其位于所述无钨功函数调整层上。9.根据权利要求8所述的半导体器件,其中,在所述第一沟道区域和所述含钨功函数调整层之间未设置含钨层。10.一种用于制造半导体器件的方法,包括:形成具有环绕第一纳米结构的第一部分的栅极电介质层;在所述栅极电介质层的所述第一部分上沉积第一无钨功函数材料;在所述第一无钨功函数材料上沉积含钨功函数材料,所述含钨功函数材料的电阻率低

于所述第一无钨功函数材料的电阻率;以及在所述含钨功函数材料上沉积填充层。

技术总结

本公开涉及半导体器件及其制造方法。在一个实施例中,一种器件包括:p型晶体管,该p型晶体管包括:第一沟道区域;第一栅极电介质层,其位于第一沟道区域上;含钨功函数调整层,其位于第一栅极电介质层上;以及第一填充层,其位于含钨功函数调整层上;以及n型晶体管,该n型晶体管包括:第二沟道区域;第二栅极电介质层,其位于第二沟道区域上;无钨功函数调整层,其位于第二栅极电介质层上;以及第二填充层,其位于无钨功函数调整层上。位于无钨功函数调整层上。位于无钨功函数调整层上。

技术研发人员:李欣怡 张文 徐志安

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:2021.05.20

技术公布日:2022/6/7

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。