技术特征:

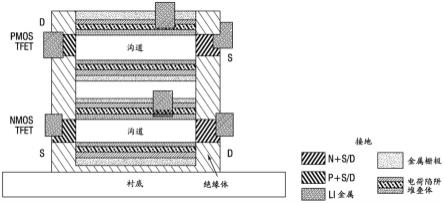

1.一种半导体器件,包括:形成在衬底上的隧穿场效应晶体管(tfet)堆叠体,该堆叠体垂直于该衬底的表面延伸,该tfet堆叠体中的每个tfet包括一个纳米沟道,该纳米沟道将每个tfet的第一侧的一个源极/漏极区与每个tfet的相反侧的另一个源极/漏极区相连接,其中,在该纳米沟道周围形成至少一个电介质层,该至少一个电介质层形成电荷俘获层。2.根据权利要求1所述的半导体器件,其中,该至少一个电介质层包括形成在该纳米沟道周围的第一氧化物层、形成在该第一氧化物层周围的高介电常数(k)电介质层、以及形成在该高k电介质层周围的第二氧化物层。3.根据权利要求1所述的半导体器件,其中,该至少一个电介质层包括形成在该纳米沟道周围的第一氧化物层、以及形成在该第一氧化物层周围的高介电常数(k)电介质层。4.根据权利要求1所述的半导体器件,其中,该至少一个电介质层包括形成在该纳米沟道周围的高介电常数(k)电介质层。5.根据权利要求1所述的半导体器件,进一步包括在与该衬底的表面垂直的方向上形成在两个相邻tfet之间的金属栅极电极堆叠体,该金属栅极电极堆叠体将该tfet的该一个源极/漏极区与该tfet的相反侧的该另一个源极/漏极区相连接。6.根据权利要求5所述的半导体器件,其中,该金属栅极电极堆叠体包括tin层、tan层、tion层和tic层。7.根据权利要求1所述的半导体器件,其中,该纳米沟道包括si或sige。8.根据权利要求2所述的半导体器件,其中,该至少一个电介质层的厚度的最小值0.9nm并且最大值为3.5nm。9.根据权利要求2所述的半导体器件,其中,该高k电介质层是hfo2。10.根据权利要求3所述的半导体器件,其中,该高k电介质层是hfo2。11.根据权利要求4所述的半导体器件,其中,该高k电介质层是hfo2。12.一种半导体电荷陷阱隧穿场效应晶体管(tfet)器件,包括:形成在衬底上的n型金属氧化物半导体tfet(nmos

·

tfet)器件,该nmos

·

tfet器件包括将该nmos

·

tfet器件的源极/漏极区相连接的一个纳米沟道,其中,在该纳米沟道周围形成至少一个电介质层,该至少一个电介质层形成电荷俘获层;以及p型金属氧化物半导体tfet(pmos tfet)器件,其形成在该衬底上并且位于该nmos tfet器件正上方,其中,至少一个间隔物将该nmos tfet器件与该pmos tfet器件隔开,该pmos tfet器件包括将该pmos tfet器件的源极/漏极区相连接的一个纳米沟道,其中,在该纳米沟道周围形成至少一个电介质层,该至少一个电介质层形成电荷俘获层,其中,该pmos tfet的漏极区连接到该nmos tfet的源极区,并且分别为该nmos tfet和该pmos tfet的源极区和漏极区、以及该nmos tfet和该pmos tfet的栅极电极提供金属连接。

tfet的漏极与该pmos tfet的源极相连接以提供输出电压,并且该nmos tfet的源极连接到正电源电压vdd,从而构成反相器器件。20.根据权利要求17所述的半导体器件,其中,该至少一个电介质层包括形成在该纳米沟道周围的高介电常数(k)电介质层。

技术总结

一种电荷陷阱隧穿场效应晶体管(TFET)包括限定电荷俘获层的多个电介质材料层。p掺杂源极/漏极区和n掺杂源极区经由纳米沟道进行连接,该纳米沟道形成在该多个电介质层之间,从而形成电荷陷阱TFET。从而形成电荷陷阱TFET。从而形成电荷陷阱TFET。

技术研发人员:马克

受保护的技术使用者:东京毅力科创株式会社

技术研发日:2020.08.21

技术公布日:2022/6/4

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。