1.本技术涉及通信技术领域,尤其涉及一种码块识别方法及装置。

背景技术:

2.一般的,发送端获取到客户信号之后,会将该客户信号以码块的形式发送出去。示例性的,该客户信号会以开始码块、数据码块以及结束码块的形式(也可以称为码块流)被发送出去。

3.接收端接收到该码块流之后,如果想要从该码块流中获取到客户信号,就需要从该码块流中识别出开始码块。

4.因此,如何识别s码块亟待解决。

技术实现要素:

5.本技术提供一种码块识别方法及装置,可以有效改善由于偶发误码导致开始码块无法被识别的情况,提高了系统的容错性。

6.第一方面,本技术实施例提供一种码块识别方法,所述方法包括:获取码块流,所述码块流中包括第一码块;确定待识别比特图样,所述待识别比特图样包括第一比特图样,所述第一比特图样为所述第一码块对应的比特图样;对比所述待识别比特图样与模板比特图样,获得不一致的比特数,所述模板比特图样包括第一模板比特图样,所述第一模板比特图样为第一边界码块对应的模板比特图样;在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块。

7.本技术实施例中,第一比特图样与第一模板比特图样对应,即第一比特图样在待识别比特图样中的位置对应于第一模板比特图样在模板比特图样中的位置。或者,也可以理解为:第一模板比特图样用于识别第一比特图样。同时,第一比特图样中的比特位置与第一模板比特图样中的比特位置对应。示例性的,第一比特图样中的第0个比特对应于第一模板比特图样中的第0个比特,第一比特图样中的第1个比特对应于第一模板比特图样中的第1个比特,第一比特图样中的第2个比特对应于第一模板比特图样中的第2个比特,以此类推。可理解,对于第一比特图样与第一模板比特图样的说明,同样适用于本技术示出的第二比特图样与第二模板比特图样,第三比特图样与第三模板比特图样,下文不再详述。

8.本技术实施例提供的方法,可以有效改善第一码块与第一边界码块(如s码块)不一致的比特数不为0比特时,确定第一码块不为第一边界码块的情况。从而,改善了由于偶发误码导致第一码块无法被识别为第一边界码块的情况,提高了系统的容错性。

9.在一种可能的实现方式中,所述第一码块为p1 b/p2 b码块,所述p1为所述第一码块的净荷比特数,所述p2为所述第一码块的总比特数,p2-p1表示所述第一码块的同步头比特数,所述p1和所述p2分别为正整数,且所述p2大于所述p1。

10.在一种可能的实现方式中,所述第一比特图样包括所述第一码块的第0个比特至第9个比特构成的图样,所述第一码块的起始比特为所述第0个比特。

11.本技术实施例中,通过获取第一码块的第0个比特至第9个比特,识别该第一码块是否为第一边界码块,不仅实施方便简单,而且还能够保证第一码块被识别为第一边界码块的可靠性。

12.当然,本技术实施例中,第一比特图样还可以包括第一码块的第0个比特至第65个比特构成的图样等,本技术实施例对于第一比特图样的具体结构不作限定。

13.在一种可能的实现方式中,所述第一码块的第0个比特和所述第一码块的第1个比特为所述第一码块的同步头,所述第一码块的第2个比特至所述第一码块的第9个比特为所述第一码块的控制块类型域。

14.可理解,第一码块的第2个比特至第9个比特还可能为该第一码块的数据字节。示例性的,当第一码块就不是第一边界码块,而是数据码块时,该第2个比特至第9个比特就是数据码块的第一个数据字节。

15.在一种可能的实现方式中,所述在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:

16.在所述待识别比特图样与所述模板比特图样有不一致的比特,且所述不一致的比特数小于或等于所述第一阈值的情况下,识别所述第一码块是所述第一边界码块。

17.也就是说,本技术实施例中,待识别比特图样与模板比特图样的不一致的比特数大于或等于1,且该不一致的比特数小于或等于第一阈值的情况下,通信装置仍可以识别第一码块是第一边界码块。

18.在一种可能的实现方式中,在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:在所述第一比特图样与所述第一模板比特图样不一致,且所述不一致的比特数小于或等于所述第一阈值的情况下,识别所述第一码块是所述第一边界码块。

19.一般的,第一码块的同步头为0b10,控制块类型域为0x78时,该第一码块才是第一边界码块。然而,本技术实施例中,即使第一码块的同步头不为0b10,和/或,第一码块的控制块类型域不为0x78,但是不一致的比特数小于或等于第一阈值的情况下,该第一码块仍可以被识别为第一边界码块。

20.在一种可能的实现方式中,所述码块流还包括第二码块,所述待识别比特图样还包括第二比特图样,所述第二比特图样为所述第二码块对应的比特图样;所述模板比特图样还包括第二模板比特图样,所述第二模板比特图样与所述第二比特图样对应。

21.在一种可能的实现方式中,所述第二模板比特图样为以下任一项码块对应的模板比特图样:第二边界码块、空闲码块、序列码块、信号码块、错误码块。

22.本技术实施例中,第二码块可以为第一码块之前的码块。示例性的,该第二码块可以为与第一码块相邻的,且位于第一码块之前的码块。

23.在一种可能的实现方式中,所述第二比特图样包括所述第二码块的第0个比特至第9个比特构成的图样,所述第二码块的起始比特为所述第0个比特。

24.本技术实施例中,第二码块的第0个比特和第1个比特可以为该第二码块的同步头。该第二码块的第2个比特至第9个比特可以为该第二码块的控制块类型域。

25.在一种可能的实现方式中,所述码块流还包括第三码块,所述待识别比特图样还包括第三比特图样,所述第三比特图样为所述第三码块对应的比特图样;所述模板比特图

样还包括第三模板比特图样,所述第三模板比特图样与所述第三比特图样对应。

26.在一种可能的实现方式中,所述第三模板比特图样为数据码块对应的模板比特图样。

27.本技术实施例中,第三码块可以为第一码块之后的码块。示例性的,该第三码块可以为与第一码块相邻的,且位于第一码块之后的码块。

28.在一种可能的实现方式中,所述在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:在所述第一比特图样与所述第一模板比特图样一致,且所述不一致的比特数小于或等于所述第一阈值的情况下,识别所述第一码块是所述第一边界码块。

29.在一种可能的实现方式中,所述在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:确定第二比特图样,所述第二比特图样为第二码块对应的比特图样;对比所述第二比特图样与第二模板比特图样;在所述不一致的比特数小于或等于所述第一阈值,且所述第二比特图样与所述第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别所述第一码块是所述第一边界码块。

30.本技术实施例中,在待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,以及在该第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,通信装置可以识别第一码块是第一边界码块。

31.示例性的,通信装置可以对比待识别比特图样和模板比特图样,如对比第一比特图样与第一模板比特图样,获得该第一比特图样与第一模板比特图样不一致的比特数。以及该通信装置还可以对比第二比特图样与第二模板比特图样,获得该第二比特图样与第二模板比特图样不一致的比特数。在第一比特图样与第一模板比特图样不一致的比特数小于或等于第一阈值的情况下,以及在第二比特图样与第二模板比特图样不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。例如,通信装置可以先对待识别比特图样(如第一比特图样)与模板比特图样(如第一模板比特图样)进行对比,当待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,该通信装置再对第二比特图样与第二模板比特图样进行对比。从而,在第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。

32.这里所示的实施例中,第二比特图样与第二模板比特图样的不一致的比特数不包含于上述第一阈值中。

33.示例性的,第二阈值可以为0或1等,本技术实施例对此不作限定。

34.在一种可能的实现方式中,所述在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:确定第二比特图样,所述第二比特图样为第二码块对应的比特图样;对比所述第二比特图样与第二模板比特图样;在所述不一致的比特数小于或等于第一阈值,且所述第二比特图样与所述第二模板比特图样一致的情况下,识别所述第一码块是所述第一边界码块。

35.本技术实施例中,通过判断该第二比特图样是否为控制码块,进一步确认第一码块是否为第一边界码块,从而进一步提高了第一码块被识别为第一边界码块的准确性和可靠性,保证了系统的容错性。可理解,关于第二比特图样与第二模板比特图样的说明,可以参考上述关于第二阈值对应的实施例的说明,这里不再详述。

36.在一种可能的实现方式中,所述在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是所述第一边界码块,包括:确定第三比特图样,所述第三比特图样为第三码块对应的比特图样;对比所述第三比特图样与第三模板比特图样;在所述不一致的比特数小于或等于所述第一阈值,且所述第三比特图样与所述第三模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别所述第一码块是所述第一边界码块。

37.可理解,对于第三码块的说明可以参考上述对第二码块的说明,这里不再详述。示例性的,第三码块可以是数据码块。

38.在一种可能的实现方式中,所述识别所述第一码块是所述第一边界码块之后,所述方法还包括:根据所述第一码块从所述码块流中确定第一码组,所述第一码组以所述第一码块开始。

39.在一种可能的实现方式中,所述第一码组包括195个数据码块和一个结束码块。

40.本技术实施例中,通过对s码块的识别,使得通信装置能够解复用出以s码块为开始的码组对应的多个第一时隙,从而获得该多个第一时隙对应的客户信号,不仅实施简单,而且还能够有效保证码组被识别的可靠性。

41.在一种可能的实现方式中,所述第一码组承载t个客户信号,所述t为正整数。

42.本技术实施例中,第一码组可以承载t个客户信号。然而,在具体实现中,该第一码组也可能没有承载客户信号等,本技术实施例对此不作限定。

43.在一种可能的实现方式中,t=24。

44.第二方面,本技术提供一种通信装置,用于执行第一方面或第一方面的任意可能的实现方式中的方法。该通信装置包括具有执行第一方面或第一方面的任意可能的实现方式中的方法的相应单元。

45.例如,该通信装置可以包括收发单元和处理单元。

46.第三方面,本技术提供一种通信装置,该通信装置包括处理器,用于执行上述第一方面或第一方面的任意可能的实现方式所示的方法。

47.在执行上述方法的过程中,上述方法中有关接收码块(或码块流)等的过程,可以理解为由处理器接收输入的码块(或码块流)的过程。处理器接收输入的码块(或码块流)时,收发器接收码块(或码块流),并将其输入处理器。更进一步的,在收发器收到该码块(或码块流)之后,该码块(或码块流)可能需要进行其他的处理,然后才输入处理器。

48.对于处理器所涉及的发射、发送和接收等操作,如果没有特殊说明,或者,如果未与其在相关描述中的实际作用或者内在逻辑相抵触,则均可以更加一般性的理解为处理器输出和接收、输入等操作,而不是直接由射频电路和天线所进行的发射、发送和接收操作。

49.在实现过程中,上述处理器可以是专门用于执行这些方法的处理器,也可以是执行存储器中的计算机指令来执行这些方法的处理器,例如通用处理器。上述存储器可以为非瞬时性(non-transitory)存储器,例如只读存储器(read only memory,rom),其可以与处理器集成在同一块芯片上,也可以分别设置在不同的芯片上,本技术实施例对存储器的类型以及存储器与处理器的设置方式不做限定。

50.在一种可能的实现方式中,存储器位于所述通信装置之外。

51.在一种可能的实现方式中,存储器位于所述通信装置之内。

52.本技术实施例中,处理器和存储器还可能集成于一个器件中,即处理器和存储器

还可以被集成在一起。

53.在一种可能的实现方式中,所述通信装置还包括收发器,所述收发器,用于接收信号和/或发送信号。

54.示例性的,该收发器可以用于接收码块流等。

55.第四方面,本技术提供一种通信装置,所述通信装置包括逻辑电路和接口,所述逻辑电路和所述接口耦合;其中,所述接口,用于获取码块流(或者,也可以称为输入码块流),所述逻辑电路,用于确定待识别比特图样,以及对比所述待识别比特图样和模板比特图样,获得不一致的比特数;在所述不一致的比特数小于或等于第一阈值的情况下,识别所述第一码块是第一边界码块。

56.可理解,对于逻辑电路的具体实现方式,还可以参考下文示出的装置实施例等,这里不再详述。对于第一码块、待识别比特图样、模板比特图样等的说明,可以参考本技术的其他实施例等,这里不作详述。

57.第五方面,本技术提供一种计算机可读存储介质,该计算机可读存储介质用于存储计算机程序,当其在计算机上运行时,使得上述第一方面或第一方面的任意可能的实现方式所示的方法被执行。

58.示例性的,当上述计算机程序在通信装置(如接收端)上运行时,上述第一方面或第一方面的任意可能的实现方式所示的方法被执行。

59.第六方面,本技术提供一种计算机程序产品,该计算机程序产品包括计算机程序或计算机代码,当其在计算机上运行时,使得上述第一方面或第一方面的任意可能的实现方式所示的方法被执行。

60.第七方面,本技术提供一种计算机程序,该计算机程序在计算机上运行时,上述第一方面或第一方面的任意可能的实现方式所示的方法被执行。

附图说明

61.图1是本技术实施例提供的一种基于灵活以太网协议的通信系统示意图;

62.图2是本技术实施例提供的一种mtn网络架构示意图;

63.图3是本技术实施例提供的另一种mtn网络架构示意图;

64.图4是本技术实施例提供的一种第一通道和第二通道的关系示意图;

65.图5a是本技术实施例提供的一种64b/66b码块的不同码型定义;

66.图5b和图5c是本技术实施例提供的一种码组的结构示意图;

67.图5d是本技术实施例提供的一种码组的封装过程示意图;

68.图6a和图6b是本技术实施例提供的一种模板比特图样示意图;

69.图7a至图7c是本技术实施例提供的一种模板比特图样示意图;

70.图8a是本技术实施例提供的一种模板比特图样与待识别比特图样的对比示意图;

71.图8b是本技术实施例提供的一种模板比特图样的结构示意图;

72.图8c是本技术实施例提供的一种待识别比特图样的结构示意图;

73.图9是本技术实施例提供的一种码块识别方法的流程示意图;

74.图10a是本技术实施例提供的一种码块识别方法的流程示意图;

75.图10b是本技术实施例提供的一种识别s码块的模块示意图;

76.图11是本技术实施例提供的一种码块识别方法的流程示意图;

77.图12a和图12b是本技术实施例提供的另一种码块识别方法的流程示意图;

78.图13和图14是本技术实施例提供的又一种码块识别方法的流程示意图;

79.图15至图17是本技术实施例提供的一种通信装置的结构示意图。

具体实施方式

80.为了使本技术的目的、技术方案和优点更加清楚,下面将结合附图对本技术作进一步地描述。

81.本技术的说明书、权利要求书及附图中的术语“第一”和“第二”等仅用于区别不同对象,而不是用于描述特定顺序。此外,术语“包括”和“具有”以及它们的任何变形,意图在于覆盖不排他的包含。例如包含了一系列步骤或单元的过程、方法、系统、产品或设备等,没有限定于已列出的步骤或单元,而是可选地还包括没有列出的步骤或单元等,或可选地还包括对于这些过程、方法、产品或设备等固有的其它步骤或单元。

82.在本文中提及的“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本技术的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员可以显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

83.在本技术中,“至少一个(项)”是指一个或者多个,“多个”是指两个或两个以上,“至少两个(项)”是指两个或三个及三个以上,“和/或”,用于描述关联对象的关联关系,表示可以存在三种关系,例如,“a和/或b”可以表示:只存在a,只存在b以及同时存在a和b三种情况,其中a,b可以是单数或者复数。字符“/”一般表示前后关联对象是一种“或”的关系。“以下至少一项(个)”或其类似表达,是指这些项中的任意组合。例如,a,b或c中的至少一项(个),可以表示:a,b,c,“a和b”,“a和c”,“b和c”,或“a和b和c”。

84.以下详细介绍本技术涉及的术语。

85.1、灵活以太网(flexible ethernet,flexe)

86.光互联网论坛(optical internet forum,oif)发布了灵活以太网(flexible ethernet,flexe),flexe是一种支持不同以太网媒体访问控制(media access contro,mac)层速率的通用技术。flexe引入了灵活以太网捆绑组(也可称为flexegroup或简称为捆绑组)的概念。捆绑组可以由一个或多个物理层装置(也可以认为物理链路接口,可记为phy)捆绑组成,一个捆绑组对应的带宽资源为该捆绑组中的phy对应的带宽资源之和,因此,基于捆绑组,flexe能够满足更大的传输速率和传输带宽。

87.图1示例性示出了一种基于灵活以太网协议的通信系统示意图,图1是以一个捆绑组包括4个phy为例。flexe通过时分复用(time division multiplexing,tdm)方式将每个phy的带宽资源划分为多个时隙,实现传输管道带宽的硬隔离。灵活以太网协议客户(flexe client)代表在捆绑组上指定的时隙(一个时隙或多个时隙)传输业务流,一个捆绑组上可承载多个灵活以太网协议客户,一个灵活以太网协议客户对应一个业务流(典型的,可以称为媒体访问控制(medium access control,mac)client),灵活以太网协议功能层(也可以称为flexeshim)层提供灵活以太网协议客户到mac client的数据适配和转换。

88.flexe通过将多个phy绑定可支持例如绑定、子速率、通道化等功能。示例性的,

flexe可以将多个100比特以太网(gigabit ethernet,ge)phy端口绑定,将每个100ge端口在时域上以5g为颗粒划分为20个时隙,flexe可支持不同以太网mac速率的业务。例如在2

×

100ge捆绑组中支持200g的mac业务,也就是flexe将多个以太网端口绑定为一个捆绑组(group)以支持速率大于单个以太网端口的mac业务,即flexe支持绑定功能。又例如支持在100ge捆绑组中传输50g的mac业务,也就是通过为业务分配时隙支持速率小于捆绑组带宽或者小于单个以太网端口带宽的mac业务,即flexe支持子速率功能。又例如在2

×

100ge捆绑组中支持同时传输一个150g和两个25g的mac业务,也就是通过为业务分配时隙支持在捆绑组中同时传输多个mac业务,即flexe支持通道化功能。

89.可见,flexe通过捆绑组可以并行地传输多个业务流,同一业务流的业务数据可以承载在捆绑组中的一个phy,也可以承载在捆绑组中的不同phy。换句话说,同一业务流的业务数据可以通过捆绑组中的一个phy传输至对端,也可以通过捆绑组中的多个phy传输至对端。一个phy的带宽资源通常会被划分为多个时隙,实际使用时,可以将业务所对应的码块流按照时隙配置表分配到相应时隙上。可理解,这里所示一个phy的带宽资源通常会被划分为多个时隙,该时隙可以理解为第二时隙。

90.可理解,本技术示出的捆绑组还可以称为链路组等,以及本技术示出的业务流也可以称为数据流等,本技术对其名称不作限定。可理解,这里所示的业务流也可以理解为下文示出的客户信号等。

91.2、城域传输网络(metro transport network,mtn)

92.mtn是国际电信联盟(telecommunication standardization sector of itu,itu-t)针对5g等新业务需求在沿用flexe设计逻辑的基础上定义了的新一代传送网技术体系。示例性的,如图2所示,mtn可以包括mtn通道层(mtn path layer)和mtn段层(mtn sectionlayer)。其中,mtn通道层包括mtn通道适配层(mtn path adaptation)、mtn通道终结层(mtn path trail termination)、mtn通道连接层(mtn path connection)等。mtn段层包括mtn段层适配层(mtn section adaptation)和mtn段层终结层(mtn section trail termination)。可选的,mtn段层还可以包括适配层(adaptation)。

93.可理解,上述mtn通道适配层、mtn通道终结层、mtn通道连接层或mtn段层终结层等,还可能存在其他名称,例如,mtn通道适配层还可以称为mtn通道适配功能模块等,本技术对此不作限定。可理解,对于mtn中关于捆绑组的描述,可参考关于flexe中关于捆绑组的描述,这里不再详述。

94.示例性的,发送端获取到的业务流可以经过mac,进入mtn域mtn通道适配层适配成64b/66b码块流的形式,该64b/66b码块流进入mtn通道终结层后,64b/66b码块流中会被插入通道层操作管理和维护(operations,administration,and maintenance,oam)信息,该oam信息中包括比特交织奇偶校验(bit interleavedparity,bip)结果。接着,发送端可以通过mtn通道连接层(mtn path connection)进行通道转发,即在该mtn通道连接层确定出入端口的对应关系,从而确定出端口。mtn段层适配层(mtn section adaptation)是通道层到段层的适配功能,在该mtn段层适配层各路mac的业务流(如64b/66b码块的形式)会进行交织,形成一路64b/66b码块流。然后,该一路64b/66b码块流经过mtn段层终结层(mtn section trail termination)、适配层(adaptation)等进入物理层进行传输等。示例性的,该64b/66b码块流还可以经过扰码、通道分布、对齐标记(alignment marker,am)插入功能

等。

95.相反,接收端接收到64b/66b码块流后,接收端接收的64b/66b码块流的流向与发送端发送64b/66b码块流的流向相反。例如接收端接收到的64b/66b码块流可以依次经过例如mtn段层、mtn通道层等。

96.从协议栈的角度粗略地看,mtn的段层从功能上来讲与oif flexe shim类似。mtn段层当前版本重用兼容flexe,mtn当前版本的段层帧格式保留了flexe帧格式。可理解,对于mac、协调子层(reconciliation sublayer,rs)、物理编码子层编码/反编码(pcs encode/decode)等的具体描述,可参考ieee802.3的以太网模型。

97.3、mtn灵活颗粒(finer granularity,fg)层

98.如图3中的客户信号(client)经过mtn fg适配层后形成码组流。该码组流经过mtn fg终结层时,该码组流可以被插入oam信息等(或者也可以理解为被插入开销信息)。然后,发送端在mtn fg连接层确定出入端口的对应关系,从而确定出端口。示例性的,在mtn fg层,如mtn fg终结层,码组流可以在第一通道中被传输;然后在mtn通道层,如mtn通道适配层,一路或多路第一通道可以复用第二通道划分出的一个或多个第一时隙。在mtn通道终结层,一路第二通道中可以被插入oam等开销信息,以及在mtn段层适配层,一路或多路第二通道复用捆绑组划分出的一个或多个第二时隙。即在mtn段层,一路第二通道可以映射至一个或多个第二时隙。可理解,对于mtn通道层和mtn段层的具体描述可以参考图2,这里不再详述。

99.本技术中,由于码组是以码块的形式封装的,因此,在码组流经过mtn通道层和mtn段层时,mtn通道层和mtn段层感知到的就是码块流,随后,码块流经过物理层,被发送到链路上。

100.接收端在接收到码块流后,可以mtn段层适配层从捆绑组中的一个或多个第二时隙中解复用出第二通道。以及mtn通道适配层从第二通道中的一个或多个第一时隙中解复用出第一通道。由此接收端可以在mtn fg层从第一通道中恢复出客户信号流。可理解,由于接收端获取到客户信号流的流向与发送端发送客户信号流的流向相反,因此对于接收端获取到客户信号流的具体方式,还可以发送端发送码块流的描述,这里不再详述。

101.4、第一时隙

102.由上文可知,切片分组网(slicing packet network,spn)或mtn等提供了基于n

×

5gbps带宽的硬管道,n为正整数。然而,对于某些业务来说,5gbps的管道带宽粒度依旧过大。为了解决管道带宽粒度过大的问题,本技术还提供了一种小颗粒管道。如图4所示,在5gbps管道的基础上,本技术提供的方法可以对该5gbps进行进一步的时隙化切分,如将5gbps的时隙切分为480个10mbps。该情况下,一个10mbps可以对应一个客户信号,或者,多个10mbps可以对应一个客户信号等,本技术对此不作限定。这里所示的5gbps还可以理解为第二时隙。换句话说,第二时隙可以被划分为多个第一时隙。如上所示,第二时隙可以被划分为480个第一时隙。可理解,该第一时隙不仅可以包括10mbps,还可以包括100mbps、7.5mbps、5mbps或2.5mbps等,以及第二时隙不仅包括5gbps,还可以包括10gbps、25gbps等,本技术对此不作限定。可理解,本技术示出的各个时隙的带宽,在具体实现中,可能还会存在偏差,因此,对于第一时隙或第二时隙的带宽的具体取值,本技术不作限定。示例性的,第一时隙的带宽为10mbps时,在具体实现中,该第一时隙的带宽还可以为10.1mbps或

10.2mbps等。

103.以下将对本技术示出的捆绑组、第一时隙以及第二时隙进行详细说明。

104.本技术中捆绑组可以由一个或多个phy捆绑而成,且该捆绑组的带宽为该一个或多个phy的带宽之和。进一步的,该捆绑组可以被划分为x个第二时隙。第二通道可以包括该x个第二隙中的n个第二时隙,且该第二通道可以被划分为y个第一时隙。第一通道可以包括该y个第一时隙中的m个第一时隙。其中,n小于或等于x,m小于或等于y,且m、n、x和y均为大于或等于1的整数。

105.换句话说,本技术中,第一通道包括m个第一时隙,该m个第一时隙包含于第二通道中,该第二通道包括n个第二时隙,该n个第二时隙包含于捆绑组中,该捆绑组中包括一个或多个phy链路。其中,第二通道被划分为y个第一时隙,上述m个第一时隙包含于该y个第一时隙中,捆绑组被划分为x个第二时隙,上述n个第二时隙包含于该x个第二时隙中。可选的,本技术中的第一时隙的带宽可以为10mbps

×

k,该k为大于或等于1的整数,且k小于或等于2048。

106.上述第一通道可以理解为用于传输码组的通道,上述第二通道可以理解为用于传输码块的通道。第一通道在传输码组时,可以复用第二通道被划分出的y个第一时隙中的m个第一时隙。换句话说,本技术示出的第一通道的时隙粒度更小,该传送网络技术相较于mtn的时隙粒度更小,更灵活。例如,该第一通道可以用于传输专线业务等。又例如,该第一通道可以用于传输一个或多个不同的客户信号等。可理解,该第一通道可以用于传输本技术示出的码组(如第一码组等),该码组可以被透传于mtn网络。

107.示例性的,如图4所示,捆绑组中的一个phy可以包括三个第二通道,该第二通道中包括的第二时隙包含于捆绑组中。其中一个第二通道可以包括三个第一通道,如第一通道中包括的m个第一时隙包含于第二通道中。可理解,图4仅为示例,不应将其理解为对本技术的限定。

108.本技术中,第一通道还可以称为fgbu通道(或mtn fg通道)、灵活小颗粒通道(或小颗粒通道)或低阶通道等,第二通道还可以称为大颗粒通道或高阶通道等,本技术对其名称不作限定。

109.5、码块(block)

110.p1 b/p2 b码块:一种编码方式,也可以称为p1 b/p2 b比特块(bit block),或者也可以称为p1 b/p2 b块,或者也可以称为p1 b/p2 b编码块,或者也可以称为p1 b/p2 b比特流,或者也可以称为p1/p2(或p1 b/p2 b)比特块等。其中,p1表示码块(或比特块)中的净荷比特数;p2表示码块的总比特数,p2-p1表示码块中的同步头比特数,p1、p2为正整数,且p2大于p1。示例性的,上述p1 b/p2 b码块可以为8b/10b码块、64b/66b码块、128b/130b码块或256b/258b码块等,本技术对上述p1和p2的具体取值不作限定。

111.下文将以64b/66b码块为例示出本技术提供的方法。可理解,下文示出的64b/66b码块也可以替换为64b/66b比特块,或者64/66码块,或者64/66比特块,或者64b/66b码块,或者64b/66b比特块,或者64b/66b比特块流,或者64b/66b编码块等。

112.作为示例,图5a示出的是一种64b/66b码块的不同码型定义。如图5a所示,首部的2个比特“10”或“01”为同步头比特,后64比特即为净荷比特,可以用于承载净荷数据等。图5a中每一行代表一种码型定义,其中,d0~d7代表数据字节,c0~c7代表控制字节,s0代表mac

帧的开始,t0~t7代表mac帧的结束。

113.图5a示出的不同码块中,当同步头比特为0b10时,对应的码块可以称为控制码块。控制码块即为上述p1 b/p2 b码块中定义的控制码型。示例性的,控制码块的同步头可以为“10”,以及该控制码块还可以包括控制块类型域(controlblock type field)。

114.例如,64b/66b中定义的控制码块的控制块类型域为0x78时,该控制码块可以为开始码块。

115.又例如,64b/66b中定义的控制码块的控制块类型域为0xff时,该控制码块可以为结束码块。可理解,这里仅示例性的示出了一种结束码块,在图5a示出的码块中结束码块的控制块类型域还可以为0x87、0x99等,这里不再详述。本技术下文示出的第二边界码块的控制块类型域不仅可以为0xff,还可以为0x87、0x99、0xaa、0xb4、0xcc、0xd2或0xe1等,本技术对于第二边界码块的控制块类型域不作限定。

116.又例如,64b/66b中定义的控制码块的控制块类型域为0x4b时,该控制码块可以为序列(sequenceordered set,o)码块,或者也可以称为信号(signal ordered set,o)码块等。示例性的,该序列码块可以表示链路状态,该信号码块可以表示特殊信号的信息。本技术对于该序列码块和该信号码块的区别不作限定。下文将以o码块表示该序列码块或该信号码块。

117.又例如,64b/66b中定义的控制码块的控制块类型域为0x1e时,该控制码块可以为空闲(idle)码块或错误(error)码块。至于该控制码块具体为空闲码块还是错误码块,可以根据控制块类型域之后的第一个控制字节的取值确定。例如,当第一个控制字节为0xie时,该控制码块为错误码块;当第一个控制字节为0x00时,该控制码块可以为空闲码块。

118.6、边界码块

119.边界码块可以用于标识数据码块的开始或结束。本技术中,边界码块可以包括第一边界码块和/或第二边界码块。

120.一般的,报文中的前导(preamble)和/或帧起始定界符(startofframedelimiter,sfd)可以被编码为开始码块。以及为标识报文的结束,在编码时可能会在最后一个数据码块之后增加一个结束码块(或者,结束码块中也可以用于承载数据等)。即这里所示的开始码块和结束码块可以用于界定至少一个数据码块。示例性的,开始码块和结束码块可以用于界定195个数据码块。或者,开始码块和结束码块可以用于界定33个数据码块等。这里所示的开始码块和结束码块的描述仅为示例。例如,第一边界码块可以为第一码组的开始码块,至于该第一码组的结束码块可以为第三边界码块(即结束码块)。又例如,第二边界码块可以为第二码组的结束码块,该第二码组的开始码块可以为第四边界码块等,本技术对于第二码组的开始码块不作限定。

121.示例性的,下文示出的客户信号可以是报文的形式。例如,下文示出的mac帧(即mac frame)流也可以称为报文流等,本技术对此不作限定。

122.7、码组(block group)

123.以下将示例性说明本技术示出的码组的结构。

124.第一种,码组可以包括一个开始码块、一个或多个数据码块和一个结束码块。示例性的,该码组的开始部分是开始码块,结尾部分可以是结束码块,或者,结尾部分可以是其他控制码块等。

125.示例性的,图5b是本技术示出的一种码组的结构示意图。该码组可以包括一个开始码块和一个结束码块,以及33个数据码块。由于图5b示出的结束码块为0xff,因此该结束码块第0个控制字节(如图5a中的d0字节)至第6个控制字节(如图5a中的d6字节)可以用于承载数据。由此,图5b示出的负载部分可以承载33个数据码块。

126.第二种,码组可以包括一个开始码块和一个结束码块,以及还包括根据64b/66b数据码块编码得到的一个或多个64b/65b数据码块。可理解,该64b/65b数据码块包含于码组的负载(payload)部分。换句话说,码组的负载部分包括的64b/65b数据码块可以由64b/66b数据码块去掉1比特同步头获得。至于去掉64b/66b数据码块的第0个比特还是第1个比特,本技术不作限定。

127.示例性的,图5c是本技术示出的另一种码组的结构示意图。如图5c所示,第一行(即对应图5a中的开始码块)为该码组中的开始码块,第197行(即对应图5a中的结束码块)为该码组中的结束码块,第198行为该码块中位于结束码块之后的其他控制码块(图5c中未示出第198行)。第2行的前7个字节用于承载开销(overhead,oh)信息。从第2行的第8个字节开始到第196行即为64b/65b数据码块,用于承载数据信息。根据65与64之间的关系,码组的负载部分可以根据195个数据码块编码得到。图5c示出的负载部分为1560字节,1560字节=1560*8比特=192个64b/65b。同时,195个64b/66b数据码块,一共有195*64=12480比特=192*65。因此,图5c示出的码组可以理解为包括一个s码块、195个d码块以及一个t码块。

128.本技术中,码组的长度可以为预设长度,如一个码组中的数据码块的长度可以为1560个字节。

129.如图5d所示,客户信号(例如mac frame流)在经过64b/66b编码后,形成64b/66b码块流,64b/66b码块流在完成64b/65b压缩(去掉1比特的同步头)后,形成64b/65b码块流。该64b/65b码块流可以按照每8个64b/65b码块为一组映射至一个第一时隙中。

130.也就是说,本技术示出第一时隙可以包括8个64b/65b。由此,结合图5c所示的fgbu的结构,一个fgbu可以承载24个第一时隙。以及20个fgbu可以构成一个完整的复用周期,一个复用周期内可以包括480个时隙。本技术中,由于第一时隙可以用于承载一个客户信号,因此一个fgbu可以最多还可以承载24个客户信号。

131.可理解,本技术示出的码组还可以称为灵活颗粒基础单元(finer granularity basicunit,fgbu)、码块集或码块簇等,本技术对其名称不作限定。

132.可理解,这里所示的码组中包括的数据码块的长度仅为示例,在具体实现中,该码组包括的数据码块的长度还可以为其他值等。

133.可理解,本技术示出的码组的说明适用于下文示出的第一码组,该第一码组以第一码块开始,该第一码块可以为s码块。

134.8、待识别比特图样和模板比特图样

135.待识别比特图样:由一个或多个码块的部分或全部比特构成。

136.可选的,该待识别比特图样可以由第一码块的至少两个比特构成。例如,待识别比特图样包括第一比特图样,该第一比特图样为第一码块的第0个比特至第9个比特构成的比特图样。又例如,第一比特图样为第一码块的第0个比特至第65个比特构成的比特图样。

137.可选的,待识别比特图样由第一码块的至少两个比特,以及第二码块的至少两个比特构成。例如,待识别比特图样包括第一比特图样和第二比特图样,该第二比特图样可以

为第二码块的第0个比特至第9个比特构成的比特图样等。

138.可选的,待识别比特图样由第一码块的至少两个比特,以及第三码块的至少两个比特构成。例如,待识别比特图样包括第一比特图样和第三比特图样,该第三比特图样可以为第三码块的第0个比特和第1个比特构成的比特图样等。

139.可选的,待识别比特图样由第一码块的至少两个比特、第二码块的至少两个比特以及第三码块的至少两个比特构成。

140.可理解,以上示出的第一比特图样、第二比特图样以及第三比特图样仅为示例,在具体实现中,第一比特图样还可以为第一码块的第0个比特至第17个比特构成的比特图样等。或者,第二比特图样还可以为第二码块的第0个比特至第65个比特构成的比特图样等,本技术实施例对此不作限定。

141.本技术中,可以通过检测窗口获取待识别比特图样,如该检测窗口可以用于检测第一码块是否为第一边界码块。

142.模板比特图样:用于判断第一码块是否为第一边界码块时所期望出现的比特顺序。如模板比特图样可以理解为:用于判断第一码块是否为第一边界码块时,所期望检测窗口内出现的比特顺序。示例性的,模板比特图样包括第一模板比特图样,该第一模板比特图样用于识别第一比特图样。换句话说,该第一模板比特图样在模板比特图样中的位置与第一比特图样在待识别比特图样中的位置是一一对应的。对于待识别比特图样与模板比特图样的对应关系还可以参考下文示出的图8a的说明。

143.示例性的,第一模板比特图样可以为开始码块对应的模板比特图样,第二模板比特图样可以为结束码块对应的模板比特图样。该情况下,对于第一模板比特图样和第二模板比特图样的说明,可以参考下文示出的各个实施例。

144.然而,本技术中第一模板比特图样还可以为结束码块对应的模板比特图样,第二模板比特图样可以为数据码块对应的模板比特图样,第三模板比特图样可以为开始码块对应的模板比特图样。或者,第三模板比特图样还可以为空闲码块、错误码块或o码块中的任一项对应的模板比特图样等。换句话说,通信装置可以利用第一码块之前的第二码块识或该第一码块之后的第三码块来识别第一码块是否为结束码块。该情况下,第一边界码块即为结束码块。可理解,关于第一模板比特图样为结束码块对应的模板比特图样、第二模板比特图样为数据码块对应的模板比特图样,第三模板比特图样为开始码块、空闲码块、错误码块或o码块中的任一项对应的模板比特图样的具体说明,可以参考下文示出的第一模板比特图样为开始码块对应的模板比特图样,第二模板比特图样为结束码块、空闲码块、错误码块或o码块中的任一项对应的模板比特图样,第三模板比特图样为数据码块对应的模板比特图样的具体说明,下文不作详述。

145.可理解,本技术示出的比特图样(bit pattern)还可以称为比特图案、比特串(bit string)、比特序列(bit sequence)或比特位模式等,本技术对其名称不作限定。同时,本技术示出的模板比特图样(bit pattern),还可以称为预设比特图样,或预设模板,或预置模板等,本技术对其名称不作限定。以及本技术示出的待识别比特图样还可以称为待验证比特图样,或目标比特图样等,本技术对其名称也不作限定。

146.以下结合附图说明本技术示出的模板比特图样。

147.在一种可能的实现方式中,模板比特图样包括第一模板比特图样,该第一模板比

特图样可以为第一边界码块对应的模板比特图样。示例性的,该第一边界码块可以为s码块。

148.可选的,如图6a所示,该第一模板比特图样可以包括该s码块的第0个比特至第9个比特对应的模板比特图样。即第一模板比特图样由s码块的同步头和控制块类型域构成。

149.可选的,该第一模板比特图样还可以包括s码块的第0个比特至第9个比特,以及第一个控制字节(如图5a中的d1字节)至第七个控制字节(如图5a中的d7字节)中的任一个字节对应的模板比特图样。如图6b所示,该第一模板比特图样可以由s码块的第0个比特至第65个比特构成。

150.可选的,第一模板比特图样还可以包括s码块的第2个比特至第9个比特对应的模板比特图样。第一模板比特图样还可以由s码块的控制块类型域构成等。

151.在另一种可能的实现方式中,模板比特图样包括第一模板比特图样和第二模板比特图样。该第二模板比特图样可以为以下任一项码块对应的模板比特图样:第二边界码块(如t7码块)、空闲(idle)码块、序列(sequenceordered set,o)码块、信号(signal ordered set,o)码块、错误(error)码块。对于第一模板比特图样的说明可以参考图6a和图6b,这里不再详述。

152.可选的,如图7a(1)所示,模板比特图样可以包括t码块的第0个比特至第9个比特,以及s码块的第0个比特至第9个比特对应的模板比特图样。如模板比特图样可以由t码块的同步头和控制块类型域,以及s码块的同步头和控制块类型域构成。

153.可理解,第一模板比特图样还可以由s码块的同步头或控制块类型域中的任一项,以及第二模板比特图样还可以包括t码块的同步头或控制块类型域中的任一项构成等。由此,模板比特图样可以包括t码块的控制块类型域,以及s码块的同步头和控制块类型域对应的模板比特图样。或者,模板比特图样可以包括t码块的控制块类型域,以及s码块的控制块类型域对应的模板比特图样。或者,模板比特图样可以包括t码块的同步头和控制块类型域,以及s码块的控制块类型域对应的模板比特图样。或者,模板比特图样可以包括t码块的同步头,以及s码块的同步头和控制块类型域对应的模板比特图样。或者,模板比特图样可以包括t码块的同步头和s码块的同步头对应的模板比特图样。可理解,对于该说明,下文示出的其他码块同样适用,下文不再详述。

154.可选的,如图7a(2)所示,模板比特图样可以包括o码块的同步头和块类型域,以及s码块的同步头和块类型域对应的模板比特图样。

155.可选的,如图7a(3)所示,模板比特图样可以包括空闲码块的同步头和块类型域,以及s码块的同步头和块类型域对应的模板比特图样。或者,图7a(3)示出的模板比特图样还可以理解为错误码块的同步头和块类型域,以及s码块的同步头和块类型域对应的模板比特图样。

156.可理解,本技术示出的第一模板比特图样还可以由s码块的同步头、s码块的控制块类型域以及s码块的控制字节构成。如图5a所示,错误码块的第0个字节至第7个字节的取值分别为0x1e。而空闲码块的第0个字节至第7个字节的取值分别为0x00。因此本技术示出的第二模板比特图样中还可以包括错误码块或空闲码块的控制字节等。

157.在又一种可能的实现方式中,模板比特图样包括第一模板比特图样和第三模板比特图样。该第三模板比特图样可以为数据码块对应的模板比特图样。

158.可选的,模板比特图样可以包括s码块的同步头和块类型域,以及数据码块的同步头对应的模板比特图样。

159.可选的,如图7b(1)所示,模板比特图样可以包括s码块的同步头和块类型域,以及数据码块的同步头和第一个字节对应的模板比特图样。可理解,图7b示出的0x89即为图5b或图5c示出的用于承载开销信息的第一个字节的取值。该0x89还可以为其他值等,本技术实施例对此不作限定。图7b示出的0xaa可以理解为用于承载开销信息的第二个字节的取值,该0xaa还可以为其他值等,本技术实施例对此不作限定。

160.可选的,如图7b(2)所示,模板比特图样可以包括s码块的同步头和块类型域,以及数据码块的同步头、第一个字节和第二个字节对应的模板比特图样。

161.可选的,模板比特图样还可以包括s码块的同步头和块类型域,以及数据码块的同步头对应的模板比特图样。

162.在又一种可能的实现方式中,模板比特图样包括第一模板比特图样、第二模板比特图样和第三模板比特图样。

163.可理解,对于第一模板比特图样、第二模板比特图样以及第三模板比特图样的具体说明,可以参考上文,这里不再详述。

164.示例性的,如图7c(1)所示,模板比特图样包括t码块的同步头和块类型域、s码块的同步头和块类型域,以及数据码块的同步头对应的模板比特图样。

165.示例性的,如图7c(2)所示,模板比特图样包括o码块的同步头和块类型域、s码块的同步头和块类型域,以及数据码块的同步头对应的模板比特图样。

166.示例性的,如图7c(3)所示,模板比特图样包括idle码块(或error码块)的同步头和块类型域、s码块的同步头和块类型域以及数据码块的同步头对应的模板比特图样。

167.可理解,本技术示出的模板比特图样仅为示例,在具体实现中,模板比特图样还可以具有更多的表现形式,本技术对此不作限定。

168.如以图6a示出的模板比特图样为例,以下结合图8a说明模板比特图样与待识别比特图样的对比结果(即不一致的比特数)。本技术实施例是以第一码块的第0个比特至第9个比特为例,但是不应将其理解为对本技术实施例的限定。示例性的,当待识别比特图样为第一码块的第0个比特至第65个比特对应的模板比特图样时,该待识别比特图样可以与图6b示出的模板比特图样进行对比等,这里不再赘述。

169.如图8a(1)所示,当第一码块的第0个比特和第1个比特为10(即第一码块的同步头为10),以及第一码块的第2个比特至第9个比特为0x78时,通过与模板比特图样对比,可以获得不一致的比特数为0。

170.如图8a(2)所示,当第一码块的第0个比特和第1个比特为10,而第一码块的第2个比特至第9个比特为0x79时,通过与模板比特图样对比,可以获得不一致的比特数为1。

171.如图8a(3)所示,当第一码块的第0个比特和第1个比特为10,而第一码块的第2个比特至第9个比特为0x7a时,通过与模板比特图样对比,可以获得不一致的比特数为1。

172.示例性的,当第一码块的第0个比特和第1个比特为01,而第一码块的第2个比特至第9个比特为0x78时,通过与模板比特图样对比,可以获得不一致的比特数为1。

173.可理解,以上示出的模板比特图样的结构仅为示例,该模板比特图样的结构还可以为其他结构等,本技术对此不作限定。示例性的,图8b(1)示出的模板比特图样为上文示

出的结构,该情况下,待识别比特图样的结构可以如图8c(1)所示。图8b(2)示出的模板比特图样是本技术示出的另一种模板比特图样的结构。该情况下,待识别比特图样的结构可以如图8c(2)所示。

174.需要说明的是,不管模板比特图样的结构如何发生变化,只要待识别比特图样中的第一比特图样与第一模板比特图样对应,第二比特图样与第二模板比特图样对应,第三比特图样与第三模板比特图样对应,都落入本技术的保护范围。

175.可理解,本技术示出的第一比特图样与第一模板比特图样对应,指的是第一码块的第0个比特与第一模板比特图样的第0个比特对应,第一码块的第1个比特与第一模板比特图样的第1个比特对应,第一码块的第2个比特与第二模板比特图样的第2个比特对应,以此类推。示例性的,如图8a(2)所示,第一比特图样的第0个比特和第1个比特分别为10,则该10可以与第一模板比特图样中的第0个比特和第1个比特10进行对比。第一比特图样的第2个比特至第9个比特为0x79,二进制为0111 1001,则该第2个比特至第9个比特,即0111 1001需要与第一模板比特图样中的第2个比特至第9个比特的0111 1000对比。

176.可理解,这里关于对应的说明,下文示出的各个实施例同样适用,下文对于第一比特图样与第一模板比特图样的对应关系,第二比特图样与第二模板比特图样的对应关系,以及第三比特图样与第三模板比特图样的对应关系,不再赘述。

177.本技术提供的第一通道(又可以称为灵活小颗粒通道或低阶通道等)可以透传mtn网络。同时,该第一通道通过时隙复用的方式,映射至第二通道(又可以称为大颗粒通道或高阶通道或mtn通道等)。由于第二通道是基于以太网物理端口的,所以第二通道在任意两个节点的速率都存在 /-100ppm的速率差。因此,为了使得第一通道能够透传于第二通道,本技术示出的码组需要进行格式封装,使得第一通道可以复用第二通道的速率适配方式。基于此,本技术提供一种码组,该码组可以包括一个s码块,多个d码块和一个t码块。可理解,对于码组的具体说明,可以参考上文描述,这里不再详述。

178.本技术中,当通信装置接收到码块流之后,需要从相应的第二时隙中恢复出fgbu序列流。然后从fgbu序列流中先识别每一个fgbu,再提取每个fgbu对应的第一时隙。由此,通过识别s码块,就可以识别fgbu。同时识别s码块的过程,也可以称为fgbu定帧。如果定帧过程中出现异常,就会导致fgbu对应的多个第一时隙(如上文示出的24个第一时隙)均无法被提取,导致fgbu均被丢弃,以及导致fgbu包括的多个d码块均被标记为错误码块。进而,导致fgbu对应的多个时隙或多个客户信号均无法被正确接收,造成系统容错性差。

179.鉴于此,本技术提供一种码块识别方法及装置,可以改善s码块因为偶发的误码而无法被识别的情况。以及改善由于s码块由于偶发的误码而无法识别,导致整个码组被丢弃的情况。同时,本技术提供的方法,还能够有效提高系统容错性。

180.本技术提供的码块识别方法可以应用于通信装置,该通信装置可以为有线设备、交换机、路由器、网卡、分组传送网(packet transport network,ptn)、(agile transport network,atn)、切片分组网(slicing packet network,spn)等,本技术对于该通信装置的具体形态不作限定。示例性的,该通信装置可以包括用于接收码块流的接收端;或者,该通信装置也可以理解为用于接收码组的接收端等。

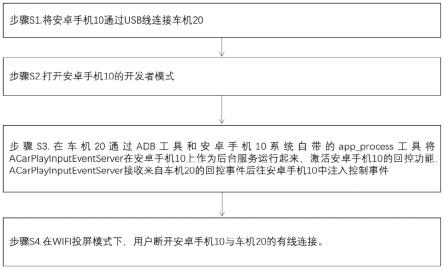

181.图9是本技术实施例提供的一种码块识别方法的流程示意图,如图9所示,该方法包括:

182.901、获取码块流,该码块流包括第一码块。

183.例如,通信装置可以接收码块流,然后从码块流中获取第一码块。可理解,这里所示的通信装置获取码块流,可以理解为:该通信装置接收来自物理层的码块流;或者,该通信装置从其他装置获取码块流;或者,该通信装置从mtn段层或mtn通道层获取码块流等。本技术实施例对于该通信装置如何获取码块流不作限定。

184.902、确定待识别比特图样,该待识别比特图样包括第一比特图样,该第一比特图样为第一码块对应的比特图样。

185.对于待识别比特图样的具体说明,可以参考上文,这里不再详述。

186.示例性的,通信装置可以从接收到的码块流中获取第一码块,然后从该第一码块中获得该第一码块的第0个比特至第9个比特等,该第一码块的第0个比特至第9个比特即为待验证比特图样。

187.可理解,通信装置可以在mtn段层接收该码块流,然后在mtn通道层确定待识别比特图样。或者,通信装置可以通过收发器接收码块流,然后在mtn段层确定待识别比特图样等,本技术实施例对此不作限定。

188.在一种可能的实现方式中,通信装置可以在接收到该码块流时,确定待识别比特图样。示例性的,通信装置在mtn段层接收到码块流时,可以确定待识别比特图样。然后,该通信装置可以执行图9所示的方法,以及该通信装置从码块流中识别出第一边界码块之后,便可以获得以该第一边界码块为开始的码块流。例如,通信装置从码块流中识别出s码块之后,便可以获得该s码块之后的多个d码块,然后获得客户信号等。

189.在另一种可能的实现方式中,通信装置需要在mtn通道层从第二通道中解复用出第一通道的情况下,该通信装置可以从码块流中确定待识别比特图样。例如,通信装置可以在mtn通道适配层确定待识别比特图样。然后,该通信装置可以执行图9所示的方法,以及该通信装置从码块流中识别出第一边界码块之后,便可以获得以该第一边界码块为开始的码组。例如,通信装置从码块流中识别出s码块之后,便可以获得以s码块为开始的第一码组,以及从该第一码组中获得t个客户信号,该t为正整数。例如t=24。也就是说,通信装置可以从第一码组中获得多个第一时隙对应的客户信号。其中,一个第一时隙可以对应一个客户信号,或者,多个第一时隙可以对应一个客户信号。可理解,对于码组的具体说明,可以参考图5a至图5d,这里不再详述。

190.换句话说,图9所示的方法不仅适用于通信装置需要从第二通道解复用第一通道的场景,即通信装置需要从fgbu序列流中识别每一个fgbu的场景;而且,还适用于从64b/66b码块流中识别s码块的场景等,对于本技术实施例提供的方法所适用的场景不作限定。

191.903、对比待识别比特图样与模板比特图样,获得不一致的比特数,该模板比特图样包括第一模板比特图样,该第一模板比特图样为第一边界码块对应的模板比特图样。

192.本技术实施例中,该第一模板比特图样与第一比特图样对应,即第一模板比特图样在模板比特图样中的位置对应于第一比特图样在待识别比特图样中的位置。换句话说,该第一模板比特图样可以用于识别第一比特图样。

193.对于模板比特图样,以及待识别比特图样与模板比特图样的对应关系,可以参考上文,这里不再详述。如上文所示,模板比特图样可以包括第一模板比特图样,还可以包括第二模板比特图样和/或第三模板比特图样。示例性的,模板比特图样可以参考图6a、图6b、

图7a至图7c等。待识别比特图样与模板比特图样的对应关系可以参考图8a和图8b等。

194.示例性的,码块流中还包括第二码块,待识别比特图样还包括第二比特图样,该第二比特图样为第二码块对应的比特图样。对于该第二比特图样的说明可以参考上文对第一比特图样的说明等,这里不再赘述。由此,第二模板比特图样与第二比特图样对应,即第二模板比特图样可以用于识别第二比特图样。

195.示例性的,码块流中还包括第三码块,待识别比特图样还包括第三比特图样,该第三比特图样为第三码块对应的比特图样。对于该第三比特图样的说明可以参考上文对第一比特图样的说明等,这里不再赘述。由此,第三模板比特图样与第三比特图样对应,即第三模板比特图样可以用于识别第三比特图样。

196.904、在不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

197.本技术实施例中,该第一阈值可以为1,即上述不一致的比特数小于或等于1比特的情况下,通信装置可以识别(或确定)第一码块是第一边界码块(如s码块)。或者,第一阈值可以为2,即上述不一致的比特数小于或等于2比特的情况下,通信装置可以确定第一码块是第一边界码块。或者,该第一阈值还可以取其他值等,本技术实施例不作限定。

198.可选的,步骤904可以包括:在待识别比特图样与模板比特图样不一致的比特数大于或等于1,且该不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

199.换句话说,本技术实施例提供的方法中,待识别比特图样与模板比特图样可以有不一致的比特数,而且该不一致的比特数小于或等于第一阈值,该情况下,通信装置仍可以识别第一码块是第一边界码块。该情况下,对于第一模板比特图样、第二模板比特图样以及第三模板比特图样的具体说明,可以参考上文的描述,这里不再详述。

200.可选的,步骤904可以包括:在第一模板比特图样与第一比特图样不一致,且待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。第一模板比特图样与第一比特图样不一致,指的是第一模板比特图样与第一比特图样在对应位置上的取值不是完全一致的。换句话说,即使第一模板比特图样与第一比特图样不能完全一致,也可以确定第一码块是s码块。这是因为:一方面,每个码块的同步头有2比特的汉明距保护,连续发生两比特错误,如01跳转10概率小;另一方面,控制块类型域之间有4比特的汉明距保护,控制块类型域中的8个比特发生一个比特或两个比特的错误不会导致s码块被误识别为其他控制码块,如o码块或t码块等。因此,本技术实施例中,即使第一比特图样与第一模板比特图样在对应位置上的取值不是完全一致,第一码块也可以被识别为s码块。可理解,对于该同步头和控制块类型域的汉明距保护的说明,适用于本技术示出的第一码块、第二码块或第三码块等。

201.可选的,步骤904还可以包括:在第一模板比特图样与第一比特图样一致,且待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。也就是说,当第一模板比特图样与第一比特图样一致,但是在第二比特图样与第二模板比特图样不一致,但是不一致的比特数小于或等于第一阈值的情况下,通信装置仍可以识别第一码块是第一边界码块。示例性的,第二码块的同步头为0b10、0b00或0b11,则说明该第二码块的同步头可能存在偶发误码,由此,第一码块仍可以被识别为第一

边界码块。

202.可选的,步骤904还可以包括:确定第二比特图样,对比第二比特图样和第二模板比特图样;在待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值,且第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。

203.本技术实施例中,该第二阈值可以小于或等于第一阈值。示例性的,该第二阈值可以为1等,本技术实施例对此不作限定。本技术实施例中,通信装置还可以对比第二比特图样与第二模板比特图样,从而在待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,以及在该第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。

204.换句话说,通信装置可以对待识别比特图样(如第一比特图样)与模板比特图样(如第一模板比特图样)进行对比,以及对第二比特图样与第二模板比特图样进行对比。从而,当待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,以及在第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。需要说明的是,第二比特图样与第二模板比特图样的不一致的比特数不包含于上述第一阈值中。

205.可选的,步骤904还可以包括:确定第二比特图样,对比第二比特图样和第二模板比特图样;在待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,以及在第二比特图样与第二模板比特图样一致的情况下,识别第一码块是第一边界码块。

206.可理解,对于第二比特图样和第二模板比特图样的说明可以参考本技术的其他实施例,这里不再详述。

207.本技术实施例提供的方法,可以有效改善第一码块与第一边界码块(如s码块)不一致的比特数不为0比特时,确定第一码块不为第一边界码块的情况。从而,改善了由于偶发误码导致第一码块无法被识别为第一边界码块的情况,提高了系统的容错性。示例性的,通过改善上述情况,而有效改善由于无法识别s码块而丢弃整个码组的情况。通过对s码块的识别,使得通信装置能够解复用出以s码块为开始的码组对应的多个第一时隙,从而获得该多个第一时隙对应的客户信号,不仅实施简单,而且还能够有效保证码组被识别的可靠性。

208.结合上文示出的各个方法,以下将以发送端和接收端为例详细对本技术实施例提供的码块识别方法进行说明。

209.图10a是本技术实施例提供的一种码块识别方法的流程示意图。如图10a所示,该方法包括:

210.1001、发送端获取客户信号(client)。

211.步骤1001可以包括:发送端从面板侧接口接收客户信号;或者,发送端生成客户信号等。可理解,这里所示的面板侧接口可以理解为用户侧接口(user network interface,uni)等。

212.1002、发送端对客户信号进行业务映射封装,获得fgbu序列流。

213.如以图3为例,发送端在获取到客户信号之后,可以通过mtn fg适配层形成预设长

度的fgbu。然后发送端可以在mtn fg终结层将fgbu映射至第一通道。

214.1003、发送端将fgbu序列流映射至第二通道。

215.这里所示的fgbu序列流指的是在未映射至第二通道之前,发送端传输的是fgbu。示例性的,发送端可以在mtn通道层将fgbu序列流映射至第二通道。结合图3,发送端可以在mtn通道适配层复用第二通道划分出的一个或多个第一时隙,即该第一通道可以包括一个或多个第一时隙。示例性的,下文将以第一通道包括m个第一时隙为例说明图10a所示的方法。

216.1004、发送端将第二通道映射至一个或多个第二时隙。

217.示例性的,发送端可以在mtn段层将第二通道映射至一个或多个第二时隙。如以图3为例,发送端可以在mtn段层适配层将第二通道映射至一个或多个第二时隙,从而复用捆绑组。例如,发送端在mtn段层适配层,需要将各路mac的业务流(即64b/66b码块的形式)进行交织,从而形成一路64b/66b码块流。该情况下,发送端可以将第二通道中的各个码块映射至一个或多个第二时隙。

218.示例性的,下文将以第二通道包括n个第二时隙为例说明图10a所示的方法。

219.1005、发送端发送64b/66b码块流。

220.示例性的,该64b/66b码块流可以mtn段层终结层、适配层等进入物理层进行传输。

221.1006、接收端接收64b/66b码块流。

222.示例性的,接收端可以从物理层获得该64b/66b码块流。

223.1007、接收端从捆绑组中的n个第二时隙中解复用第二通道,获得该n个第二时隙中的fgbu码块流。

224.可理解,这里示出的fgbu码块流指的是接收端接收到的仍然是64b/66b码块的形式。

225.1008、接收端识别s码块。

226.对于接收端识别s码块的方法可以参考图9,以及下文示出的方法实施例等,这里不再详述。

227.1009、接收端解封装fgbu。

228.接收端从码块流中识别出s码块之后,可以根据该s码块识别以s码块为开始的fgbu。示例性的,接收端可以获得该fgbu中的195个数据码块以及一个t码块。示例性的,接收端识别出s码块之后,可以在mtn通道层从第二通道中的m个第一时隙中解复用第一通道,从而获得以s码块为开始的fgbu。

229.可理解,这里所示的接收端从第二通道中的m个第一时隙中解复用第一通道,也可以理解为:接收端从第二通道的m个第一时隙中恢复第一通道,从而获得该第一通道中的fgbu。

230.1010、接收端提取客户信号。

231.示例性的,接收端从第二通道中的m个第一时隙中解复用第一通道之后,便可以获得该m个第一时隙中每个时隙对应的客户信号。

232.可理解,接收端提取出客户信号之后,还可以对业务流进行转发或者终结操作等,本技术实施例对此不作限定。

233.上述步骤1008,接收端识别s码块可以理解为是由接收端的处理器执行,或者,也

可以理解为是在接收端的mtn网络中的mtn通道适配层中实现(仅为示例),或者,也可以理解为是由接收端中的功能或模块或单元执行等,本技术实施例对此不作限定。

234.作为示例,如图10b所示,接收端识别s码块的功能模块可以包括:模板匹配模块,模板存储模块,检验窗口模块。该模板存储模块中保存着识别第一码块为s码块所需要的模板。即该模板存储模块用于存储本技术实施例示出的模板比特图样。检验窗口模块可以用于从第一码块、第二码块或第三码块中提取相应比特,组成待识别比特图样。该模板匹配模块用于将检验窗口内的比特图样(即待识别比特图样)与模板比特图样比较。

235.由此,接收端可以将符合比较结果预期的第一码块识别为s码块。随着s码块的确定,接收端就可以完成fgbu定帧。从而根据fgbu开始的位置获取该fgbu所封装的时隙数据等。

236.可理解,图10b所示的各个模块仅为示例,本技术实施例对此不作限定。

237.为更详细地理解上述方法,以下将提供码块识别方法的具体实施例。可理解,以下各个实施例的执行主语可以理解为是64b/66b码块流的接收端。

238.在本技术实施例中,第二码块和第三码块可以分别为与第一码块相邻的码块。因此,为便于描述,以下将以第一码块为第i码块,第二码块为第i-1码块,第三码块为第i 1码块为例,说明本技术实施例提供的码块识别方法。

239.实施例一、

240.图11是本技术实施例提供的一种码块识别方法的流程示意图,如图11所示,该方法包括:

241.1101、接收端从n个5gbps中恢复出码块流。

242.可理解,对于接收端如何从n个5gbps中恢复出码块流,可以参考上文,这里不再详述。

243.1102、接收端从码块流中获取第i码块。

244.在一种可能的实现方式中,接收端可以以固定的周期从码块流中获取一个码块(即第i码块)。

245.在另一种可能的实现方式中,接收端可以根据码组的预设长度从码块流中获取第i码块。例如,码组包括197个码块时,该接收端可以根据该码组的长度,每197个码块获取一个码块(即第i码块)。

246.在又一种可能的实现方式中,接收端还可以根据已知码块的同步头等从码块流中获取第i码块。例如,接收端已经获知某个码块的同步头为0b10,则该某个码块即可以为第i码块。获知,该某个码块的前一个码块或下一个码块等也可以为第i码块等。

247.可理解,上述示出的接收端从码块流中获取第i码块,也可以理解为:接收端开始对对i码块进行识别;或者,接收端从码块流中搜索第i码块等。

248.可理解,本技术实施例对于接收端以何种方式获取第i码块不作限定。

249.1103、接收端判断第i码块的同步头是否为0b10,如果是,则执行步骤1105;否则,执行步骤1104。

250.1104、接收端确定第i码块不为s码块,即第i码块无法被识别为s码块。

251.可理解,在第i码块无法被识别为s码块的情况下,该接收端可以停止搜索码块。或者,接收端还可以开始下一个码块的搜索等,本技术实施例对此不作限定。

252.1105、接收端获取第i码块的第2个比特至第9个比特,得到待识别比特图样。

253.结合图10b所示的识别s码块的模块示意图,接收端可以通过检测窗口模块获取第i码块的第2个比特至第9个比特。

254.1106、接收端将待识别比特图样与模板比特图样进行对比,获得不一致的比特数。并判断不一致的比特数是否小于或等于k比特,如果是,则执行步骤1107;否则,执行步骤1108。

255.可理解,接收端可以将待识别比特图样与模板比特图样在对应位置上进行对比。以及该模板比特图样可以为s码块的比特图样。例如,模板比特图样可以为s码块的第2个比特至第9个比特对应的模板比特图样。又例如,模板比特图样还可以为s码块的第0个比特至第65个比特对应的模板比特图样。但是在对比时,由于接收端获取的是第i码块的第2比特至第9比特,因此,接收端需要将第i码块的第2比特至第9比特依次与s码块的第2比特至第9比特对比。可理解,对于模板比特图样的说明,下文示出的各个实施例同样适用。

256.本技术实施例中,接收端还可以获取第i码块的更多比特,如获取第i码块的第2个比特至第65个比特等;或者,获取第i码块的第2个比特至第17个比特。

257.可选的,接收端还可以不执行上述步骤1103,而是直接获取第i码块的第0个比特至第9个比特等,本技术实施例对此不作限定。

258.1107、不一致的比特数小于或等于k比特(如k=2),接收端确定第i码块为s码块。

259.1108、不一致的比特数大于k比特,接收端确定第i不能被识别为s码块。

260.可理解,对于接收端识别出s码块,从第二通道中解复用第一通道的具体实现,可以参考上文,这里不再详述。

261.本技术实施例中,接收端通过获取第i码块,对该第i码块进行s码块的识别。从而,即使是第i码块的比特图样与s码块的比特图样不完全一致,只要待识别比特图样与模板比特图样在对应位置不一致的比特数小于或等于k比特,该第i码块仍可以被识别为s码块。该方法不仅实施方便简单,而且有效提高了系统的容错性。

262.实施例二、

263.图12a是本技术实施例提供的一种码块识别方法的流程示意图,如图12a所示,该码块识别方法包括:

264.1201、接收端从n个5gbps中恢复出码块流。

265.1202、接收端从码块流中获取第i码块和第i-1码块。

266.在一种可能的实现方式中,接收端可以从码块流中获取相邻的两个码块,该相邻的两个码块分别为第i-1码块和第i码块。

267.在另一种可能的实现方式中,接收端可以从码块流中获取一个码块,即第i码块。然后再获取该第i码块的上一个码块,即第i-1码块。

268.在又一种可能的实现方式中,接收端还可以根据已被识别为不是s码块的码块获取第i码块和第i-1码块。对于该种实现方式可以参考图12b所示的方法,示例性的,对于该实现方式可以适应性参考图12b中的步骤1213等。

269.1203、接收端根据第i码块的前p个比特与第i-1码块的前q个比特确定待识别比特图样。

270.示例性的,接收端获取第i码块和第i-1码块后,可以获取第i码块的前p个比特,以

及第i-1码块的前q个比特。又或者,接收端也可能已对第i-1码块进行识别,该情况下,接收端已经获得了第i-1码块的比特图样。由此,接收端便可以获取第i码块的前p个比特。从而,根据该第i码块的前p个比特以及第i-1码块的前q个比特,组成待识别比特图样。该p为大于或等于2的整数,该q为大于或等于2的整数。

271.例如,p=q=10时,待识别比特图样内的第0比特至第9比特可以依次为第i-1码块的前10个比特,该待识别比特图样内的第10比特至第19比特可以依次为第i码块的前10个比特。

272.1204、接收端将待识别比特图样与模板比特图样进行对比,获得不一致的比特数。并判断不一致的比特数是否小于或等于k比特,如果是,则执行步骤1205;否则,执行步骤1206。

273.示例性的,模板比特图样可以如图7a所示。

274.1205、不一致的比特数小于或等于k比特(例如k=2),接收端确定第i码块为s码块。

275.1206、不一致的比特数大于k比特,接收端确定第i不能被识别为s码块。

276.本技术实施例提供的方法,可以进一步提高系统的容错性。

277.实施例三、

278.1211、接收端从n个5gbps中恢复出码块流。

279.1212、接收端从码块流中获取第i码块。

280.1213、接收端判断第i码块的同步头是否为0b10,如果是,则执行步骤1215;否则,执行步骤1214。

281.1214、接收端确定第i码块不为s码块,即第i码块无法被识别为s码块。

282.该接收端在识别第i码块不为s码块的情况下,还可以保存该第i码块的至少两个比特。示例性的,接收端可以保存该第i码块的同步头。或者,该接收端还可以保存该第i码块的第0个比特至第9个比特。或者,该接收端还可以保存该第i码块的第0个比特至第66个比特等。通过保存该第i码块的至少两个比特,一方面,可使得接收端后续需要使用该第i码块的至少两个比特时,直接获取保存的第i码块的至少两个比特。另一方面,通过保存该第i码块的至少两个比特,还可以为接收端后续识别第i 1码块等提供有益信息。可理解,关于保存第i码块的说明,本技术示出的其他实施例,同样适用。

283.1215、接收端获取第i码块的第2个比特至第9个比特,得到待识别比特图样。

284.1216、接收端将待识别比特图样与模板比特图样进行对比,获得不一致的比特数。并判断不一致的比特数是否小于或等于k比特,如果是,则执行步骤1217;否则,执行步骤1218。

285.示例性的,模板比特图样可以如图6a或图6b所示。

286.1217、接收端获取第i-1码块的第0个比特和第1个比特。

287.示例性的,该接收端还可以获取该第i-1码块的第0个比特至第9个比特等,本技术实施例对此不作限定。

288.1218、接收端确定第i码块不为s码块。

289.1219、根据该第i-1码块的第0个比特和第1个比特,判断该第i-1码块的同步头是否为0b01;如果否,则执行步骤1220;如果是,执行步骤1221。

290.可理解,本技术实施例中,当第i-1码块的同步头为0b01时,则说明该第i-1码块是数据码块,则第一码块不可能为s码块。而当第i-1码块不为数据码块,如第i-1码块为错误码块、t码块或o码块等,则说明第i码块可以为s码块。

291.可理解,本技术实施例对于步骤1217与步骤1216或步骤1215等的先后顺序不作限定。例如,接收端还可以同时执行步骤1215和步骤1217等,本技术实施例对此不作限定。

292.1220、接收端确定第i码块为s码块。

293.1221、接收端确定第i码块不为s码块。

294.可理解,该情况下,接收端还可以保存第i-1码块的第2个比特至第9个比特,或者第i码块的第2个比特至第9个比特等。

295.本技术实施例中,接收端通过将第i码块的比特图样与模板比特图样进行对比,就可以确定该第i码块是否可以被识别为s码块。进一步地,通过判断第i-1码块是否为控制码块,可以进一步提高第i码块被识别为s码块的准确度和可靠性,同时还能够保证系统的容错性。

296.可理解,本技术实施例示出的方法同样适用于第i码块和第i 1码块的实施例,为避免赘述,下文不再详细说明。

297.实施例四、

298.图13是本技术实施例提供的一种码块识别方法的流程示意图,如图13所示,该方法包括:

299.1301、接收端从n个5gbps中恢复出码块流。

300.1302、接收端从码块流中获取第i码块和第i 1码块。

301.可理解,对于接收端获取第i码块和第i 1码块的具体说明,可以参考上文示出的步骤1202的说明,这里不再详述。

302.1303、接收端根据第i码块的前p个比特与第i 1码块的前q个比特确定待识别比特图样。

303.1304、接收端将待识别比特图样与模板比特图样进行对比,获得不一致的比特数。并判断不一致的比特数是否小于或等于k比特,如果是,则执行步骤1305;否则,执行步骤1306。

304.示例性的,模板比特图样可以如图7b所示。

305.1305、不一致的比特数小于或等于k比特(例如k=2),接收端确定第i码块为s码块。

306.1306、不一致的比特数大于k比特,接收端确定第i不能被识别为s码块。

307.可理解,对于图13的具体描述可以参考图11、图12a或图12b中的描述等,这里不再详述。

308.实施例五、

309.图14是本技术实施例提供的一种码块识别方法的流程示意图,如图14所示,该方法包括:

310.1401、接收端从n个5gbps中恢复出码块流。

311.1402、接收端从码块流中获取第i-1码块、第i码块和第i 1码块。

312.可理解,对于接收端获取第i-1码块、第i码块和第i 1码块的具体说明,可以参考

上文示出的步骤1202等的说明,这里不再详述。

313.1403、接收端根据第-1码块的前r个比特、第i码块的前p个比特与第i 1码块的前q个比特确定待识别比特图样。

314.1404、接收端将待识别比特图样与模板比特图样进行对比,获得不一致的比特数。并判断不一致的比特数是否小于或等于k比特,如果是,则执行步骤1405;否则,执行步骤1406。

315.示例性的,当r=p=q=10时,该模板比特图样可以如图7c所示。可理解,本技术实施例示出的p、q或r仅为示例,对于其具体取值,本技术实施例不作限定。

316.1405、不一致的比特数小于或等于k比特(例如k=2),接收端确定第i码块为s码块。

317.1406、不一致的比特数大于k比特,接收端确定第i不能被识别为s码块。

318.本技术实施例中,接收端通过获取第i码块,以及与第i码块相邻的两个码块,从而结合模板比特图样对第i码块是否为s码块进行判断,有效提高了判断第i码块为s码块的准确性,同时提高了系统的容错性。

319.可理解,以上所示的各个实施例中,其中一个实施例中未详尽描述的实现方式,可以参考另一个实施例的描述,这里不作详述。或者,本文中描述的各个实施例可以为独立的方案,也可以根据内在逻辑进行组合,这些方案都落入本技术的保护范围中。换句话说,以上所示的各个实施例相互之间可以结合。

320.以下将介绍本技术实施例提供的通信装置。

321.图15是本技术实施例提供的一种通信装置的结构示意图,该通信装置可以用于执行上述方法实施例中如图9、图10a、图11、图12a、图12b、图13或图14所示的方法。示例性的,该通信装置可以为任意形态的交换机(或者称为交换设备、交换芯片等)、路由器或网卡等等,本技术实施例对于该通信装置的具体形态不作的。如图15所示,该通信装置包括:处理单元1501和收发单元1502。

322.收发单元1502,用于获取码块流,该码块流中包括第一码块;

323.处理单元1501,用于确定待识别比特图样,以及对比该待识别比特图样和模板比特图样,获得不一致的比特数;在该不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

324.在一种可能的实现方式中,处理单元1501,具体用于在不一致的比特数大于或等于1,且该不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

325.示例性的,第二阈值可以为2或1等,本技术实施例对此不作限定。

326.在一种可能的实现方式中,处理单元1501,具体用于在第一比特图样与第一模板比特图样不一致,且待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

327.在一种可能的实现方式中,处理单元1501,具体用于确定第二比特图样,该第二比特图样为第二码块对应的比特图样;对比第二比特图样与第二模板比特图样;在不一致的比特数小于或等于第一阈值,且第二比特图样与第二模板比特图样的不一致的比特数小于或等于第二阈值的情况下,识别第一码块是第一边界码块。

328.在一种可能的实现方式中,处理单元1501,具体用于确定第二比特图样,对比第二

比特图样与第二模板比特图样,在待识别比特图样与模板比特图样的不一致的比特数小于或等于第一阈值,且在第二比特图样与第二模板比特图样不一致,识别第一码块是第一边界码块。

329.在一种可能的实现方式中,处理单元1501,具体用于根据第一码块从码块流中确定第一码组,该第一码组以第一码块开始。

330.可理解,关于第一比特图样、第二比特图样、第三比特图样、待识别比特图样、模板比特图样、第一码块、第二码块、第三码块以及第一边界码块等的描述,可以参考前述各个实施例等,这里不再详述。

331.示例性的,收发单元1502可以用于执行图9中的步骤901,处理单元1501可以用于执行图9中的步骤902至步骤904。

332.示例性的,收发单元1502还可以用于执行图10a中的步骤1006,处理单元1501还可以用于执行图10a中的步骤1007至步骤1010。

333.示例性的,处理单元1501还可以用于执行图11中的步骤1101至步骤1108。

334.可理解,对于收发单元和处理单元的其他功能或步骤等,可以参考上述方法实施例,这里不再一一列举。

335.本技术实施例中对模块的划分是示意性的,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,另外,在本技术各个实施例中的各功能模块或单元可以集成在一个处理器中,也可以是单独物理存在,也可以两个或两个以上模块或单元集成在一个模块或单元中。上述集成的模块或单元既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。

336.以上介绍了本技术实施例的通信装置,以下介绍所述通信装置可能的产品形态。应理解,但凡具备上述图15所述的通信装置的功能的任何形态的产品,都落入本技术实施例的保护范围。还应理解,以下介绍仅为举例,不限制本技术实施例的通信装置的产品形态仅限于此。

337.在一种可能的实现方式中,当图15所示的通信装置是任意形态的交换机、路由器或网卡等;或者是任意形态的交换机、路由器或网卡等中的装置,或者是与任意形态的交换机、路由器或网卡等匹配使用的装置时,处理单元1501可以是一个或多个处理器,收发单元1502可以是收发器,或者收发单元1502还可以是发送单元和接收单元,发送单元可以是发送器,接收单元可以是接收器,该发送单元和接收单元集成于一个器件,例如收发器。本技术实施例中,处理器和收发器可以被耦合等,对于处理器和收发器的连接方式,本技术实施例不作限定。

338.如图16所示,该通信装置160包括一个或多个处理器1620和收发器1610。

339.本技术实施例中,该处理器1620和该收发器1610可以用于执行上述通信装置或接收端执行的方法。

340.示例性的,收发器1610可以用于接收码块流,处理器1620可以用于对码块流中的第一码块进行识别等。

341.可理解,关于第一比特图样、第二比特图样、第三比特图样、待识别比特图样、模板比特图样、第一码块、第二码块、第三码块以及第一边界码块等的描述,可以参考前述各个实施例等,这里不再详述。

342.可理解,对于收发器和/或处理器执行的功能或操作等,可以参考图15示出的各个实施例,或者,还可以参考图9、图10a、图11、图12a、图12b、图13或图14所示的方法实施例,这里不再一一详述。

343.在图16所示的通信装置的各个实现方式中,收发器可以包括接收机和发射机,该接收机用于执行接收的功能(或操作),该发射机用于执行发射的功能(或操作)。以及收发器用于通过传输介质和其他设备/装置进行通信。

344.可选的,通信装置160还可以包括一个或多个存储器1630,用于存储程序指令和/或数据。存储器1630和处理器1620耦合。本技术实施例中的耦合是装置、单元或模块之间的间接耦合或通信连接,可以是电性,机械或其它的形式,用于装置、单元或模块之间的信息交互。处理器1620可能和存储器1630协同操作。处理器1620可能执行存储器1630中存储的程序指令。可选的,上述一个或多个存储器中的至少一个可以包括于处理器中。

345.本技术实施例中不限定上述收发器1610、处理器1620以及存储器1630之间的具体连接介质。本技术实施例在图16中以存储器1630、处理器1620以及收发器1610之间通过总线1640连接,总线在图16中以粗线表示,其它部件之间的连接方式,仅是进行示意性说明,并不引以为限。所述总线可以分为地址总线、数据总线、控制总线等。为便于表示,图16中仅用一条粗线表示,但并不表示仅有一根总线或一种类型的总线。

346.在本技术实施例中,处理器可以是通用处理器、数字信号处理器、专用集成电路、现场可编程门阵列或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等,可以实现或者执行本技术实施例中的公开的各方法、步骤及逻辑框图。通用处理器可以是微处理器或者任何常规的处理器等。结合本技术实施例所公开的方法的步骤可以直接体现为硬件处理器执行完成,或者用处理器中的硬件及软件模块组合执行完成等。

347.本技术实施例中,存储器可包括但不限于硬盘(hard disk drive,hdd)或固态硬盘(solid-state drive,ssd)等非易失性存储器,随机存储记忆体(random access memory,ram)、可擦除可编程只读存储器(erasable programmable rom,eprom)、只读存储器(read-only memory,rom)或便携式只读存储器(compact disc read-only memory,cd-rom)等等。存储器是能够用于携带或存储具有指令或数据结构形式的程序代码,并能够由计算机(如本技术示出的通信装置等)读和/或写的任何存储介质,但不限于此。本技术实施例中的存储器还可以是电路或者其它任意能够实现存储功能的装置,用于存储程序指令和/或数据。

348.可理解,本技术实施例示出的通信装置还可以具有比图16更多的元器件等,本技术实施例对此不作限定。以上所示的处理器和收发器所执行的方法仅为示例,对于该处理器和收发器具体所执行的步骤可参照上文介绍的方法。

349.可理解,本技术实施例示出的通信装置还可以具有比图16更多的元器件等,本技术实施例对此不作限定。

350.可理解,以上所示的处理器和收发器所执行的方法仅为示例,对于该处理器和收发器具体所执行的步骤可参照上文介绍的方法。

351.在另一种可能的实现方式中,当上述通信装置是芯片系统,如交换机(或者称为交换设备、交换芯片等)、路由器、网卡等中的芯片系统时,处理单元1501可以是一个或多个逻辑电路,收发单元1502可以是输入输出接口,又或者称为通信接口,或者接口电路,或接口

等等。或者收发单元1502还可以是发送单元和接收单元,发送单元可以是输出接口,接收单元可以是输入接口,该发送单元和接收单元集成于一个单元,例如输入输出接口。如图17所示,图17所示的通信装置包括逻辑电路1701和接口1702。即上述处理单元1501可以用逻辑电路1701实现,收发单元1502可以用接口1702实现。其中,该逻辑电路1701可以为芯片、处理电路、集成电路或片上系统(system on chip,soc)芯片等,接口1702可以为通信接口、输入输出接口等。本技术实施例中,逻辑电路和接口还可以相互耦合。对于逻辑电路和接口的具体连接方式,本技术实施例不作限定。

352.本技术实施例中,该逻辑电路和该接口可以用于执行上述通信装置或接收端执行的功能或操作等。

353.示例性的,接口1702,用于输入码块流,该码块流中包括第一码块等。逻辑电路1701,用于确定待识别比特图样,以及对比该待识别比特图样和模板比特图样,获得不一致的比特数;在该不一致的比特数小于或等于第一阈值的情况下,识别第一码块是第一边界码块。

354.可理解,关于逻辑电路和接口的具体实现方式,还可以参考上述各个实施例,这里不再一一举例。

355.可理解,关于第一比特图样、第二比特图样、第三比特图样、待识别比特图样、模板比特图样、第一码块、第二码块、第三码块以及第一边界码块等的描述,可以参考前述各个实施例等,这里不再详述。

356.此外,本技术还提供一种计算机程序,该计算机程序用于实现本技术提供的方法中由通信装置或接收端执行的操作和/或处理。

357.本技术还提供一种计算机可读存储介质,该计算机可读存储介质中存储有计算机代码,当计算机代码在计算机上运行时,使得计算机执行本技术提供的方法中由通信装置或接收端执行的操作和/或处理。

358.本技术还提供一种计算机程序产品,该计算机程序产品包括计算机代码或计算机程序,当该计算机代码或计算机程序在计算机上运行时,使得本技术提供的方法中由通信装置或接收端执行的操作和/或处理被执行。

359.在本技术所提供的几个实施例中,应该理解到,所揭露的系统、装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另外,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口、装置或单元的间接耦合或通信连接,也可以是电的,机械的或其它的形式连接。

360.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本技术实施例提供的方案的技术效果。

361.另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以是两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

362.所述集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分,或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个可读存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的可读存储介质包括:u盘、移动硬盘、只读存储器(read-only memory,rom)、随机存取存储器(random access memory,ram)、磁碟或者光盘等各种可以存储程序代码的介质。

363.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。