基于fpga的舰载多路信号采集同步控制系统

技术领域

1.本发明涉及模拟信号的变换传输领域,具体涉及基于fpga的舰载多路信号采集同步控制系统。

背景技术:

2.多路信号采集系统一般由输入的模拟量、调理电路、adc芯片、fpga、光模块组成;其中,调理电路对模拟量进行预处理、adc芯片进行模数转换、fpga进行数据组装。

3.在不同的场合,一般对多路信号采集系统的性能存在更高的要求,比如:将多路信号采集系统应用于舰船平台时,多路信号采集系统在作战和航行时,应能耐受舰船自身武器发射、非接触性爆炸或高强度碰撞等非重复性的强烈冲击,并连续有效地工作。也需要耐受舰船环境的高温等环境。

4.现有技术中,其多路信号采集系统,是由多个adc芯片 1个fpga组成,其输出信号的同步性受到、环境温度、电路本身板材、以及作战冲击的影响。并且在舰载应用场景中,至少要去挂载17路的模拟量的输入,对fpga的同步控制负担要求高。

5.常规的同步技术一般的思路是:例如专利:201821547450 .2,其由于应用的是边防监控,其没有过高输入路数的限定、也没有作战冲击的影响,因此其同步控制方式采用的是由fpga自检数字信号的同步状态,然后输出,具体为:1)先通过外部采样时钟控制3个ad9695芯片,同步对3个tr通道的信号采样;采样率为1280mhz。

6.2)fpga芯片针对3个tr通道,每个通道的目标频点采用数字下变频技术,生成24路基带信号,fpga芯片接收到“外部秒脉冲信号”后,通过gtx接口与mt光模块,将生成的基带信号通过光纤传输到后端。

7.其中,可以看出,fpga芯片获得“外部秒脉冲信号”的作用是组织数字信号进行同步。

8.上述技术若应用于更多路数的输入、以及高温环境、冲击环境时,其仅依赖fpga芯片根据“外部秒脉冲信号”保证输出信号同步,是无法完成的。

技术实现要素:

9.本发明提供基于fpga的舰载多路信号采集同步控制系统,该系统可以支持数量达到17路输入、高温、冲击环境的稳定同步输出。

10.本发明的技术方案为:基于fpga的舰载多路信号采集同步控制系统,包括:1个时钟电路,n个模拟中频回波信号,m个调理电路、m个adc芯片、1个fpga、1个光模块;时钟电路,用于为adc芯片“采样时钟信号”;m个调理电路,用于对引入的n个模拟中频回波信号进行预处理;

m个adc芯片,用于在“采样时钟信号”下对多个预处理后的模拟中频回波信号进行模数转换处理;fpga,用于将多个模数转换处理后的数字中频回波信号组织为光模块所需格式数据,并同步向光模块发送;时钟电路,用于为双通道adc芯片提供“同步用秒脉冲信号”;m个adc芯片,用于依据“同步用秒脉冲信号”对模数转换处理后的数字中频回波信号进行同步输出,完成第一次同步;fpga,用于观测adc芯片的快速检测输出引脚的状态波形中的多帧时钟信号波形、若多帧时钟信号波形存在延时,则等待该adc芯片输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

11.本发明的技术方案由2个技术要点组成:1、将现有用于fpga的“外部秒脉冲信号”,改到用于adc芯片;使得adc芯片在完成模数转换后,需要在秒脉冲的同步控制下向fpga同步输出,完成第一次同步,该同步可以控制进入到fpga的数据在初始时就处于同步状态;而现有技术,仅依赖采用时钟信号对模拟量进行采样,无法保障其输出数字信号时处于同步状态。2、本发明借助adc芯片的“快速检测输出引脚”进行同步效验,再根据效验结果决定输出时机,保障fpga对外输出处于同步状态,从而实现第二次同步,其中,一般在常规技术中,“快速检测输出引脚”一般悬置不适用,或者作为检测adc状态的端子使用,一般会配置监视器观测adc的状态;未见现有技术中将“快速检测输出引脚”与fpga关联使用的技术,本发明经过研究发现,可以从“快速检测输出引脚”的状态波形中找到表征输出数字信号的多帧时钟信号波形;因此,对于fpga而言,其可以通过观测多帧时钟信号波形,来确定其自身获得数字信号的同步状态,若其中存在不同步时,则可以对其进行修正,即adc输出同步失效时,可以对其在fpga位置进行修正,从而达到效验修正的目的。

12.本发明可以理解为:利用2次同步,实现多级、分硬件级区的同步控制,即adc作为第一级硬件进行输出同步,fpga作为第二级硬件进行输出同步,因此,即使在高温、冲击的影响下,能及时在输出节点完成纠正,从而保证每级的输出同步。

13.优选的,所述n为17或18,所述m为9,所述adc芯片为双通道adc芯片、型号为:ad9680。

14.优选的,fpga型号为:xc7vx690t-2ffg1927i。

15.优选的,还包括设置有可编程阈值的可编程阈值检测器,可编程阈值检测器,用于对所有adc芯片的快速检测输出引脚fd_a或/和快速检测输出引脚fd_b引脚的状态波形中的输入信号功率波形进行监控,若输入信号功率波形超过可编程阈值,可编程阈值检测器输出调低adc系统增益的控制信号至adc芯片。

16.优选的,当adc芯片为双通道adc芯片,1个adc芯片处理2个模拟中频回波信号为2个数字中频回波信号时;fpga,用于同时观测1个adc芯片的快速检测输出引脚fd_a和快速检测输出引脚fd_b引脚的状态波形中的多帧时钟信号波形、若该adc芯片的2个多帧时钟信号波形相比存在延时,则等待该adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

17.优选的,当adc芯片为双通道adc芯片,1个adc芯片处理2个模拟中频回波信号为2个数字中频回波信号时;fpga,用于同时观测所有adc芯片的快速检测输出引脚fd_a或快速检测输出引脚fd_b引脚的状态波形中的多帧时钟信号波形、若第i个adc芯片的多帧时钟信号波形与其它adc芯片的多帧时钟信号波形相比存在延时,则等待第i个adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

18.优选的,当adc芯片为单通道adc芯片,1个adc芯片处理1个模拟中频回波信号为1个数字中频回波信号时;fpga,用于同时观测所有adc芯片的快速检测输出引脚fd的状态波形中的多帧时钟信号波形、若第i个adc芯片的多帧时钟信号波形与其它adc芯片的多帧时钟信号波形相比存在延时,则等待第i个adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

19.本发明相比现有技术而言,其具备多级同步控制方式,多同步控制具备更多的冗余保障,且其在adc与fpga之间直接采用监测快速检测输出引脚的做法,可以避免外部引入另外的同步时钟时导致同步的不一致性;同时,其效验同步的做法,并不是由传统fpga引入外部脉冲信号进行同步对齐的做法,这种仅比对多帧时钟信号波形延时的做法,可以解决fpga的开销负担,使得fpga可以挂载更多的adc;而传统fpga引入外部脉冲信号进行同步对齐的做法;需要fpga对将数据在脉冲信号的基准下进行对齐;因此,其做法会导致大量的计算开销,因此无法支撑挂载较多的adc。

附图说明

20.此处所说明的附图用来提供对本发明实施例的进一步理解,构成本技术的一部分,并不构成对本发明实施例的限定。在附图中:图1为本发明的结构示意图。

21.图2为fpga与adc的引脚连接图。

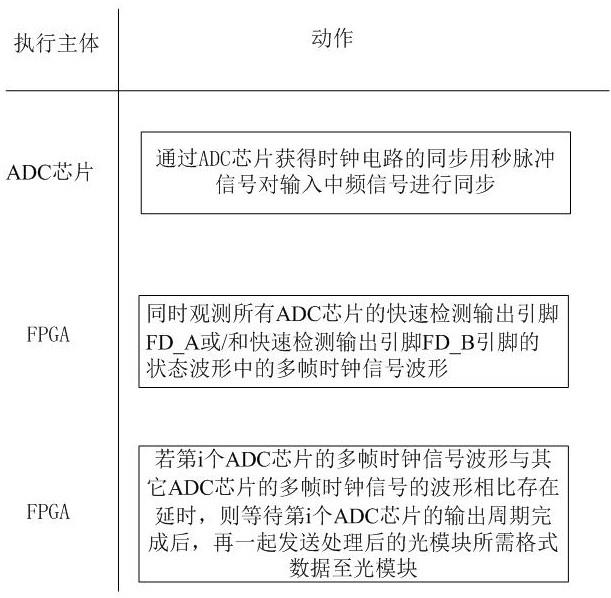

22.图3为同步控制流程图。

具体实施方式

23.为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

24.实施例1:如图1至图3所示,基于fpga的舰载多路信号采集同步控制系统,如图1所示,图1为本发明的结构示意图。该系统包括:1个时钟电路,n个模拟中频回波信号,m个调理电路、m个adc芯片、1个fpga、1个光模块;时钟电路,用于为adc芯片“采样时钟信号”;

m个调理电路,用于对引入的n个模拟中频回波信号进行预处理;m个adc芯片,用于在“采样时钟信号”下对多个预处理后的模拟中频回波信号进行模数转换处理;fpga,用于将多个模数转换处理后的数字中频回波信号组织为光模块所需格式数据,并同步向光模块发送;时钟电路,用于为双通道adc芯片提供“同步用秒脉冲信号”;m个adc芯片,用于依据“同步用秒脉冲信号”对模数转换处理后的数字中频回波信号进行同步输出,完成第一次同步;fpga,用于观测adc芯片的快速检测输出引脚的状态波形中的多帧时钟信号波形、若多帧时钟信号波形存在延时,则等待该adc芯片输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

25.如图3所示,图3为同步控制流程图。

26.本发明的技术方案由2个技术要点组成:1、将现有用于fpga的“外部秒脉冲信号”,改到用于adc芯片;使得adc芯片在完成模数转换后,需要在秒脉冲的同步控制下向fpga同步输出,完成第一次同步,该同步可以控制进入到fpga的数据在初始时就处于同步状态;而现有技术,仅依赖采用时钟信号对模拟量进行采样,无法保障其输出数字信号时处于同步状态。2、本发明借助adc芯片的“快速检测输出引脚”进行同步效验,再根据效验结果决定输出时机,保障fpga对外输出处于同步状态,从而实现第二次同步,其中,一般在常规技术中,“快速检测输出引脚”一般悬置不适用,或者作为检测adc状态的端子使用,一般会配置监视器观测adc的状态;未见现有技术中将“快速检测输出引脚”与fpga关联使用的技术,本发明经过研究发现,可以从“快速检测输出引脚”的状态波形中找到表征输出数字信号的多帧时钟信号波形;因此,对于fpga而言,其可以通过观测多帧时钟信号波形,来确定其自身获得数字信号的同步状态,若其中存在不同步时,则可以对其进行修正,即adc输出同步失效时,可以对其在fpga位置进行修正,从而达到效验修正的目的。

27.本发明可以理解为:利用2次同步,实现多级、分硬件级区的同步控制,即adc作为第一级硬件进行输出同步,fpga作为第二级硬件进行输出同步,因此,即使在高温、冲击的影响下,能及时在输出节点完成纠正,从而保证每级的输出同步。

28.实施例2:如图1至图3所示,基于fpga的舰载多路信号采集同步控制系统,包括:1个时钟电路,17或18个模拟中频回波信号,9个调理电路、9个adc芯片、1个fpga、1个光模块;所述adc芯片为双通道adc芯片、型号为:ad9680。优选的,fpga型号为:xc7vx690t-2ffg1927i。

29.如图2所示,图2为fpga与adc的引脚连接图,ser dou用传输通道传输的数据;adc芯片的快速检测输出引脚fd_a或/和快速检测输出引脚fd_b引脚连接至fpga;时钟电路,用于为adc芯片“采样时钟信号”;9个调理电路,用于对引入的17或18个模拟中频回波信号进行预处理;9个adc芯片,用于在“采样时钟信号”下对多个预处理后的模拟中频回波信号进行模数转换处理;fpga,用于将多个模数转换处理后的数字中频回波信号组织为光模块所需格式数

据,并同步向光模块发送;时钟电路,用于为双通道adc芯片提供“同步用秒脉冲信号”;9个adc芯片,用于依据“同步用秒脉冲信号”对模数转换处理后的数字中频回波信号进行同步输出,完成第一次同步;fpga,用于观测adc芯片的快速检测输出引脚的状态波形中的多帧时钟信号波形、若多帧时钟信号波形存在延时,则等待该adc芯片输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

30.本发明的技术方案由2个技术要点组成:1、将现有用于fpga的“外部秒脉冲信号”,改到用于adc芯片;使得adc芯片在完成模数转换后,需要在秒脉冲的同步控制下向fpga同步输出,完成第一次同步,该同步可以控制进入到fpga的数据在初始时就处于同步状态;而现有技术,仅依赖采用时钟信号对模拟量进行采样,无法保障其输出数字信号时处于同步状态。2、本发明借助adc芯片的“快速检测输出引脚”进行同步效验,再根据效验结果决定输出时机,保障fpga对外输出处于同步状态,从而实现第二次同步,其中,一般在常规技术中,“快速检测输出引脚”一般悬置不适用,或者作为检测adc状态的端子使用,一般会配置监视器观测adc的状态;未见现有技术中将“快速检测输出引脚”与fpga关联使用的技术,本发明经过研究发现,可以从“快速检测输出引脚”的状态波形中找到表征输出数字信号的多帧时钟信号波形;因此,对于fpga而言,其可以通过观测多帧时钟信号波形,来确定其自身获得数字信号的同步状态,若其中存在不同步时,则可以对其进行修正,即adc输出同步失效时,可以对其在fpga位置进行修正,从而达到效验修正的目的。

31.本发明可以理解为:利用2次同步,实现多级、分硬件级区的同步控制,即adc作为第一级硬件进行输出同步,fpga作为第二级硬件进行输出同步,因此,即使在高温、冲击的影响下,能及时在输出节点完成纠正,从而保证每级的输出同步。

32.fpga完成第二次同步的过程有:第一种:fpga,可以用于同时观测1个adc芯片的快速检测输出引脚fd_a和快速检测输出引脚fd_b引脚的状态波形中的多帧时钟信号波形、若该adc芯片的2个多帧时钟信号波形相比存在延时,则等待该adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

33.第二种:fpga,可以用于同时观测所有adc芯片的快速检测输出引脚fd_a或快速检测输出引脚fd_b引脚的状态波形中的多帧时钟信号波形、若第i个adc芯片的多帧时钟信号波形与其它adc芯片的多帧时钟信号波形相比存在延时,则等待第i个adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

34.其中,fpga技术要求有:fpga型号:xc7vx690t-2ffg1927i;输入时钟:频率80mhz,功率7dbm,相噪-90dbc/hz@1khz;采样时钟:频率320mhz;数据通道上,fpga通过jesd204b与9片ad9680连接;fpga与一组驱动芯片相连,将fpga的1.8v io电平转换为5v电平,完成16个组件共64个数字通道的控制功能以及两个变频模块的控制功能。fpga与两片12t/r光模块(型号htg8503-mh-t001yy)连接,完成数字中频回波信号的传输功能,传输速率10g。

35.图1中,flash为存储器,选用micron公司n25q256a11ef840g,总容量256mbit,支持1.8v电平,可支持x4数据位加载。

36.单端转差分为1组15路单端转差分,通过单端转差分芯片来实现。所述单端转差分芯片,用于将fpga输出的4路单端信号转换为差分信号输出到接口。

37.实施例3:优选的,当adc芯片为单通道adc芯片,1个adc芯片处理1个模拟中频回波信号为1个数字中频回波信号时;fpga,用于同时观测所有adc芯片的快速检测输出引脚fd的状态波形中的多帧时钟信号波形、若第i个adc芯片的多帧时钟信号波形与其它adc芯片的多帧时钟信号波形相比存在延时,则等待第i个adc芯片的输出周期完成后,再一起发送处理后的光模块所需格式数据至光模块,完成第二次同步。

38.实施例4:优选的,还包括设置有可编程阈值的可编程阈值检测器(附图未示意),可编程阈值检测器,用于对所有adc芯片的快速检测输出引脚fd_a或/和快速检测输出引脚fd_b引脚的状态波形中的输入信号功率波形进行监控,若输入信号功率波形超过可编程阈值,可编程阈值检测器输出调低adc系统增益的控制信号至adc芯片。

39.以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。