用于多通道dram的动态同步刷新控制器和动态同步刷新控制方法

技术领域

1.本发明主要涉及到多核处理器的设计领域,特指一种用于多通道dram的动态同步刷新控制器和动态同步刷新控制方法。

背景技术:

2.dram存储器由于工艺集成度高、集中访问速率快等原因,一直被大规模用作处理器的外部存储器。在gpu(graphic processing unit)、dsp(digital signal processing)等高性能计算中,ddr(double data rate)存储器、gddr(graphic double data rate)存储器和lpddr(low power double data rate)存储器等dram存储体得到了广泛应用;近些年还产生了例如hbm(hight bandwidth memory)、hmc(hybrid memroy cube)等新兴的dram类存储体应用。

3.dram的存储单元主要部件是电容,一个主要的缺点是数据保持期间电容会缓慢漏电。因此dram存储体需要定期进行充电维护,使电容所处电平可保证正确读写。这种操作一般称为刷新。定期的刷新是dram控制器的必备功能,完成一次刷新通常需要成百个时钟周期不等;同时按jedec规定,一般情况下在64ms内所有的单元都必须刷一遍。刷新期间dram不能提供读写服务。因此,所有的dram类存储体都有周期性的不可服务时间。

4.另一方面,为提高供数能力,高性能计算中往往采用以多通道dram存储器为外存的复杂的多级存储层次;并采用多种结构的内核、数据搬移机制(如各种dma)在多个dram存储体通道之间进行复杂的数据搬移,期望充分利用dram提供的带宽以提供更强大的外存访问带宽。同时,多核协作是高性能计算中的常用模式,各通道dram长期、稳定提供均衡的数据服务能力是很多高性能算法性能发挥的关键之一。

5.另外,特制的dma多核dma等数据搬移机制也希望多通道dram能稳定提供类似的协调一致的服务。

6.dram的刷新是在soc(system-on-a-chip,片上系统)的dram控制器的控制下完成的。每个通道的dram及dram控制器因其物理延迟有所区别,刷新和校准带来的不可服务时间间隙的出现时刻会随着工作时间的推移而在dram通道间产生偏斜,从而导致多通道dram整体不可服务时间延长,提供数据服务时间缩短,计算部件性能下降。因此,必须在运行时、周期地对多通道dram的不可服务时间进行动态修正,使其不可服务时间协调一致。

7.有从业者在中国专利申请(201610194968.1)中提出了一种dram刷新控制器及多通道dram同步刷新方法,可以对多通道的dram刷新执行同步刷新。但是该技术方案只能在dram完成初始化之后进行一次同步,并没有公开随着计算时间的推移,多个dram通道失调之后如何解决同步刷新的问题。

技术实现要素:

8.本发明所解决的技术问题在于:针对现有技术存在的问题,提供一种结构简单、成

本低廉、易实现和推广、可极大降低并行程序的用于多通道dram的动态同步刷新控制器和动态同步刷新控制方法。

9.为解决上述技术问题,本发明采用以下技术方案:

10.一种用于多通道dram的动态同步刷新控制器,其包括:

11.总线接口,用于提供soc主机对dram同步实时刷新控制器的访问功能,用于提供与dram通道控制器之间信息通信功能;

12.控制寄存器组,包括周期更新标志寄存器r0、刷新周期寄存器r1、刷新计数器c0、通道偏差容限寄存器d0;

13.同步刷新控制器,用来完成对通道dram控制器的刷新功能的禁止和使能,设置通道dram控制器的刷新周期和刷新计数器,控制向dram通道控制器发送强制刷新请求;

14.刷新监控单元,用来根据总线接口收集的各dram通道控制器的刷新状态,实时监控各通道dram的刷新状态,计算各通道刷新不可服务间隙出现时间,并与控制寄存器组进行实时对比,并将比较结果实时反馈给同步刷新控制器。

15.作为本发明方法的进一步改进:所述dram通道控制器用来进行dram访问协议转换、dram刷新和校准控制,并提供从机接口、服务soc片上总线访问请求。

16.作为本发明方法的进一步改进:所述总线接口用来支持在多个dram通道控制器之间广播请求的功能。

17.作为本发明方法的进一步改进:所述周期更新标志寄存器r0用于控制将刷新周期寄存器r1中的值更新到刷新控制状态机;所述刷新周期寄存器r1用于保存用户设置的刷新命令的发送周期;所述刷新计数器c0用于同步所有dram通道控制器的刷新计数器;所述通道偏差容限寄存器d0用于设置触发动态同步刷新控制的通道偏差阈值。

18.作为本发明方法的进一步改进:所述同步刷新控制器包含刷新状态机,根据周期更新标志寄存器r0的控制完成对通道dram控制器的刷新功能的禁止和使能,设置通道dram控制器的刷新周期和刷新计数器,控制向dram通道控制器发送强制刷新请求。

19.作为本发明方法的进一步改进:所述刷新监控单元,根据总线接口收集的各dram通道控制器的刷新状态,实时监控各通道dram的刷新状态,计算各通道刷新不可服务间隙出现时间,并与通道偏差容限寄存器d0进行实时对比,并将比较结果实时反馈给同步刷新控制单元。

20.本发明提供一种基于上述dram动态刷新控制器的多通道dram动态同步刷新控制方法,其包括:

21.步骤s1:系统初始化;

22.步骤s2:开启同步刷新;

23.步骤s3:程序执行及监控刷新偏差;所有dram的刷新周期已经处于同步状态,进入多核处理器的正常计算过程;同时,监控每个通道dram控制器的刷新命令,测算dram通道之间的刷新偏差;当刷新偏差大于预设的容限d0的时候,转入步骤s4,否则停留在步骤s3;

24.步骤s4:实时动态同步刷新。

25.作为本发明的进一步改进:所述步骤s1的流程包括:

26.步骤s101:设定通道间刷新间歇偏差容限;

27.步骤s102:通过soc系统的dram控制器完成dram以及dram控制器本身的初始化,

dram子系统处于可工作状态,但关闭读写请求接收端口。

28.作为本发明的进一步改进:所述步骤s2的流程包括:

29.步骤s201:关闭所有通道dram控制器的刷新功能;

30.向刷新周期寄存器r1中写入0,并向更新标志寄存器r0写入“1”,此时刷新计数器c0将重新采用刷新周期;刷新控制器将向通道dram控制器发出禁止刷新dram请求;

31.步骤s202:同步开启所有dram通道控制器的刷新功能。

32.作为本发明的进一步改进:

33.步骤s401:启动一次强制刷新;

34.步骤s402:广播更新所有dram控制器的刷新周期,并强制所有通道刷新计数器重新采样,这会导致后续刷新间隔时间得以同步;

35.步骤s403:跳转到步骤s3。

36.与现有技术相比,本发明的优点在于:本发明的dram动态同步刷新控制器及多通道dram动态同步刷新方法,可以动态跟踪多通道dram的刷新不可服务时间的相对偏差情况,动态调整同步刷新,提高系统总体性能。本发明的整体硬件结构简单,成本低廉,易实现和推广,可容易在dram通道控制器中集成。

附图说明

37.图1是典型的多通道dram的多核soc结构示意图。

38.图2是本发明dram动态刷新控制器的结构示意图。

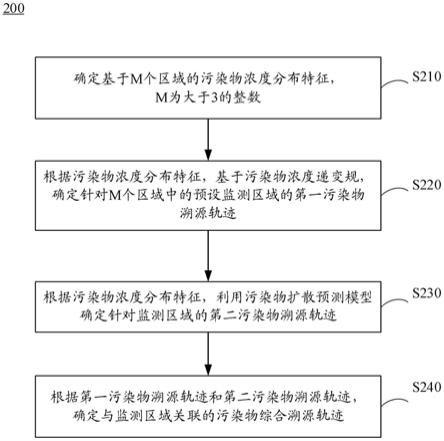

39.图3是本发明方法的流程示意图。

40.图4是采用本发明方法和典型dma访问4个dram的流程对比示意图。

具体实施方式

41.以下结合具体实施例和附图对本发明作进一步详细说明。

42.本发明的技术方案主要适用于多核soc,图1是典型的多dram通道的片上多核soc系统,其包含了m个内核(核1-核m),n个dram通道控制器(dcc1-dccn)以及其他的片内存储器和io,m个内核通过片上互连与dram通道控制器、片内存储器以及其他io进行数据通信。每个dram通道控制器控制一个dram存储器的工作,包括初始化、读写、刷新等功能。

43.如图2所示,本发明的用于多通道dram的动态同步刷新控制器,包括:

44.总线接口,用于提供soc主机对dram同步实时刷新控制器的访问功能,用于提供与dram通道控制器之间信息通信功能;进一步,还可用来收集dram通道控制器的刷新信息、传递dram通道刷新请求等;

45.控制寄存器组,包括周期更新标志寄存器r0、刷新周期寄存器r1、刷新计数器c0、通道偏差容限寄存器d0;

46.同步刷新控制器,用来完成对通道dram控制器的刷新功能的禁止和使能,设置通道dram控制器的刷新周期和刷新计数器,控制向dram通道控制器发送强制刷新请求;

47.刷新监控单元,用来根据总线接口收集的各dram通道控制器的刷新状态,实时监控各通道dram的刷新状态,计算各通道刷新不可服务间隙出现时间,并与控制寄存器组进行实时对比,并将比较结果实时反馈给同步刷新控制器。

48.在具体应用实例中,所述总线接口用来支持在多个dram通道控制器之间广播请求的功能。

49.在具体应用实例中,根据实际应用的需要,所述soc主机可以是soc中某个处理核,也可以是某个主动外围设备等可以主动访问soc从机的设备。

50.在具体应用实例中,所述dram通道控制器具备dram访问协议转换、dram刷新和校准控制,并提供从机接口、服务soc片上总线访问请求。

51.在具体应用实例中,所述周期更新标志寄存器r0用于控制将刷新周期寄存器r1中的值更新到刷新控制状态机;所述刷新周期寄存器r1用于保存用户设置的刷新命令的发送周期;所述刷新计数器c0用于同步所有dram通道控制器的刷新计数器;所述通道偏差容限寄存器d0用于设置触发动态同步刷新控制的通道偏差阈值。

52.在具体应用实例中,所述同步刷新控制器包含刷新状态机,根据周期更新标志寄存器r0的控制完成对通道dram控制器的刷新功能的禁止和使能,设置通道dram控制器的刷新周期和刷新计数器,控制向dram通道控制器发送强制刷新请求。

53.在具体应用实例中,所述刷新监控单元,根据总线接口收集的各dram通道控制器的刷新状态,实时监控各通道dram的刷新状态,计算各通道刷新不可服务间隙出现时间,并与通道偏差容限寄存器d0进行实时对比,并将比较结果实时反馈给同步刷新控制单元。

54.如图3所示,本发明进一步提供一种基于上述dram动态刷新控制器的多通道dram动态同步刷新控制方法,其步骤包括:

55.步骤s1:系统初始化;

56.步骤s2:开启同步刷新;

57.步骤s3:程序执行及监控刷新偏差;所有dram的刷新周期已经处于同步状态,进入多核处理器的正常计算过程;同时,监控每个通道dram控制器的刷新命令,测算dram通道之间的刷新偏差。当刷新偏差大于预设的容限d0的时候,转入步骤s4,否则停留在步骤s3;

58.步骤s4:实时动态同步刷新。

59.作为本发明方法的进一步改进:所述步骤1)中,soc主机依次完成所有dram通道控制器的相关配置和dram的初始化工作;此时,所有dram通道控制器处于非严格同步刷新和校准状态,即对dram发生的刷新和校准发生在不同的时刻。

60.作为本发明方法的进一步改进:所述步骤2.2)中,首先配置所有dram通道控制器的刷新周期寄存器,要求刷新周期相同;然后采用广播的方式所有dram通道控制器的更新标志寄存器中写入“1”,重新启动所有的周期刷新机制。

61.在具体应用实例中,所述步骤s1的流程包括:

62.步骤s101:设定通道间刷新间歇偏差容限。

63.步骤s102:通过soc系统的dram控制器完成dram以及dram控制器本身的初始化,dram子系统处于可工作状态,但关闭读写请求接收端口。

64.在具体应用实例中,所述步骤s2的流程包括:

65.步骤s201:关闭所有通道dram控制器的刷新功能;

66.向刷新周期寄存器r1中写入0,并向更新标志寄存器r0写入“1”,此时刷新计数器c0将重新采用刷新周期;刷新控制器将向通道dram控制器发出禁止刷新dram请求;

67.步骤s202:同步开启所有dram通道控制器的刷新功能。

68.在具体应用实例中,所述步骤s4的流程包括:

69.步骤s401:启动一次强制刷新;

70.步骤s402:广播更新所有dram控制器的刷新周期,并强制所有通道刷新计数器重新采样,这会导致后续刷新间隔时间得以同步;

71.步骤s403:跳转到步骤s3。

72.如图4所示,为典型dma访问4个dram通道的两种流程对比示意图示意图。其中图4(a)是未进行多个dram通道控制器间刷新和校准同步的dma访问过程。dma引擎并行的向4个dram发送访问请求,访问请求的目的地以“之”字形在四个dram中平均分布。

73.假定dma一共要执行16组访问请求,每一组请求包含n个独立的请求。dma发送请求的时候必须按照顺序发送,前面的请求未发送出去将阻塞后面请求的发送,时间槽i对应一组请求的执行时间。

74.其执行过程如下:

75.·

时间槽i:dcc0-3依次执行dma的请求。

76.·

时间槽i 1:dcc0需要对dram0执行刷新,无法继续接收请求。dma对后续dcc1-3的请求也因此阻塞。

77.·

时间槽i 2:dcc0完成刷新和校准,正常执行第4组请求,dcc1-3也可分别继续执行第5、第6、第7组请求。

78.·

时间槽i 3:dcc0执行第8组请求,而dcc1到了刷新和校准时间,暂时挂起dma的第9组请求。dcc2和dcc3也只能进入等待状态。

79.·

时间槽i 4:dcc2和dcc3挂起dma导致dcc0继续等待;dcc1完成刷新和校准,正常执行第9组请求;dcc2进入刷新和校准周期,dcc3进入等待状态。

80.·

时间槽i 5:dcc3挂起dma导致dcc0和dcc1继续等待;dcc1完成刷新和校准,正常执行第10组请求;dcc3进入刷新和校准周期。

81.·

时间槽i 6:由于dma需要等dcc3将挂起的dma请求完成并释放dma通道后,才能继续放松后续请求,所以dcc0-2仍然处于等待状态;dcc3执行第11组dma请求。

82.·

时间槽i 7:dcc0-3进入正常执行阶段。

83.参见图4(b),是执行过多dram通道控制器间刷新和校准同步的dma访问过程,其执行过程如下:

84.·

时间槽i:dcc0-3依次执行dma的请求。

85.·

时间槽i 1:dcc0-3都需要对dram0执行刷新,无法继续接收请求。dma请求被挂起。

86.·

时间槽i 2:dcc0-3同步完成刷新和校准,继续正常执行第4-7组请求。

87.·

时间槽i 3:正常执行第8-11组请求。

88.·

时间槽i 4:正常执行第12-15组请求。

89.从图4(a)和图4(b)的执行过程可以看出,未采用本发明的方法的dma执行过程将需要8个时间槽才能完成该dma任务,而采用了本发明的方法的相同dma任务则只需要5个时间槽。

90.以上仅是本发明的优选实施方式,本发明的保护范围并不仅局限于上述实施例,凡属于本发明思路下的技术方案均属于本发明的保护范围。应当指出,对于本技术领域的

普通技术人员来说,在不脱离本发明原理前提下的若干改进和润饰,应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。