1.本发明涉及半导体晶片及其制造方法。

背景技术:

2.在专利文献1中公开了在蓝宝石或碳化硅基板上使具有与基板不同的晶格常数的半导体层生长的方法。在该方法中,在基板上的规定部位形成具有用于使半导体层选择性地生长的开口部的层,并通过开口部使基板的规定部位露出。接下来,在通过开口部而露出的基板的表面上选择性地使半导体层异质外延生长。

3.专利文献1:日本特开平10-135140号公报

4.当在硅基板生长氮化镓时,存在因两者的晶格常数之差引起基板翘曲的情况。在专利文献1的方法中,通过分割半导体层,能够减少基板翘曲。然而,在专利文献1的方法中,有可能无法充分地抑制翘曲。由此,曝光工序等之后的工序有可能变得困难。

技术实现要素:

5.本发明是为了解决上述问题而做出的,其目的在于得到一种能够抑制基板的翘曲的半导体晶片及其制造方法。

6.本技术的发明所涉及的半导体晶片的制造方法具备:第一工序,在硅基板的上表面形成被分割成多个小区块的氮化镓生长层;和第二工序,用绝缘膜填埋该多个小区块之间,该绝缘膜对该硅基板施加与该氮化镓生长层对该硅基板施加的应力相反方向的应力。

7.本技术的发明所涉及的半导体晶片具备:硅基板;氮化镓生长层,设置于该硅基板的上表面,并被分割成多个小区块;以及绝缘层,设置于该硅基板的上表面,并填埋该多个小区块之间,该绝缘层对该硅基板施加与该氮化镓生长层对该硅基板施加的应力相反方向的应力。

8.在本技术的发明所涉及的半导体晶片的制造方法中,通过绝缘膜能够抑制硅基板的翘曲。

9.在本技术的发明所涉及的半导体晶片中,通过绝缘层能够抑制硅基板的翘曲。

附图说明

10.图1是实施方式1所涉及的半导体晶片的剖视图。

11.图2是表示在硅基板形成有热氧化膜的状态的俯视图。

12.图3是表示去除了热氧化膜的状态的俯视图。

13.图4是表示去除了热氧化膜的状态的剖视图。

14.图5是表示形成有绝缘膜的状态的剖视图。

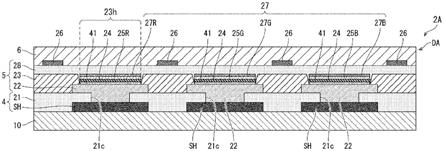

15.图6是实施方式2所涉及的半导体晶片的剖视图。

16.图7是说明实施方式2所涉及的半导体晶片的制造方法的剖视图。

17.图8是表示使多个小区块的上表面露出的状态的剖视图。

18.图9是实施方式3所涉及的半导体晶片的剖视图。

19.图10是实施方式4所涉及的半导体晶片的剖视图。

具体实施方式

20.参照附图对本发明的实施方式所涉及的半导体晶片及其制造方法进行说明。有时对相同的或对应的构成要素标注相同的附图标记,省略重复说明。

21.实施方式1

22.图1是实施方式1所涉及的半导体晶片100的剖视图。半导体晶片100具备硅基板10。在硅基板10的上表面设置有氮化镓生长层12。氮化镓生长层12被分割成多个小区块13。多个小区块13相互分离。氮化镓生长层例如为包含in

1-x-y

ga

x

alyn层的多层膜。这里,0≤x≤1、0≤y≤1。

23.在硅基板10的上表面设置有绝缘膜14。绝缘膜14填埋多个小区块13之间。绝缘膜14的厚度例如为1μm以上,且为氮化镓生长层12的厚度以下。绝缘膜14例如为氮化硅膜。绝缘膜14从硅基板10的一端连接到另一端。

24.接下来,对半导体晶片100的制造方法进行说明。首先,在硅基板10的上表面形成热氧化膜16。图2是表示在硅基板10形成有热氧化膜16的状态的俯视图。在热氧化膜16通过光刻而形成格子状的图案。由此,形成格子状的氧化膜。硅基板10的上表面由热氧化膜16划分成多个区域11。

25.接下来,在硅基板10形成氮化镓生长层12。氮化镓生长层12例如通过有机金属气相生长法或分子束外延法形成。由此,在硅基板10中的未被热氧化膜16覆盖的部分形成氮化镓生长层12。即,在多个区域11分别生长多个小区块13。其中,氮化镓生长层12设为包含用于使氮化镓外延生长的缓冲层。

26.其后,去除热氧化膜16。在去除中例如使用氢氟酸。图3是表示去除了热氧化膜16的状态的俯视图。图4是表示去除了热氧化膜16的状态的剖视图。以上是在硅基板10的上表面形成被分割成多个小区块13的氮化镓生长层12的第一工序。

27.接下来,实施用绝缘膜14填埋多个小区块13之间的第二工序。图5是表示形成了绝缘膜14的状态的剖视图。绝缘膜14例如通过cvd(chemical vapor deposition:化学气相沉积)法堆积于硅基板10之上。绝缘膜14形成为与硅基板10紧贴。

28.绝缘膜14对硅基板10施加与氮化镓生长层12对硅基板10施加的应力相反方向的应力。绝缘膜14由对硅基板10施加与氮化镓生长层12相反的应力的材料形成。绝缘膜14例如为氮化硅膜或氧化硅膜。优选为绝缘膜14由对硅基板10施加的应力大的材料形成。

29.通常,氮化硅膜根据成膜条件而能够产生数gpa左右的拉伸应力或压缩应力。虽然取决于制造装置,但在通过等离子体cvd形成的氮化硅膜中能够得到300mpa左右的膜应力,在通过热cvd形成的氮化硅膜中能够得到1gpa左右的膜应力。另外,绝缘膜14也可以通过ecr(electron cyclotron resonance:电子回旋共振)溅射形成。在通过ecr溅射形成的氮化硅膜中,能够得到3gpa左右的膜应力。

30.例如也可以使用sih4和nh3作为工艺气体,通过等离子体cvd形成绝缘膜14。在该情况下,通过使sih4相对于nh3的比率在0.5~2之间变化,能够使膜应力变化至100mpa左右的拉伸应力~300mpa左右的压缩应力。因此,例如通过将sih4相对于nh3的比率设定为0.5以

下,能够从绝缘膜14向硅基板10施加拉伸应力。另外,通过将sih4相对于nh3的比率设定为2以上,能够从绝缘膜14向硅基板10施加拉伸应力。

31.接下来,如图1所示,直到氮化镓生长层12露出为止去除绝缘膜14。绝缘膜14的去除通过干式蚀刻等蚀刻来进行。此时,通过调整蚀刻时间,来调整绝缘膜14的厚度。通常,绝缘膜14越厚,施加到硅基板10的应力越大。因此,通过调整蚀刻时间,能够调整绝缘膜14对硅基板10施加的应力的大小。

32.另外,与绝缘膜14的厚度成比例地能够矫正的翘曲变大。绝缘膜14的厚度也可以由形成有氮化镓生长层12且形成绝缘膜14之前的状态的硅基板10的翘曲量决定。绝缘膜14的厚度也可以设定为在形成有绝缘膜14的状态下硅基板10变得平坦。

33.通常,缓和基板的翘曲所需的绝缘膜的膜厚,取决于氮化镓生长层间的区域的大小或绝缘膜的膜应力的大小。例如,若以1μm的厚度堆积膜应力为1gpa的绝缘膜14,则与不设置绝缘膜14的情况相比,能够矫正数μm~10μm左右的硅基板10的翘曲。这里,将相邻的小区块13所夹的绝缘膜14的宽度相对于小区块13的宽度设定为1/10。另外,硅基板10的厚度设定为625μm。根据以上,通过例如将绝缘膜14的厚度设为1μm以上,能够充分地抑制硅基板10的翘曲。

34.根据以上,形成绝缘膜14。如图3所示,绝缘膜14形成在氮化镓生长层12被去除而硅基板10以格子状露出的部分。即,绝缘膜14形成为格子状。

35.接下来,在从绝缘膜14露出的氮化镓生长层12的表面形成电极等。由此,形成器件。

36.通常,通过使用氮化镓(gan)、氮化镓铝(algan)以及氮化铝(aln)等基于氮化物的半导体材料,能够制作异质结构。因此,这些材料有时用于高频器件、光器件或功率器件的制造。

37.基于氮化物的半导体结构通常通过在碳化硅、蓝宝石或硅基板之上外延生长而制作。特别是硅基板比碳化硅等廉价。因此,能够降低材料成本。

38.这里,通常若在硅基板生长氮化镓则有时基板翘曲。由此,有时在搬运或曝光工序等工序中产生问题。

39.硅的晶格常数为0.5431nm。因此,在硅的(111)面上的原子间隔为0.5431/√2=0.3840nm。与此相对,氮化镓的晶格常数为0.3819nm。氮化镓的晶格间隔比硅窄。因此,硅基板从在(111)面上异质外延生长的氮化镓受压缩应力。

40.另外,硅的线膨胀系数为2.6

×

10

-6k-1

。与此相对,氮化镓的线膨胀系数为5.6

×

10

-6k-1

。通常,氮化镓在800℃以上的高温下生长。因此,在从生长温度降低至室温时,氮化镓收缩得比硅大。因此,硅基板从氮化镓生长层受压缩应力。

41.根据以上,若在硅基板形成氮化镓生长层,则以氮化镓生长层成为内侧的方式产生翘曲。实际上,翘曲的朝向根据外延生长的条件或缓冲层的构成而不同。

42.另外,可以想到通过将氮化镓生长层分割成小区块,分散应力,来减少基板翘曲的方法。但是,在这样的方法中,通常难以完全消除基板的翘曲。例如在4英寸基板中,有可能残留数μm~10μm左右的晶片翘曲。这样的翘曲特别是在需要形成微小图案的栅极曝光工序等中成为问题。

43.与此相对,本实施方式的绝缘膜14对硅基板10施加与氮化镓生长层12对硅基板10

施加的应力相反方向的应力。即,在氮化镓生长层12对硅基板10施加压缩应力的情况下,使用对硅基板施加拉伸应力的膜作为绝缘膜14。另外,在氮化镓生长层12对硅基板10施加拉伸应力的情况下,使用对硅基板施加压缩应力的膜作为绝缘膜14。

44.由此,通过绝缘膜14能够抵消硅基板10从氮化镓生长层12受到的应力。因此,能够缓和硅基板10的翘曲。在本实施方式中,可得到将氮化镓生长层12分割成小区块13来分散应力的效果、和基于绝缘膜14实现的应力的抵消效果这两者。因此,能够抑制晶片的翘曲,容易地实施曝光工序。

45.另外,通过绝缘膜14的厚度,能够调节对硅基板10施加的应力。绝缘膜14的厚度能够通过蚀刻时间来调节。因此,能够容易地使硅基板10平坦。

46.此外,将图2所示的热氧化膜16形成得厚来抑制翘曲是困难的。在该情况下,在外延生长之前厚的热氧化膜16形成于硅基板10。此时,由于热氧化膜16的膜应力大,所以有可能在外延生长的开始时晶片成为大幅翘曲的状态。因此,外延生长工序有可能变得困难。

47.因此,热氧化膜16需要形成得薄以抑制硅基板10大幅翘曲。与此相对,绝缘膜14形成得比热氧化膜16厚以对硅基板10施加大的应力。

48.作为本实施方式的变形例,图3所示的去除氮化镓生长层12的区域并不局限于格子状。去除了氮化镓生长层12的区域只要能够将氮化镓生长层12分割成多个小区块13,也可以为其它形状。考虑到通过形成绝缘膜14来对硅基板10施加应力,去除了氮化镓生长层12的区域优选为在纵向和横向上从硅基板10的一端贯穿到另一端。

49.另外,第一工序也可以如下这样进行。首先,通过有机金属气相生长法或分子束外延法在硅基板10的整个上表面形成氮化镓生长层12。其后,在氮化镓生长层12之上形成光致抗蚀剂等掩模层。接下来,使用掩模层对氮化镓生长层12进行蚀刻直到硅基板10露出为止。由此,硅基板10以格子状露出,氮化镓生长层12被分割成多个小区块13。接下来,去除掩模层。

50.这些变形能够对以下实施方式所涉及的半导体晶片及其制造方法适当地应用。此外,对于以下实施方式所涉及的半导体晶片及其制造方法,由于与实施方式1的共通点多,因此围绕与实施方式1的不同点进行说明。

51.实施方式2

52.图6是实施方式2所涉及的半导体晶片200的剖视图。在半导体晶片200中,绝缘膜214的结构与半导体晶片100不同。在绝缘膜214且在多个小区块13中的相互相邻的一对小区块13之间形成有凹部215。

53.接下来,对半导体晶片200的制造方法进行说明。第一工序与实施方式相同。接下来,实施第二工序。图7是说明实施方式2所涉及的半导体晶片的制造方法的剖视图。首先,用绝缘膜214覆盖硅基板10的上表面、和多个小区块13的各个侧面以及上表面。

54.绝缘膜214沿着硅基板10和多个小区块13而形成。在绝缘膜214的表面形成有反映了多个小区块13的形状的凹凸。此时,在绝缘膜214中的相互相邻的一对小区块13之间的部分形成有凹部215。绝缘膜214中的覆盖小区块13的侧面的部分的厚度为,被相邻的小区块13夹住的区域的宽度的1/2以下。

55.接下来,涂敷抗蚀剂218。抗蚀剂218以填埋凹部215的方式设置于绝缘膜214之上。抗蚀剂218的上表面是平坦的。抗蚀剂218具有在抗蚀剂218的上表面不反映绝缘膜214的表

面的凹凸的厚度。

56.接下来,实施蚀刻工序。由此使多个小区块13的上表面从绝缘膜214露出。图8是表示使多个小区块13的上表面露出的状态的剖视图。在蚀刻工序中,通过干式蚀刻连同抗蚀剂218一起去除绝缘膜214直到氮化镓生长层12露出为止。由此,去除抗蚀剂218中的设置在比多个小区块13的上表面靠上方的部分、和绝缘膜214中的设置在比多个小区块13的上表面靠上方的部分。

57.此时,优选使用抗蚀剂218与绝缘膜214的蚀刻速率变得相等的蚀刻条件。通常在氧化硅膜以及氮化硅膜中,可以找出与抗蚀剂成为相同的蚀刻速率的蚀刻条件。由此,能够高精度地使多个小区块13的上表面露出。

58.在蚀刻工序之后,去除抗蚀剂218中的填埋凹部215的部分。根据以上,形成绝缘膜214。

59.若以覆盖多个小区块13的方式设置绝缘膜214,则如图7所示,有时在绝缘膜214的表面形成格子状的凹凸。若不涂敷抗蚀剂218,而是与实施方式1同样地仅将绝缘膜214蚀刻到氮化镓生长层12露出为止,则硅基板10之上的绝缘膜214也被蚀刻。因此,有可能绝缘膜214几乎不残留在硅基板10上。

60.在绝缘膜214使用覆盖性(coverage)为0的膜的极端的例子中,在氮化镓生长层12之上和硅基板10之上,绝缘膜214的厚度变得相同。因此,若对绝缘膜214蚀刻至氮化镓生长层12露出为止,则硅基板10之上的绝缘膜214也被完全去除。

61.与此相对,在本实施方式中,即使在绝缘膜214的表面形成有凹凸的情况下,也能够在硅基板10之上厚厚地残留绝缘膜214。因此,通过绝缘膜214能够充分地抑制硅基板10的翘曲。

62.实施方式3

63.图9是实施方式3所涉及的半导体晶片300的剖视图。半导体晶片300的硅基板310的结构与半导体晶片100不同。在硅基板310的上表面侧形成有多个凸部310a。多个小区块13分别设置于多个凸部310a之上。

64.接下来,对半导体晶片300的制造方法进行说明。首先,在硅基板310的上表面形成氮化镓生长层12。在该状态下,硅基板310的上表面是平坦的。另外,氮化镓生长层12形成于硅基板310的整个上表面。

65.接下来,实施蚀刻工序。在蚀刻工序中,首先,在氮化镓生长层12之上形成光致抗蚀剂等掩模层。接下来,使用掩模层通过蚀刻去除氮化镓生长层12的一部分。蚀刻例如为干式蚀刻。由此,氮化镓生长层12被去除成格子状,硅基板310露出。通过蚀刻工序,氮化镓生长层12被分割成多个小区块13。

66.另外,在硅基板310露出之后也继续进行蚀刻。由此,硅基板310被蚀刻,而在硅基板310形成槽。即,在硅基板310的上表面侧形成多个凸部310a。

67.接下来,形成绝缘膜14。绝缘膜14填埋相邻的凸部310a之间。之后的工序与实施方式1相同。

68.在本实施方式中,能够与形成于硅基板310的槽的深度对应地增厚绝缘膜14。因此,能够通过绝缘膜14对硅基板310施加比实施方式1大的应力。另外,即使在氮化镓生长层12的厚度比为了抑制翘曲所需的绝缘膜14的厚度薄的情况下,也能够确保绝缘膜14的厚

度。

69.实施方式4

70.图10是实施方式4所涉及的半导体晶片400的剖视图。在本实施方式中,在硅基板10的上表面设置有热氧化膜16。在热氧化膜16之上设置有绝缘膜14。热氧化膜16和绝缘膜14形成绝缘层。

71.接下来,对半导体晶片400的制造方法进行说明。直到使氮化镓生长层12生长的工序为止,与实施方式1相同。在本实施方式中,不去除热氧化膜16。接下来,在热氧化膜16之上形成绝缘膜14。之后的工序与实施方式1相同。

72.在本实施方式中,由于不去除热氧化膜16,所以能够简化制造工序。另外,在热氧化膜16施加用于矫正硅基板10的翘曲的应力的情况下,能够将热氧化膜16有效地用于翘曲的抑制。

73.此外,在各实施方式中说明的技术特征也可以适当地组合来使用。

74.附图标记说明

75.10...硅基板;11...区域;12...氮化镓生长层;13...小区块;14...绝缘膜;16...热氧化膜;100、200...半导体晶片;214...绝缘膜;215...凹部;218...抗蚀剂;300...半导体晶片;310...硅基板;310a...凸部;400...半导体晶片。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。