1.本发明涉及一种快速报文处理方法,具体说是一种用于工业网络、基于硬件实现的、具有时间确定性以及传输低延时等特性的报文处理电路及方法。

背景技术:

2.在工业网络的应用场景中,报文处理的确定性、低延时指标是工业网络的重要指标,该指标与工业网络系统的性能密切相关。工业网络中报文处理的延时指的是工业网络中某节点从接收到其他节点的报文到开始发送本节点的报文所耗费的时间;工业网络中报文处理的确定性指的是上述延时的延时抖动程度保持一定的稳定性。网络节点间的延时及确定性与工业网络系统的性能具有较大的相关性,决定了工业网络系统的响应速度、同步性能、节点数量、最小循环周期等技术指标。

3.传统的工业网络报文处理方法是:报文无论是否为当前节点的报文,均要经过当前节点中的处理器处理之后,再转发给下一节点。报文在节点处理的过程中,需要由处理器或dma处理,经存储器存储转发等过程,从而引入额外了较大的延时,并且延时抖动的可控性较差。本专利所述的报文处理方法采用硬件处理结构、报文由接收端口经固定延时直接由发送端口转出。对比于本专利所述的硬件报文处理方案,传统的处理方法在时延及确定性方面性能较差,对于具有强实时性要求的工业网络应用场景将不再适用;同时,网络侧的时钟与网络节点本地的时钟不同步也使得数据传输延时的确定性无法保证。

技术实现要素:

4.针对传统工业网络报文处理中的不足,本发明的目的是提供一种面向具有强实时性需求的工业网络应用场景的、基于硬件的,用于工业网络节点的低延时确定性报文处理电路及方法。该电路对传统工业网络报文处理电路包含两项改进:第一是增加了数字锁相环电路,在节点接收到报文后以及节点发送报文前均进行时钟相位修正;第二是采用硬件处理结构、增加了快速转发电路,对原本需要经过存储器存储转发结构处理的报文直接转发至下一节点。

5.本发明为实现上述目的所采用的技术方案是:

6.一种确定性低延时报文处理方法,包括以下步骤:

7.接收电路接收来自网络侧的串行总线接收信号并提取工业网络时钟,将工业网络时钟输出至数字锁相环;

8.数字锁相环接收工业网络时钟和本地的本地参考时钟,生成本地工作时钟和发送电路时钟,将本地工作时钟分别发送给接收电路、本地报文交互处理模块,将发送电路时钟发送给发送电路;

9.接收电路接收本地工作时钟,将串行总线接收信号向本地工作时钟同步,生成串行总线接收信号1,将串行总线接收信号1发送给本地报文交互处理模块;

10.本地报文交互处理模块对串行总线接收信号1进行处理,生成串行总线发送信号1

并发送给发送电路;

11.发送电路接收到串行总线发送信号1,结合发送电路时钟,将串行总线发送信号发送至工业网络。

12.所述本地工作时钟与工业网络时钟的相位差保持固定,所述发送电路时钟与工业网络时钟的相位差保持固定。

13.所述本地报文交互处理模块对串行总线接收信号1的处理包括以下步骤:

14.校验检查电路接收串行总线接收信号1,生成校验指示信号并发送至本地报文交互处理模块外部,即本节点内其他功能模块;

15.接收串并转换电路接收串行总线接收信号1和来自控制状态机的控制信号1,将串行总线接收信号1转换为并行接收数据,发送至本地报文交互处理模块外部,即本节点内其他功能模块,同时生成接收时间戳锁存信号,发送至本地报文交互处理模块外部,即本节点内其他功能模块,接收串并转换电路在接收到来自控制状态机的控制信号1后,发送并行接收数据至控制状态机;

16.控制状态机接收并行接收数据,生成接收数据字段指示,将接收数据字段指示发送至本地报文交互处理模块外部,即本节点内其他功能模块,将控制信号1发送至接收串并转换电路,将控制信号2发送至发送并串转换电路,将控制信号3发送至快速转发电路,将控制信号4发送至校验生成电路;

17.发送并串转换电路在接收到控制信号2后,将来自本地报文交互处理模块外部的本地并行发送数据转换成本地发送数据,发送给快速转发电路,同时生成发送时间戳锁存信号,发送至本地报文交互处理模块外部,即本节点内其他功能模块;

18.快速转发电路根据控制信号3选择处理串行总线接收信号1或本地发送数据,将其作为发送数据发送至校验生成电路;

19.校验生成电路接收到发送数据后,根据控制信号4,生成发送校验数据并发送至快速转发电路;

20.快速转发电路根据控制信号3,将串行总线接收信号1,或者本地发送数据加上发送校验数据后,作为串行总线发送信号1发送至发送电路。

21.通过奇偶校验、累加和校验或循环冗余校验中任意一种方法生成所述校验指示信号。

22.一种确定性低延时报文处理系统,包括:接收电路、数字锁相环、本地报文交互处理模块以及发送电路,其中:

23.接收电路,用于接收来自网络侧的串行总线接收信号并提取工业网络时钟,将工业网络时钟输出至数字锁相环以及接收本地工作时钟,将串行总线接收信号向本地工作时钟同步,生成串行总线接收信号1,将串行总线接收信号1发送给本地报文交互处理模块;

24.数字锁相环,用于接收工业网络时钟和本地的本地参考时钟,生成本地工作时钟和发送电路时钟,将本地工作时钟分别发送给接收电路、本地报文交互处理模块,将发送电路时钟发送给发送电路;

25.本地报文交互处理模块,用于串行总线接收信号1进行处理,生成串行总线发送信号1并发送给发送电路;

26.发送电路,用于接收到串行总线发送信号1,结合发送电路时钟,将串行总线发送

信号发送至工业网络。

27.所述本地报文交互处理模块包括:检验检查电路、接收串并转换电路、控制状态机、发送并串转换电路、快速转发电路以及校验生成电路,其中:

28.校验检查电路,用于接收串行总线接收信号1,并生成校验指示信号并发送至本地报文交互处理模块外部;

29.接收串并转换电路,用于接收串行总线接收信号1和来自控制状态机的控制信号1,将串行总线接收信号1转换为并行接收数据,发送至本地报文交互处理模块外部,同时生成接收时间戳锁存信号,发送至本地报文交互处理模块外部,接收串并转换电路在接收到来自控制状态机的控制信号1后,发送并行接收数据至控制状态机;

30.控制状态机,用于接收并行接收数据,生成接收数据字段指示、控制信号1、控制信号2、控制信号3、控制信号4,将接收数据字段指示发送至本地报文交互处理模块外部,即本节点内其他功能模块,将控制信号1发送至接收串并转换电路,用于使能串并转换,将控制信号2发送至发送并串转换电路,用于控制本地并行发送数据到本地发送数据的转换,将控制信号3发送至快速转发电路,用于控制串行总线接收信号1、本地发送数据、发送校验数据的多路选择,将控制信号4发送至校验生成电路,用于控制生成发送校验数据;

31.发送并串转换电路,用于在接收到控制信号2后,将来自本地报文交互处理模块外部的本地并行发送数据转换成本地发送数据,发送给快速转发电路,同时生成发送时间戳锁存信号,发送至本地报文交互处理模块外部;

32.快速转发电路,用于根据控制信号3选择处理串行总线接收信号1或本地发送数据,将其作为发送数据发送至校验生成电路,以及根据控制信号3,将串行总线接收信号1,或者本地发送数据加上发送校验数据后,作为串行总线发送信号1发送至发送电路。

33.校验生成电路,用于在接收到发送数据后,根据控制信号4,生成发送校验数据并发送至快速转发电路。

34.本发明具有以下有益效果及优点:

35.1.本发明电路面向工业网络,基于硬件实现,可以提供低延时和低延时抖动。

36.2.本发明电路采用数字锁相环、接收电路等电路结构,可以将串行总线接收信号向本地工作时钟同步,可以提供更精确的信号处理延时。

37.3.本发明采用快速转发电路、控制状态机等电路结构,针对无需工业网络节点处理、仅需转发给其他节点的报文可快速送至发送电路,提供较低的、固定的报文转发延时。

38.4.本发明电路采用数字锁相环、发送电路等电路结构,可以将串行总线发送信号1的时钟调整为与工业网络时钟有固定相位差的信号,从而避免本地时钟漂移对工业网络数据传输产生的影响。

附图说明

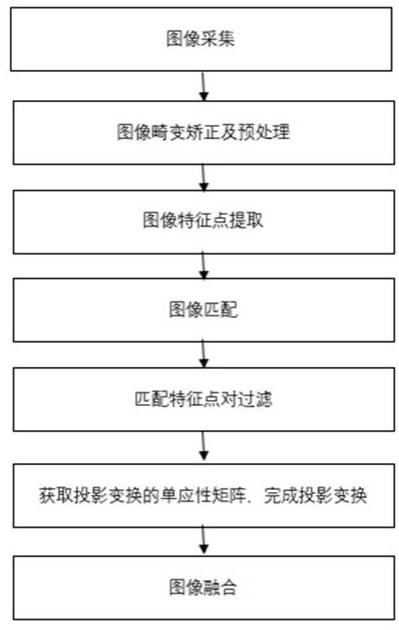

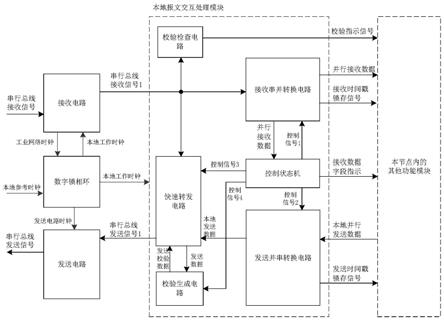

39.图1是确定性低延时报文处理电路结构图;

40.图2是工业网络电路延时示意图;

41.图3是快速转发电路生成报文示意图;

42.图4是快速转发电路内部工作原理图;

43.图5是控制状态机内部工作原理图;

44.图6是状态机1内部状态转移图。

具体实施方式

45.下面结合附图及实施例对本发明做进一步的详细说明。

46.当工业网络一侧的异步串行信号经过接收电路时,接收电路会对该信号进行时钟采样,将该串行信号与本地工作时钟进行时钟同步。

47.经过时钟同步后的串行信号送至快速转发电路,另一路通过串并转换电路送至网络节点本地;本地的发送数据可以通过并串转换电路变成串行信号送至快速转发电路,在控制状态机的指示信号下,快速转发电路可以选择直接转发来自网络的串行信号,亦可以发送本地的串行数据,同时控制校验生成电路将这两种串行数据进行校验,并生成校验数据。

48.发送电路根据数字锁相环给出的时钟信号,对快速转发电路发送出的串行信号进行相位调整,形成与工业网络时钟有固定相位差的信号,随后发送至工业网络。

49.本发明电路的原理描述如下:

50.所述接收电路的作用是对工业网络侧的异步串行信号进行时钟采样,提取到工业网络侧的时钟信号,以及将该异步串行信号与本地工作时钟进行时钟同步。

51.所述数字锁相环的作用是根据本地参考时钟和工业网络时钟,生成与工业网路时钟存在固定相偏的本地工作时钟信号及发送电路时钟信号。

52.所述快速转发电路的作用类似一个选择器,在状态控制机发出的控制信号3的指示下,可以选择发送来自接收电路的串行总线接收信号1或来自发送并串转换电路的本地发送数据,以及这两种数据相对应的校验数据。

53.所述接收串并转换电路的作用是将来自接收电路的串行总线接收信号1转换为多路并行信号,将转换后的并行接收数据发送给本地处理器,以及将串行总线接收信号1进入接收串并转换电路的时刻对该时间进行锁存,生成接收时间戳锁存信号。

54.所述发送并串转换电路的作用是将来自本地的本地并行发送数据进行并串转换,将并串转换后的数据作为本地发送数据发送给快速转发电路,并在发送时刻生成发送时间戳锁存信号。

55.所述控制状态机的作用是接收来自接收串并转换电路的并行接收数据,然后生成接收数据字段指示;通过控制信号1、控制信号2、控制信号3、控制信号4分别控制接收串并转换电路的串并转换、控制发送并串转换电路的并串转换、控制快速转发电路的发送数据选择、控制校验生成电路的校验数据生成及发送。

56.所述校验检查电路的作用是对来自接收电路的串行总线接收信号1进行校验并检查其校验数据是否正确,随后生成校验指示信号。

57.所述校验生成电路的作用是在来自控制状态机的控制信号4的指示下,将来自快速转发电路的发送数据进行校验运算,并将生成的发送校验数据发送回快速转发电路。

58.所述发送电路的作用时根据数字锁相环给出的时钟信号,对快速转发电路发送出的串行信号进行相位调整,形成与工业网络时钟有固定相位差的信号,随后发送至工业网络。

59.本发明专利的方法步骤为:

60.a.接收电路接收来自网络侧的串行总线接收信号并提取工业网络时钟,将该时钟信号输出至数字锁相环;

61.b.数字锁相环接收来自接收电路的工业网络时钟和本地的本地参考时钟,生成与工业网络时钟保持固定相位差的本地工作时钟和发送电路时钟,将本地工作时钟发送给接收电路、本地报文交互处理模块,将发送电路时钟发送给发送电路;

62.c.接收电路接收来自数字锁相环输出的本地工作时钟,将网络侧的串行总线接收信号向本地工作时钟同步,生成串行总线接收信号1,将串行总线接收信号1发送给本地报文交互处理模块的校验检查电路、接收串并转换电路、快速转发电路;

63.d.校验检查电路接收来自接收电路输出的串行总线接收信号1,生成校验指示信号并发送至本地报文交互处理模块外部;

64.e.接收串并转换电路接收来自接收电路的串行总线接收信号1和来自控制状态机的控制信号1,将串行总线接收信号1转换为并行接收数据,发送至本地报文交互处理模块外部,同时生成接收时间戳锁存信号,发送至本地报文交互处理模块外部,在接收到来自控制状态机的控制信号1后,发送并行接收数据至控制状态机;

65.f.控制状态机接收来自接收串并转换电路的并行接收数据,生成接收数据字段指示,将接收数据字段指示发送至本地报文交互处理模块外部,将控制信号2发送至发送并串转换电路,将控制信号3发送至快速转发电路,将控制信号4发送至校验生成电路;

66.g.发送并串转换电路在接收到控制信号2后,将来自本地报文交互处理模块外部的本地并行发送数据转换成本地发送数据,发送给快速转发电路,同时生成发送时间戳锁存信号,发送至本地报文交互处理模块外部;

67.h.快速转发电路在控制信号3的指示下可选择处理来自接收电路的串行总线接收信号1或来自发送并串转换电路的本地发送数据,将其作为发送数据发送至校验生成电路;

68.i.校验生成电路接收来自快速转发电路的发送数据,在来自控制状态机的控制信号4的指示下,生成发送校验数据并发送至快速转发电路;

69.j.快速转发电路在控制信号3的指示下,将串行总线接收信号1或本地发送数据加上发送校验数据后,作为串行总线发送信号1发送至发送电路;

70.k.发送电路接收来自快速转发电路的串行总线发送信号1,在来自数字锁相环的发送电路时钟作用下,将串行总线发送信号发送至工业网络。

71.本实施例使用verilog代码编写,可以使用synopsys designcompiler综合工具进行综合实现。

72.本实施例结构框图及连接关系如图1所示。在本实施例中,实现了三种数据的发送,包括串行总线接收信号1、本地发送数据、发送校验数据的发送。本实施例只体现本发明专利的一种实现方式,根据实际需要,可以增加或减少发送数据的种类。

73.本实施例实现的一种确定性低延时报文处理电路的输入输出端口包括:外部输入端口包括串行总线接收信号、本地参考时钟、本地并行发送数据;外部输出端口包括串行总线发送信号、校验指示信号、并行接收数据、接收时间戳锁存信号、接收数据字段指示、发送时间戳锁存信号。

74.本实施例实现的一种确定性低延时报文处理电路,其功能模块包括接收电路模块、数字锁相环模块、发送电路模块、本地报文交互处理模块,其中本地报文交互处理模块

包括校验检查电路模块、快速转发电路模块、接收串并转换电路模块、控制状态机模块、发送并串转换电路模块、校验生成模块。

75.本实施例的连接关系如下:

76.外部输入的串行总线接收信号接入接收电路模块,接收电路模块输出串行总线接收信号1、工业网络时钟;接收电路模块输出的串行总线接收信号1接入本地报文交互处理模块;

77.外部输入的本地参考时钟接入数字锁相环模块,接收电路输出的工业网络时钟接入数字锁相环模块,数字锁相环模块输出本地工作时钟、发送电路时钟;数字锁相环模块输出的本地工作时钟接入接收电路模块、本地报文交互处理模块,数字锁相环模块输出的发送电路时钟接入发送电路模块;

78.本地报文交互处理模块包括校验检查电路模块、接收串并转换电路模块、控制状态机模块、快速转发电路模块、发送并串转换电路模块、校验生成电路模块;

79.接收电路模块输出的串行总线接收信号1接入本地报文交互处理模块中的校验检查电路模块、接收串并转换电路模块、快速转发电路模块;

80.校验检查电路模块输出校验指示信号至外部;

81.接收串并转换电路模块输出并行接收数据、接收时间戳锁存信号至外部,输出并行接收数据至控制状态机模块;

82.控制状态机模块输出控制信号1、控制信号2、控制信号3、控制信号4,分别接入接收串并转换电路模块、发送并串转换电路模块、快速转发电路模块、校验生成电路模块,输出接收数据字段指示至外部;

83.外部输入的本地并行发送数据接入发送并串转换电路模块,发送并串转换电路模块输出发送时间戳锁存信号至外部,输出本地发送数据至快速转发电路模块;

84.快速转发电路模块输出发送数据至校验生成电路模块,输出串行总线发送信号1至发送电路模块;

85.校验生成电路模块输出发送校验数据至快速转发电路模块;

86.发送电路模块输出串行总线发送信号至外部;

87.如图2所示,本实施例中的电路延时包括接收电路模块的延时、快速转发电路模块的延时、发送电路模块的延时。

88.如图3所示,本实施例中的快速转发电路生成的报文来自串行总线接收信号1、本地发送数据、发送校验数据,由控制信号3在串行总线接收信号1、本地发送数据、发送校验数据中选择。

89.控制状态机电路原理如图5所示,其中接收数据解析模块采用通用电路结构,功能是从并行接收数据中提取报文开始指示、数据校验开始指示、报文结束指示、本地数据插入开始指示、本地数据插入结束指示,接收数据计数器对并行接收数据进行计数,输出接收数据计数值,接收数据计数值指示当前报文接收位置信息,其中状态机1采用典型状态机电路,状态转换如图6所示,包括空闲状态、状态1、状态2、状态3,其中空闲状态时控制信号1复位、控制信号2复位、控制信号3复位、控制信号4复位、数据接收字段指示信号指示复位状态,状态1时控制信号1置位、控制信号2复位、控制信号3为“串行总线接收信号1”选通有效、数据接收字段指示信号指示为本地数据接收状态,状态2时控制信号1复位、控制信号2置

位、控制信号3控制“本地发送数据”选通有效、数据接收字段指示信号指示为本地数据插入状态,状态3时控制信号3控制“发送校验数据”选通有效、控制信号4置位、数据接收字段指示信号指示复位状态。

90.快速转发电路原理如图4所示,多路选择器由控制信号3进行控制,控制信号3根据状态控制机内部的状态1、状态2、状态3的跳转,分别选通串行总线接收信号1、本地发送数据和发送校验数据,选择器输出发送数据,发送数据经触发器后输出串行总线发送信号1。触发器工作时钟为本地工作时钟,快速转发电路整体延时为触发器延时,即图2中的延时2。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。