一种jtag读指令延时处理方法

技术领域

1.本发明涉及jtag调试技术领域,尤其是一种jtag读指令延时处理方法。

背景技术:

2.随着计算机技术、通信技术和微电子技术的高速发展,jtag(jointtestaction group,联合测试工作组)作为一种国际标准测试协议(ieee1149.1兼容)广泛应用于芯片内部测试。目前,jtag接口主要用于芯片电气特性测试(边界扫描)及芯片内部调试(在线编程)。

3.jtag内部有一个状态机,称为tap控制器。tap控制器的状态机通过tck和tms进行状态的改变,实现数据和指令的输入。tap状态机共有16种状态,如图1所示,图1中每个椭圆形代表一种状态,标有状态名称及标识代码,箭头代表各状态所有可能的转换流程;状态前的转换是在tck的驱动下,由tms控制。jtag扫描链一共有四种操作,分别为挂起、捕获(capture)、移位(shift)和更新(update)。上位机的读指令在扫描链处于更新状态时下发,之后当扫描链处于捕获状态时,对应该读指令的返回数据才能更新至扫描链上,参照图2。读取不同存储器数据的网络延迟并不完全相同,很难提前预估延迟时间,为了保证读取的数据不被覆盖,现有的解决方案根据最长的延时时间来降低tck,实际应用中,tck降至芯片内核时钟的千分之一,乃至万分之一,大大降低了工作效率。

技术实现要素:

4.针对现有技术存在的上述问题,本发明提供了一种jtag读指令延时处理方法,能够大大提高工作效率。

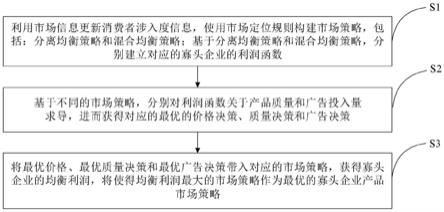

5.一种jtag读指令延时处理方法,若上位机下发的有效读指令在新的扫描链捕获状态到来时仍未返回有效读数据,则上位机下发无效指令,直至上位机接收到有效的读数据返回;无效指令为最高位为0的指令。

6.进一步的,jtag模块包括tap状态机、指令寄存器、旁路寄存器、调试扫描链,

7.所述tap状态机模块兼容标准ieee1149.1协议,根据状态转换控制指令寄存器及调试扫描链的写入和读出,完成调试指令的下发和返回数据的上传;

8.所述指令寄存器,用于控制链路的选择,通过tap状态机写入指令寄存器,根据指令寄存器的寄存器值选择接入旁路寄存器链或调试扫描链;

9.所述旁路寄存器,用于在多个芯片jtag接口串联情况下,旁路指定芯片的jtag调试电路,激活待调试芯片的jtag调试电路;

10.所述调试扫描链,用于在调试模式激活的情况下,完成仿真器下发指令的接收操作,以及上一轮指令返回值的上传操作。

11.进一步的,调试扫描链连接有1个指令缓存单元和1个数据缓存单元;所述缓存单元为深度为32,宽度为65的同步fifo。

12.本发明的有益效果:1、上位机下发无效指令驱动tap状态机正常运转,但不产生有

效读写操作(芯片内部接受到此类指令直接丢弃),意义在于实现读数据的轮询。jtag模块接收到上位机下发的无效指令,tap状态机会正常运转,每轮捕获状态均会检测是否返回有效数据,仅当检测到有效读数据返回后,上位机再继续下发有效指令即可避免读数据被覆盖的问题;2、调试扫描链连接有1个指令缓存单元和1个数据缓存单元,由于缓存单元的存在,上位机可以连续下发一批有效读指令,再一直下发无效指令,直至对应这16个读指令的读数据全部返回为止,再启动下一批有效指令的下发,进一步缩短返回数据的平均等待时间,提高在线仿真器的工作频率,进而提高整体工作效率。

附图说明

13.图1为tap状态机状态转换示意图;

14.图2为现有调试扫描链调试工作时序状态图;

15.图3为上位机下发无效指令后的现有调试扫描链调试工作时序状态图;

16.图4为jtag模块内部结构示意图;

17.图5是带缓存的调试扫描链结构示意图;

18.图6是带缓存的调试扫描链调试工作时序状态图。

具体实施方式

19.下面结合附图和具体实施方式对本发明作进一步详细的说明。本发明的实施例是为了示例和描述起见而给出的,而并不是无遗漏的或者将本发明限于所公开的形式。很多修改和变化对于本领域的普通技术人员而言是显而易见的。选择和描述实施例是为了更好说明本发明的原理和实际应用,并且使本领域的普通技术人员能够理解本发明从而设计适于特定用途的带有各种修改的各种实施例。

20.实施例1

21.从图2可以看出,上位机的读指令在扫描链处于更新状态时下发,若在下一次扫描链跳转至捕获状态前,对应该读指令的返回数据已经读出,则顺利能够更新至扫描链上,否则对应该读指令的返回数据需要等待再下一次扫描链跳转至捕获状态时,才能更新至扫描链上。倘若在对应该读指令的返回数据更新至扫描链上之前,上位机又下发了一次读指令,并且对应此读指令的返回数据及时读出,则会覆盖前一次读指令的返回数据,导致前一次读指令的返回数据的丢失。目前,针对这一技术问题的解决方案为,根据最长的延时时间来降低tck,实际应用中,tck降至芯片内核时钟的千分之一,乃至万分之一,大大降低了工作效率。

22.为此,本实施例提出一种jtag读指令延时处理方法,若上位机下发的有效读指令在新的扫描链捕获状态到来时仍未返回有效读数据,则上位机下发无效指令,直至上位机接收到有效的读数据返回。

23.上位机下发无效指令驱动tap状态机正常运转,但不产生有效读写操作(芯片内部接受到此类指令直接丢弃),意义在于实现读数据的轮询。jtag模块接收到上位机下发的无效指令,如图3所示,tap状态机会正常运转,每轮捕获状态均会检测是否返回有效数据,仅当检测到有效读数据返回后,上位机再继续下发有效指令即可避免读数据被覆盖的问题。

24.本实施例提供的jtag读指令延时处理方法的优势为:上位机下发无效指令在保证

tap状态机正常运转的前提下,不产生有效读写操作。由于上位机下发无效指令起到了监测读数据是否已经返回的作用,因此再通过降低tck来解决读数据覆盖的问题,tck可以提高到最高芯片内核时钟的一半,从而通过插入无效指令的方式,使得调试指令的生效延时接近芯片内部指令的网络延迟,大大提高了工作效率。

25.jtag模块包括tap状态机、指令寄存器、旁路寄存器、调试扫描链,内部连接关系如图4所示。

26.所述tap状态机模块兼容标准ieee1149.1协议,根据状态转换控制指令寄存器及调试扫描链的写入和读出,完成调试指令的下发和返回数据的上传;

27.所述指令寄存器,用于控制链路的选择,通过tap状态机写入指令寄存器,根据指令寄存器的寄存器值选择接入旁路寄存器链或调试扫描链。

28.所述旁路寄存器,用于在多个芯片jtag接口串联情况下,旁路指定芯片的jtag调试电路,激活待调试芯片的jtag调试电路。

29.所述调试扫描链,用于在调试模式激活的情况下,完成仿真器下发指令的接收操作,以及上一轮指令返回值的上传操作。

30.实施例2

31.当上位机需要连续下发一批读指令时,扫描链接收到每条读指令的返回数据都需要等待数量不等的捕获状态,为了在这一情况下进一步缩短返回数据的平均等待时间,本实施例中的调试扫描链连接有1个指令缓存单元和1个数据缓存单元,所述缓存单元可以是深度为32,宽度为65的同步fifo,如图5所示。

32.由于缓存单元的存在,上位机可以连续下发一批(例如16个,不超过fifo深度即可)有效读指令,参照图6,再一直下发无效指令,直至对应这16个读指令的读数据全部返回为止,再启动下一批有效指令的下发。

33.显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域及相关领域的普通技术人员在没有作出创造性劳动的前提下所获得的所有其他实施例,都应属于本发明保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。