1.本发明涉及一种生成并输出多位格雷码的多位格雷码生成电路。

背景技术:

2.以往,开发了各种用于生成多位(比特,bit)的格雷码的技术。作为与此相关联的技术,有日本专利特开平6-053818号公报所公开的发明。

3.日本特开平6-053818号公报涉及对脉冲信号进行计数并输出与计数值对应的格雷码的多位格雷码计数器。

4.该多位格雷码计数器包括具有加减法功能的n位格雷码加/减法计数器和m位的格雷码计数器。

技术实现要素:

5.在上述日本专利特开平6-053818号公报中公开的多位格雷码计数器中,在构成格雷码计数器的触发器(以下,简称为ff)电路之间连接有ff电路以外的多个逻辑电路。输入到ff电路的时钟信号的驱动频率由前级的ff电路的延迟时间、逻辑电路的延迟时间以及下一级的ff电路的建立时间决定。

6.即,如果在ff电路之间存在多个逻辑电路,则延迟时间变大,无法使输入到ff电路的时钟信号的驱动频率成为高频率,也无法使从格雷码计数器输出的格雷码的频率成为高频率。

7.本发明的一个方面的目的在于,实现能够以高频率输出格雷码的多位格雷码生成电路。

8.为了解决上述问题,根据本发明的一个方面的多位格雷码生成电路包括:第零格雷码生成电路,其生成与多位格雷码的第0位对应的格雷码;以及多个格雷码生成电路,其生成与比多位格雷码的第0位更高位的各位对应的格雷码,多个格雷码生成电路分别由多个触发器电路构成,前级的触发器电路的输出输入到下一级的触发器电路,最终级的触发器电路的输出被初级的触发器电路反相并保持,将多个触发器电路中的任一个的输出作为与各位对应的格雷码输出。

9.根据本发明的一个方面,能够提供一种能够以高频率输出格雷码的多位格雷码生成电路。

附图说明

10.图1是示出本发明的第一实施方式所涉及的多位格雷码生成电路的概略构成的框图。图2是用于说明本发明的第一实施方式所涉及的多位格雷码生成电路的动作概要的时序图。图3是示出时钟延迟电路的电路构成的图。

图4是用于说明时钟延迟电路的动作的时序图。图5是示出bit0格雷码生成电路的电路构成的图。图6是用于说明bit0格雷码生成电路的动作的时序图。图7是示出bit1格雷码生成电路的电路构成的图。图8是用于说明bit1格雷码生成电路的动作的时序图。图9是示出bit2格雷码生成电路的电路构成的图。图10是用于说明bit2格雷码生成电路的动作的时序图。图11是示出bit3格雷码生成电路的电路构成的图。图12是用于说明bit3格雷码生成电路的动作的时序图。图13是用于说明本发明的第一实施方式所涉及的多位格雷码生成电路的动作细节的时序图。图14是示出本发明的第二实施方式所涉及的多位格雷码生成电路的概略构成的框图。图15是用于说明本发明的第二实施方式所涉及的多位格雷码生成电路中的sel信号为“0”时的动作的时序图。图16是用于说明本发明的第二实施方式所涉及的多位格雷码生成电路中的sel信号为“1”时的动作的时序图。图17是示出本发明的第三实施方式所涉及的多位格雷码生成电路的概略构成的框图。图18是用于说明本发明的第三实施方式所涉及的多位格雷码生成电路中的sel信号为“0”时的动作的时序图。图19是用于说明本发明的第三实施方式所涉及的多位格雷码生成电路中的sel信号为“1”时的动作的时序图。

具体实施方式

11.〔第一实施方式〕以下,详细说明本发明的一实施方式。此外,为了便于说明,对相同的部件标注相同的附图标记,它们的名称以及功能也相同。因此,将不重复对它们的详细说明。

12.<格雷码生成电路100的构成和动作>图1是示出本发明的第一实施方式所涉及的多位格雷码生成电路100的概略构成的框图。格雷码生成电路100包括时钟延迟电路1、bit0格雷码生成电路(也称为第零格雷码生成电路)2、bit1格雷码生成电路(也称为第一格雷码生成电路)3、bit2格雷码生成电路(也称第二格雷码生成电路)4、bit3格雷码生成电路(也称第三格雷码生成电路)5、以及bit4格雷码生成电路(也称为第四格雷码生成电路)6。

13.时钟延迟电路1在复位信号xrst从低电平(以下简称为“0”)变为高电平(以下简称为“1”)后,在几个时钟后开始输出时钟信号ck0。

14.bit0格雷码生成电路2、bit1格雷码生成电路3、bit2格雷码生成电路4、bit3格雷码生成电路5、以及bit4格雷码生成电路6与时钟延迟电路1输出的时钟信号ck0同步,并输出各自对应的位的格雷码。与各位对应的格雷码生成电路2~6的细节将在后述。

15.图2是用于说明本发明的第一实施方式所涉及的多位格雷码生成电路100的动作概要的时序图。在时刻t1,复位信号xrst变为“1”。在该几个时钟后的t2中,时钟延迟电路1开始时钟信号ck0的输出。然后,在几个时钟后的t3中,与各位对应的格雷码生成电路2~6开始输出格雷码d<4:0>。

16.<时钟延迟电路1的构成和动作>图3是示出时钟延迟电路1的电路构成的图。时钟延迟电路1包括ff电路11~13、锁存电路14和and电路15。在ff电路11~13和锁存电路14中连接有相同的时钟信号ck。另外,在ff电路11~13中连接有相同的复位信号xrst。

17.ff电路11~13在xrst信号为“0”时被复位,在xrst信号为“1”时在ck信号的上升沿保持输入端子d中所输入的值,并输出到输出端子q。

18.此外,ff电路11~13在时钟信号的上升沿动作,但也可以在时钟信号的下降沿动作。因此,由于ff电路11~13可以在时钟信号的上升沿或下降沿动作,因此也能够记载为ff电路11~13与时钟信号同步动作。

19.锁存电路14在ck信号的上升沿保持输入到端子d的值并向端子q输出,并在ck信号为“1”的期间维持这种状态。并且,在ck信号为“0”时,将输入到端子d的值原样输出到(穿过)端子q。

20.图4是用于说明时钟延迟电路1的动作的时序图。在时刻t1,复位信号xrst变为“1”。在t2,ff电路11的输出信号n0从“0”变为“1”。在t3,ff电路12的输出信号n1从“0”变为“1”。在t4,ff电路13的输出信号n2从“0”变为“1”。

21.在t5,锁存电路14的输出信号n3从“0”变为“1”。在t6中,and电路15开始时钟信号ck0的输出。

22.<bit0格雷码生成电路2的构成和动作>图5是示出bit0格雷码生成电路2的电路构成的图。bit0格雷码生成电路2包含ff电路21。从时钟延迟电路1输出的时钟信号ck0和复位信号xrst连接到ff电路21。

23.ff电路21在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的下降沿保持端子xd的值,并输出到端子q。由于xd端子将从端子q输出的值反相并输入,所以每次ck0信号下降时,xd端子将从端子q输出的值反相并输出。输出到该ff电路21的输出端子q的值成为第0位(bit0)的格雷码d0。

24.此外,ff电路21在时钟信号的下降沿动作,但也可以在时钟信号的上升沿动作。因此,由于ff电路21可以在时钟信号的上升沿或下降沿动作,因此也能够记载为ff电路21与时钟信号同步动作。

25.图6是用于说明bit0格雷码生成电路2的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,ff电路21的输出信号d0变为“0”。在t2,ff电路21的输出信号d0在ck0信号的下降沿从“0”变为“1”。在t3,ff电路21的输出信号d0保持在“1”。在t4,ff电路21的输出信号d0从“1”变为“0”。

26.在t5,ff电路21的输出信号d0保持在“0”。在t6,ff电路21的输出信号d0从“0”变为“1”。在t7,ff电路21的输出信号d0保持在“1”。之后,进行相同的动作。

27.<bit1格雷码生成电路3的构成和动作>图7是示出bit1格雷码生成电路3的电路构成的图。bit1格雷码生成电路3包含ff

电路31和32。从时钟延迟电路1输出的时钟信号ck0和复位信号xrst连接到ff电路31和32。

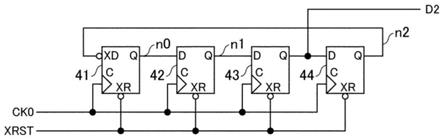

28.ff电路31在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子xd的值,并输出到端子q。由于xd端子将从ff电路32的输出端子q输出的值进行反相并输入,所以每次ck0信号上升时,xd端子将ff电路32的输出端子q所输出的值反相并输出。

29.ff电路32在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子d的值,并输出到端子q。输出到该ff电路32的输出端子q的值成为第1位(bit1)的格雷码d1。

30.此外,ff电路31和32在时钟信号的上升沿动作,但也可以在时钟信号的下降沿动作。因此,由于ff电路31和32可以在时钟信号的上升沿或下降沿动作,因此也能够记载为ff电路31和32与时钟信号同步动作。

31.图8是用于说明bit1格雷码生成电路3的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,ff电路31的输出端子q的值(n0)从“0”变为“1”。在t2,ff电路31的输出信号n0保持在“1”。在t3,ff电路32的输出端子q的值(d1)从“0”变为“1”。在t4,ff电路31和32的输出信号n0和d1保持在“1”。

32.在t5,ff电路31的输出信号n0从“1”变为“0”。在t6,ff电路31的输出信号n0保持在“0”,ff电路32的输出信号d1保持在“1”。在t7,ff电路32的输出信号d1从“1”变为“0”。在t8,ff电路31和32的输出信号n0和d1保持在“0”。之后,进行相同的动作。

33.<bit2格雷码生成电路4的构成和动作>图9是示出bit2格雷码生成电路4的电路构成的图。bit2格雷码生成电路4包含ff电路41~44。从时钟延迟电路1输出的时钟信号ck0和复位信号xrst连接到ff电路41~44。

34.ff电路41在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子xd的值,并输出到端子q。由于xd端子将从ff电路44的输出端子q输出的值进行反相并输入,所以每次ck0信号上升时,xd端子将ff电路44的输出端子q所输出的值反相并输出。

35.ff电路42~44在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子d的值,并输出到端子q。输出到ff电路43的输出端子q的值成为第2位(bit2)的格雷码d2。

36.此外,ff电路41~44在时钟信号的上升沿动作,但也可以在时钟信号的下降沿动作。因此,由于ff电路41~44可以在时钟信号的上升沿或下降沿动作,因此也能够记载为ff电路41~44与时钟信号同步动作。

37.图10是用于说明bit2格雷码生成电路4的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,ff电路41的输出端子q的值(n0)从“0”变为“1”。在t2,ff电路41的输出信号n0保持在“1”。在t3,ff电路42的输出端子q的值(n1)从“0”变为“1”。在t4,ff电路41和42的输出信号n0和n1保持在“1”。

38.在t5,ff电路43的输出信号d2从“0”变为“1”。在t6,ff电路41~43的输出信号n0、n1和d2保持在“1”。在t7,ff电路44的输出信号n2从“0”变为“1”。在t8,ff电路41~44的输出信号n0、n1、d2和n2保持在“1”。

39.在t9,ff电路41的输出信号n0从“1”变为“0”。在t10,ff电路41~44保持相同的值。在t11,ff电路42的输出信号n1从“1”变为“0”。在t12,ff电路41~44保持相同的值。在t13,ff电路43的输出信号d2从“1”变为“0”。之后,进行相同的动作。

40.<bit3格雷码生成电路5的构成和动作>图11是示出bit3格雷码生成电路5的电路构成的图。bit3格雷码生成电路5包含ff电路51~58。从时钟延迟电路1输出的时钟信号ck0和复位信号xrst连接到ff电路51~58。

41.ff电路51在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子xd的值,并输出到端子q。由于xd端子将从ff电路58的输出端子q输出的值进行反相并输入,所以每次ck0信号上升时,xd端子将ff电路58的输出端子q所输出的值反相并输出。

42.ff电路52~58在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的上升沿保持端子d的值,并输出到端子q。输出到ff电路55的输出端子q的值成为第3位(bit3)的格雷码d3。

43.此外,ff电路51~58在时钟信号的上升沿动作,但也可以在时钟信号的下降沿动作。因此,由于ff电路51~58可以在时钟信号的上升沿或下降沿动作,因此也能够记载为ff电路51~58与时钟信号同步动作。

44.图12是用于说明bit3格雷码生成电路5的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,ff电路51的输出端子q的值(n0)从“0”变为“1”。在t2,ff电路51的输出信号n0保持在“1”。在t3,ff电路52的输出端子q的值(n1)从“0”变为“1”。在t4,ff电路51和52的输出信号n0和n1保持在“1”。

45.在t5,ff电路53的输出信号n2从“0”变为“1”。在t6,ff电路51~53的输出信号n0、n1和n2保持在“1”。在t7,ff电路54的输出信号n3从“0”变为“1”。在t8,ff电路51~54的输出信号n0、n1、n2和n3保持在“1”。

46.在t9,ff电路55的输出信号d3从“0”变为“1”。在t10,ff电路51~58保持相同的值。在t11,ff电路56的输出信号n4从“0”变为“1”。在t12,ff电路51~58保持相同的值。在t13,ff电路57的输出信号n5从“0”变为“1”。

47.在t14,ff电路51~58保持相同的值。在t15,ff电路58的输出信号n6从“0”变为“1”。重复同样的动作,在t16,ff电路55的输出信号d3从“1”变为“0”。

48.此外,不对bit4格雷码生成电路6的构成以及动作进行详细的说明。然而,对于比第3位更高位的位,本领域技术人员容易参考bit0格雷码生成电路2~bit3格雷码生成电路5的构成和动作进行类推。

49.<多位格雷码生成电路100的动作>图13是用于详细说明多位格雷码生成电路100的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,但bit0格雷码生成电路2的输出信号d0变为“0”。此时,多位格雷码用十进制表示为“0”。

50.在时刻t2,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“1”。

51.在时刻t3,bit1格雷码生成电路3的输出信号d1变为“1”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“3”。

52.在时刻t4,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“2”。

53.在时刻t5,bit2格雷码生成电路4的输出信号d2变为“1”,其他格雷码生成电路2、3、5、6的输出信号不变。此时,多位格雷码用十进制表示为“6”。

54.在时刻t6,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“7”。

55.在时刻t7,bit1格雷码生成电路3的输出信号d1变为“0”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“5”。

56.在时刻t8,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“4”。

57.在时刻t9,bit3格雷码生成电路5的输出信号d3变为“1”,其他格雷码生成电路2~4和6的输出信号不变。此时,多位格雷码用十进制表示为“12”。

58.在时刻t10,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“13”。

59.在时刻t11,bit1格雷码生成电路3的输出信号d1变为“1”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“15”。

60.在时刻t12,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“14”。

61.在时刻t13,bit2格雷码生成电路4的输出信号d2变为“0”,其他格雷码生成电路2、3、5、6的输出信号不变。此时,多位格雷码用十进制表示为“10”。

62.在时刻t14,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“11”。

63.在时刻t15,bit1格雷码生成电路3的输出信号d1变为“0”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“9”。

64.在时刻t16,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“8”。

65.在时刻t17,bit4格雷码生成电路6的输出信号d4变为“1”,其他格雷码生成电路2~5的输出信号不变。此时,多位格雷码用十进制表示为“24”。之后,进行相同的动作。

66.如以上说明的那样,在本实施方式所涉及的多位格雷码生成电路100中,bit1格雷码生成电路3~bit3格雷码生成电路5的电路构成具有以下的构成。即,具有如下构成:前级的ff电路的输出被输入到下一级的ff电路且最终级的ff电路的输出被初级的ff电路反转并被保持的、所谓的多个ff电路环状连接。并且,将多个ff电路中的任一个的输出设为与各位对应的格雷码。

67.通过设为上述构成,ff电路之间没有逻辑电路,延迟时间变小,并且能够使输入到触ff电路的时钟信号的驱动频率成为高频率。因此,能够使从多位格雷码生成电路100输出的格雷码的频率成为高频率。

68.另外,由于bit0格雷码生成电路2和其它格雷码生成电路3~6以错开时钟信号的半周期量的方式进行动作,因此整体能够以时钟信号的半周期进行动作。因此,能够进一步使从多位格雷码生成电路100输出的格雷码的频率成为高频率。

69.另外,由于时钟延迟电路1在基于复位信号xrst的复位解除之后,在规定的时钟数之后开始时钟信号的输出,因此能够在任意的时序下开始多位格雷码的输出。

70.〔第二实施方式〕以下,说明本发明的其它实施方式。并且,为了便于说明,对与在上述实施方式中

说明的部件具有相同功能的部件,标注相同的附图标记,并不再重复说明。

71.<格雷码生成电路100a的构成和动作>图14是示出本发明的第二实施方式所涉及的多位格雷码生成电路100a的概略构成的框图。与图1所示的第一实施方式所涉及的多位格雷码生成电路100相比,仅在增加了缓冲器61~63、反相器(反相电路)64~65以及选择器(选择电路)66~67这一方面不同。

72.缓冲器61~63将来自bit0格雷码生成电路2~bit2格雷码生成电路4的输出信号d0~d2的值直接作为sd0~sd2输出。该缓冲器61~63没有亦可。

73.反相器64将来自bit3格雷码生成电路5的输出信号d3的值进行反相并输出。当sel信号为“0”时,选择器66选择来自bit3格雷码生成电路5的输出信号d3的值作为sd3输出。另外,当sel信号为“1”时,选择器66选择d3被反相器64反相的值作为sd3输出。

74.反相器65将来自bit4格雷码生成电路6的输出信号d4的值进行反相并输出。当sel信号为“0”时,选择器67选择来自bit4格雷码生成电路6的输出信号d4的值作为sd4输出。另外,当sel信号为“1”时,选择器67选择d4被反相器65反相的值作为sd4输出。

75.图15是用于说明本发明的第二实施方式所涉及的多位格雷码生成电路100a中的sel信号为“0”时的动作的时序图。该时序图与图13所示的时序图相同。因此,将不重复详细说明。

76.图16是用于说明本发明的第二实施方式所涉及的多位格雷码生成电路100a中的sel信号为“1”时的动作的时序图。在时刻t1,开始来自时钟延迟电路1的时钟信号ck0的输出,但bit0格雷码生成电路2~bit2格雷码生成电路4的输出信号d0~d2为“0”,sd0~sd3变为“0”。此外,bit3格雷码生成电路5和bit4格雷码生成电路6的输出信号d3和d4是“0”,sd3~sd4变为“1”。此时,多位格雷码用十进制表示为“24”。

77.在时刻t2,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“25”。

78.在时刻t3,bit1格雷码生成电路3的输出信号d1变为“1”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“27”。

79.在时刻t4,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“26”。

80.在时刻t5,bit2格雷码生成电路4的输出信号d2变为“1”,其他格雷码生成电路2、3、5、6的输出信号不变。此时,多位格雷码用十进制表示为“30”。

81.在时刻t6,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“31”。

82.在时刻t7,bit1格雷码生成电路3的输出信号d1变为“0”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“29”。

83.在时刻t8,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“28”。

84.在时刻t9,bit3格雷码生成电路5的输出信号d3变为“1”,sd3变为“0”。其他格雷码生成电路2~4和6的输出信号不变。此时,多位格雷码用十进制表示为“20”。

85.在时刻t10,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“21”。

86.在时刻t11,bit1格雷码生成电路3的输出信号d1变为“1”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“23”。

87.在时刻t12,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“22”。

88.在时刻t13,bit2格雷码生成电路4的输出信号d2变为“0”,其他格雷码生成电路2、3、5、6的输出信号不变。此时,多位格雷码用十进制表示为“18”。

89.在时刻t14,bit0格雷码生成电路2的输出信号d0变为“1”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“19”。

90.在时刻t15,bit1格雷码生成电路3的输出信号d1变为“0”,其他格雷码生成电路2、4~6的输出信号不变。此时,多位格雷码用十进制表示为“17”。

91.在时刻t16,bit0格雷码生成电路2的输出信号d0变为“0”,其他格雷码生成电路3~6的输出信号不变。此时,多位格雷码用十进制表示为“16”。

92.在时刻t17,bit4格雷码生成电路6的输出信号d4变为“1”,sd4变为“0”。其他格雷码生成电路2~5的输出信号不变。此时,多位格雷码用十进制表示为“0”。之后,进行相同的动作。

93.如以上说明的那样,在本实施方式所涉及的多位格雷码生成电路100a中,选择器66和67在sel信号为“0”时,选择来自bit3格雷码生成电路5和bit4格雷码生成电路6的输出信号d3和d4的值,并作为sd3和sd4输出。另外,当sel信号为“1”时,选择器66和67选择d3和d4被反相器64和65反相的值并将这些值作为sd3和sd4输出。

94.因此,通过将sel信号从“0”变为“1”,能够将格雷码的起始码用十进制表示并从“0”变为“24”,能够提供通用性高的多位格雷码生成电路。

95.〔第三实施方式〕以下,说明本发明的其它实施方式。并且,为了便于说明,对与在上述实施方式中说明的部件具有相同功能的部件,标注相同的附图标记,并不再重复说明。

96.<格雷码生成电路100b的构成和动作>图17是示出本发明的第三实施方式所涉及的多位格雷码生成电路100b的概略构成的框图。与图1所示的第一实施方式所涉及的多位格雷码生成电路100相比,仅在增加了ff电路71~73以及选择器(选择电路)74~78这一方面不同。

97.ff电路71~73在xrst信号为“0”时被复位,在xrst信号为“1”时在ck0信号的下降沿保持端子d的值,并输出到端子q。

98.当sel信号为“0”时,选择器74选择来自bit0格雷码生成电路2的输出信号d0作为gb_d0输出。另外,当sel信号为“1”时,选择器74选择时钟信号ck0作为gb_d0输出。

99.当sel信号为“0”时,选择器75选择来自bit1格雷码生成电路3的输出信号d1作为gb_d1输出。另外,当sel信号为“1”时,选择器75选择来自bit0格雷码生成电路2的输出信号d0作为gb_d1输出。

100.当xrst信号为“1”时,ff电路71在ck0信号的下降沿保持来自bit1格雷码生成电路3的输出信号d1的值,并将该值输出到选择器76。当sel信号为“0”时,选择器76选择来自bit2格雷码生成电路4的输出信号d2作为gb_d2输出。另外,当sel信号为“1”时,选择器76选择来自ff电路71的输出信号作为gb_d2输出。

101.当xrst信号为“1”时,ff电路72在ck0信号的下降沿保持bit2格雷码生成电路4的输出信号n2的值,并将该值输出到选择器77。当sel信号为“0”时,选择器77选择来自bit3格雷码生成电路5的输出信号d3作为gb_d3输出。另外,当sel信号为“1”时,选择器77选择来自ff电路72的输出信号作为gb_d3输出。

102.当xrst信号为“1”时,ff电路73在ck0信号的下降沿保持bit3格雷码生成电路5的输出信号n6的值,并将该值输出到选择器78。当sel信号为“0”时,选择器78选择来自bit4格雷码生成电路6的输出信号d4作为gb_d4输出。另外,当sel信号为“1”时,选择器78选择来自ff电路73的输出信号作为gb_d4输出。

103.以下,将选择器74~78的输出信号gb_d0~gb_d4称为二进制代码。

104.图18是用于说明本发明的第三实施方式所涉及的多位格雷码生成电路100b中的sel信号为“0”时的动作的时序图。该时序图与图13所示的时序图相同。因此,将不重复详细说明。

105.图19是用于说明本发明的第三实施方式所涉及的多位格雷码生成电路100b中的sel信号为“1”时的动作的时序图。在时刻t1,选择器74~78的输出信号gb_d0~gb_d4都变为“0”。此时,二进制代码用十进制表示为“0”。

106.在时刻t2,开始来自时钟延迟电路1的时钟信号ck0的输出,选择器74选择时钟信号ck0作为gb_d0输出。此时,二进制代码用十进制表示为“1”。之后,选择器74将与时钟信号ck0相同的时序波形输出到gb_d0。

107.在时刻t3,bit0格雷码生成电路2的输出信号d0变为“1”,选择器75向gb_d1输出“1”。此时,二进制代码用十进制表示为“2”。

108.在时刻t4,bit1格雷码生成电路3的输出信号d1变为“1”,ff电路71的输出端子q的输出保持为“0”。此时,二进制代码用十进制表示为“3”。

109.在时刻t5,bit0格雷码生成电路2的输出信号d0变为“0”,选择器75向gb_d1输出“0”。另外,ff电路71保持bit1格雷码生成电路3的输出信号d1的值“1”,并将该值输出到选择器76。选择器76选择ff电路71所保持的值“1”作为gb_d2输出。此时,二进制代码用十进制表示为“4”。

110.在时刻t6,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“5”。

111.在时刻t7,bit0格雷码生成电路2的输出信号d0变为“1”,选择器75向gb_d1输出“1”。此时,二进制代码用十进制表示为“6”。

112.在时刻t8,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“7”。

113.在时刻t9,ff电路71保持bit1格雷码生成电路3的输出信号d1的值“0”,并将该值输出到选择器76。选择器76选择ff电路71所保持的值“0”作为gb_d2输出。另外,ff电路72保持bit2格雷码生成电路4的输出信号n2的值“1”,并将该值输出到选择器77。选择器77选择ff电路72所保持的值“1”作为gb_d3输出。此时,二进制代码用十进制表示为“8”。

114.在时刻t10,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“9”。

115.在时刻t11,bit0格雷码生成电路2的输出信号d0变为“1”,选择器75向gb_d1输出“1”。此时,二进制代码用十进制表示为“10”。

116.在时刻t12,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“11”。

117.在时刻t13,bit0格雷码生成电路2的输出信号d0变为“0”,选择器75向gb_d1输出“0”。另外,ff电路71保持bit1格雷码生成电路3的输出信号d1的值“1”,并将该值输出到选择器76。选择器76选择ff电路71所保持的值“1”作为gb_d2输出。此时,二进制代码用十进制表示为“12”。

118.在时刻t14,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“13”。

119.在时刻t15,bit0格雷码生成电路2的输出信号d0变为“1”,选择器75向gb_d1输出“1”。此时,二进制代码用十进制表示为“14”。

120.在时刻t16,选择器75~78的输出gb_d1~gb_d4的值不变。此时,二进制代码用十进制表示为“15”。

121.在时刻t17,ff电路71保持bit1格雷码生成电路3的输出信号d1的值“0”,并将该值输出到选择器76。选择器76选择ff电路71所保持的值“0”作为gb_d2输出。另外,ff电路72保持bit2格雷码生成电路4的输出信号n2的值“0”,并将该值输出到选择器77。选择器77选择ff电路72所保持的值“0”作为gb_d3输出。另外,ff电路73保持bit3格雷码生成电路5的输出信号n6的值“1”,并将该值输出到选择器78。选择器78选择ff电路73所保持的值“1”作为gb_d4输出。此时,二进制代码用十进制表示为“16”。

122.如上所述,根据本实施方式的多位格雷码生成电路100b,在sel信号为“1”时,选择器74选择时钟信号ck0并输出。当sel信号为“0”时,选择器75选择来自bit0格雷码生成电路2的输出信号d0并将其输出。另外,选择器76~78选择来自ff电路73的输出信号并将其输出。通过这种构成,多位格雷码生成电路100b能够将5位的格雷码转换为5位的二进制代码。

123.<总结>本发明的方式1所涉及的多位格雷码生成电路包括:第零格雷码生成电路,其生成与多位格雷码的第0位对应的格雷码;以及多个格雷码生成电路,其生成与比多位格雷码的第0位更高位的各位对应的格雷码,多个格雷码生成电路分别由多个触发器电路构成,前级的触发器电路的输出输入到下一级的触发器电路,最终级的触发器电路的输出被初级的触发器电路反相并保持,将多个触发器电路中的任一个的输出作为与各位对应的格雷码输出。

124.根据上述构成,触发器电路之间没有逻辑电路,延迟时间变小,并且能够使输入到触发器电路的时钟信号的驱动频率成为高频率。因此,能够使从多位格雷码生成电路输出的格雷码的频率成为高频率。

125.本发明的方式2所涉及的多位格雷码生成电路在上述方式1中,第零格雷码生成电路与多个格雷码生成电路之间错开时钟信号的半周期地动作。

126.根据上述构成,能够进一步使从多位格雷码生成电路输出的格雷码的频率成为高频率。

127.本发明的方式3所涉及的多位格雷码生成电路在上述方式1或2中,第零格雷码生成电路包含第一触发器电路,第一触发器电路与时钟信号同步地保持将输出反相后的值,

并将该输出作为格雷码的第0位输出。

128.根据上述构成,能够使输入到触发器电路的时钟信号的驱动频率成为高频率。

129.本发明的方式4所涉及的多位格雷码生成电路在上述方面1~3中的任一个中,多个格雷码生成电路包括第一格雷码生成电路,第一格雷码生成电路具有:第二触发器电路,其与时钟信号同步地保持并输出将输入反相后的值;以及第三触发器电路,其与时钟信号同步地保持第二触发器电路的输出的值并输出到第二触发器电路,并将第三触发器电路的输出作为格雷码的第1位。

130.根据上述构成,触发器电路之间没有逻辑电路,延迟时间变小,并且能够使输入到触发器电路的时钟信号的驱动频率成为高频率。

131.本发明的方式5所涉及的多位格雷码生成电路在上述方面4中,多个格雷码生成电路还包括第二格雷码生成电路,第二格雷码生成电路具有:第四触发器电路,其与时钟信号同步地保持并输出将输入反相后的值;第五触发器电路,其与时钟信号同步地保持并输出第四触发器电路的输出的值;第六触发器电路,其与时钟信号同步地保持并输出第五触发器电路的输出的值,并将第六触发器电路的输出作为格雷码的第2位;以及第七触发器电路,其与时钟信号同步地保持第六触发器电路的输出的值并输出到第四触发器电路。

132.根据上述构成,触发器电路之间没有逻辑电路,延迟时间变小,并且能够使输入到触发器电路的时钟信号的驱动频率成为高频率。

133.本发明的方式6所涉及的多位格雷码生成电路在上述方面5中,多个格雷码生成电路还包含第三格雷码生成电路,第三格雷码生成电路具有:第八触发器电路,其与时钟信号同步地保持并输出将输入反相后的值;第九触发器电路,其与时钟信号同步地保持并输出第八触发器电路的输出的值;第十触发器电路,其与时钟信号同步地保持并输出第九触发器电路的输出的值;第十一触发器电路,其与时钟信号同步地保持并输出第十触发器电路的输出的值;第十二触发器电路,其与时钟信号同步地保持并输出第十一触发器电路的输出的值,并将第十二触发器电路的输出作为格雷码的第3位;第十三触发器电路,其与时钟信号同步地保持并输出第十二触发器电路的输出的值;第十四触发器电路,其与时钟信号同步地保持并输出第十三触发器电路的输出的值;以及第十五触发器电路,其与时钟信号同步地保持第十四触发器电路的输出的值并输出到第八触发器电路。

134.根据上述构成,触发器电路之间没有逻辑电路,延迟时间变小,并且可以提高输入到触发器电路的时钟信号的驱动频率。

135.本发明的方式7所涉及的多位格雷码生成电路在上述方面6中,多位格雷码生成电路还包括:第四格雷码生成电路,其生成格雷码的第4位;第一选择电路,其选择性输出来自第三格雷码生成电路的输出的值和将来自第三格雷码生成电路的输出反相后的值;第二选择电路,其选择性输出来自第四格雷码生成电路的输出的值和将来自第四格雷码生成电路的输出反相后的值。

136.根据上述的构成,能够提供一种能够变更格雷码的起始码,且通用性高的多位格雷码生成电路。

137.本发明的方式8所涉及的多位格雷码生成电路在上述方面6中,多位格雷码生成电路还包括:第四格雷码生成电路,其生成格雷码的第4位;第十六触发器电路,其与时钟信号同步地保持并输出第一格雷码生成电路的输出的值;第十七触发器电路,其与时钟信号同

步地保持并输出第二格雷码生成电路的第七触发器电路的输出的值;第十八触发器电路,其与时钟信号同步地保持并输出第三格雷码生成电路的第十五触发器电路的输出的值;第三选择电路,其选择性输出来自第零格雷码生成电路的输出和时钟信号;第四选择电路,其选择性输出来自第一格雷码生成电路的输出和来自第零格雷码生成电路的输出;第五选择电路,其选择性输出来自第二格雷码生成电路的输出和来自第十六触发器电路的输出;第六选择电路,其选择性输出来自第三格雷码生成电路的输出和来自第十七触发器电路的输出;第七选择电路,其选择性输出来自第四格雷码生成电路的输出和来自第十八触发器电路的输出。

138.根据上述的构成,多位格雷码生成电路能够将格雷码转换为二进制代码。

139.本发明的方式9所涉及的多位格雷码生成电路在上述方面1~8的任一个中,多位格雷码生成电路还包括时钟延迟电路,时钟延迟电路自复位解除起经过规定的时钟数后,开始时钟信号的输出。

140.根据上述的构成,多位格雷码生成电路能够在任意的时序下开始多位格雷码的输出。

141.本发明不限于上述各实施方式,能在权利要求所示的范围中进行各种变更,将不同的实施方式中分别公开的技术手段适当组合得到的实施方式也包含于本发明的技术范围。而且,能够通过组合各实施方式分别公开的技术方法来形成新的技术特征。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。