技术特征:

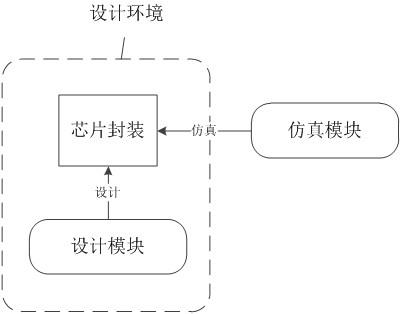

1.一种芯片封装电磁建模系统,其特征在于,所述的芯片封装电磁建模系统包括设计模块和仿真模块;所述设计模块和所述仿真模块集成在同一平台中;所述设计模块完成芯片布局,建构芯片封装并根据所述芯片封装的仿真结果优化改进所述芯片封装,得到合格芯片封装;所述仿真模块在所述设计模块的设计环境中对所述芯片封装进行仿真模拟,将所述仿真结果传递给所述设计模块;所述设计模块包括速度设计子模块、均衡设计子模块和精确设计子模块;所述速度设计子模块用于简化芯片设计,所述均衡设计子模块用于优化经由所述速度设计子模块设计的芯片封装,所述精确设计子模块用于优化经由所述精确设计子模块设计的芯片封装。2.根据权利要求1所述的芯片封装电磁建模系统,其特征在于,所述设计模块包括速度设计子模块;所述速度设计子模块对芯片互连的三维结构进行简化,采用预设的传输走线模板建构第一芯片封装;所述仿真模块开启电磁场简化模式,在设计环境中对所述第一芯片封装进行仿真模拟,得到第一仿真参数;所述速度设计子模块根据所述第一仿真参数调整所述第一芯片封装,得到第二芯片封装。3.根据权利要求2所述的芯片封装电磁建模系统,其特征在于,所述设计模块还包括均衡设计子模块;所述均衡设计子模块获取所述第二芯片封装;所述仿真模块关闭电磁场简化模式,在设计环境中对所述第二芯片封装进行仿真模拟,得到第二仿真参数;所述均衡设计子模块根据所述第二仿真参数调整所述第二芯片封装,得到第三芯片封装。4.根据权利要求3所述的芯片封装电磁建模系统,其特征在于,所述设计模块还包括精确设计子模块;所述精确设计子模块获取所述第三芯片封装,取消芯片互连的结构简化,细化所述第三芯片封装的芯片走线布局,得到第四芯片封装;所述仿真模块关闭电磁场简化模式,在设计环境中对所述第四芯片封装进行仿真模拟,得到第三仿真参数;所述精确设计子模块根据所述第三仿真参数判断所述第四芯片封装是否符合要求,实现仿真工具和设计工具交互;若不符合要求,所述精确设计子模块重新调整芯片走线布局;若符合要求,即得到所述第四芯片封装。5.根据权利要求4所述的芯片封装电磁建模系统,其特征在于,所述设计模块还包括验证子模块,所述验证子模块用于判断所述第四芯片封装是否为所述合格芯片封装;所述验证子模块获取所述第四芯片封装的走线,判断走线是否满足要求;若满足走线要求,通过所述仿真模块调用所述第四芯片封装进行电磁场建模;所述验证子模块将模型结果传递给时域仿真工具进行时域波形的验证,判断时域眼图是否符合要求;

若满足时域眼图的判定要求,所述验证子模块进一步对所述第四芯片封装做物理验证,判断所述第四芯片封装是否合格;若合格,所述第四芯片封装即为所述合格芯片封装。6.一种芯片封装电磁建模方法,其特征在于,所述的芯片封装电磁建模方法包括:获取芯片封装的设计参数,通过设计模块完成芯片布局并建构第一芯片封装;在所述设计模块的设计环境中对所述第一芯片封装进行仿真模拟,得到仿真结果;根据所述仿真结果,优化改进所述芯片封装,并通过验证子模块的时域验证和物理验证,得到合格芯片封装。7.根据权利要求6所述的芯片封装电磁建模方法,其特征在于,建构所述第一芯片封装的方法包括:获取所述第一芯片封装的设计参数,实现芯片布局;通过速度设计子模块对芯片互连的三维结构进行简化;采用预设的传输走线模板布置走线,得到所述第一芯片封装;其中,芯片互连的三维结构简化包括:忽略金属平面孔,合并过地孔,去除悬浮地网络。8.根据权利要求6所述的芯片封装电磁建模方法,其特征在于,所述仿真结果包括第一仿真参数、第二仿真参数和第三仿真参数,获得所述第一仿真参数、所述第二仿真参数和所述第三仿真参数的方法包括:开启电磁场简化模式,在设计环境中对所述第一芯片封装进行仿真模拟,得到所述第一仿真参数;根据所述第一仿真参数调整所述第一芯片封装,得到第二芯片封装;关闭电磁场简化模式,在设计环境中对所述第二芯片封装进行仿真模拟,得到所述第二仿真参数;根据所述第二仿真参数调整所述第二芯片封装,得到第三芯片封装;取消芯片互连的结构简化,细化所述第三芯片封装的芯片走线布局,得到第四芯片封装;关闭电磁场简化模式,在设计环境中对所述第四芯片封装进行仿真模拟,得到所述第三仿真参数。9.根据权利要求8所述的芯片封装电磁建模方法,其特征在于,通过验证子模块的验证得到所述合格芯片封装的方法包括:根据所述第三仿真参数判断所述第四芯片封装是否符合要求;若不符合要求,重新调整芯片走线布局;若符合要求,即得到所述第四芯片封装;获取所述第四芯片封装的走线,判断走线是否满足要求;若满足走线要求,通过仿真模块调用所述第四芯片封装进行电磁场建模;所述验证子模块将模型结果传递给时域仿真工具进行时域波形的验证,判断时域眼图是否符合要求;若满足时域眼图的判定要求,所述验证子模块进一步对所述第四芯片封装做物理验证,判断所述第四芯片封装是否合格;若合格,所述第四芯片封装即为所述合格芯片封装。10.一种芯片封装电磁建模装置,其特征在于,所述芯片封装电磁建模装置包括设计模

块和仿真模块:所述设计模块完成芯片布局,建构芯片封装并根据所述芯片封装的仿真结果优化改进所述芯片封装,得到合格芯片封装;所述仿真模块在所述设计模块的设计环境中对所述芯片封装进行仿真模拟,将所述仿真结果传递给所述设计模块。

技术总结

本发明适用于芯片封装技术领域,提供了一种芯片封装电磁建模系统、方法和装置。一种芯片封装电磁建模系统,所述的芯片封装电磁建模系统包括设计模块和仿真模块:所述设计模块完成芯片布局,建构芯片封装并根据所述芯片封装的仿真结果优化改进所述芯片封装,得到合格芯片封装;所述仿真模块在所述设计模块的设计环境中对所述芯片封装进行仿真模拟,将所述仿真结果传递给所述设计模块。本发明通过在设计模块中进行仿真模拟,统一设计环境和仿真环境的数据,实现仿真工具和设计工具交互,避免了繁琐的数据交换过程,减少了人力和时间资源消耗;根据仿真结果优化芯片封装,提高芯片设置的合理性。的合理性。的合理性。

技术研发人员:蒋历国 凌峰 钟章民 代文亮

受保护的技术使用者:芯和半导体科技(上海)有限公司

技术研发日:2022.01.13

技术公布日:2022/5/30

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。