1.本实用新型涉及数字通信领域,具体涉及一种基于天脉操作系统的信号处理存储系统。

背景技术:

2.近年来,随着科学技术尤其是电子信息技术的飞速发展,人类对信号处理存储的需求也不断增加,信号处理存储系统已经被广泛的应用于军用机载电子系统,负责多路高速接口和低速接口信号数据处理、存储、控制等功能。高速信号处理存储技术的研究是整个处理存储系统的难点和重点。因此信号处理存储中的速度、实时性、可靠性以及存储特性都是这些领域所要研究和关注的问题。

3.目前基于进口操作系统软件的和硬件的信号处理存储系统,高速接口数量有限。现有处理存储系统对外接口有限,不能满足多路高速、低速接口同时存储。所以亟需一种多接口的信号处理存储系统,来满足高速、低速信号的处理和存储。

技术实现要素:

4.为解决现有技术中,信号处理存储系统对外接口有限,不能满足多路高速、低速接口同时存储的问题,本实用新型提出一种基于天脉操作系统的信号处理存储系统,采用fpga技术与rsio技术结合,通过在powerpc处理单元外设多个接口连接pcie单元和srio交换单元,实现对外设备的交互,通过在存储控制管理单元外设多个接口,实现对高速数据的存储,并通过设置lrmd连接器将各个单元连接起来,实现信号的采集、处理与存储。。

5.本实现上述目的,本实用新型具体内容如下:

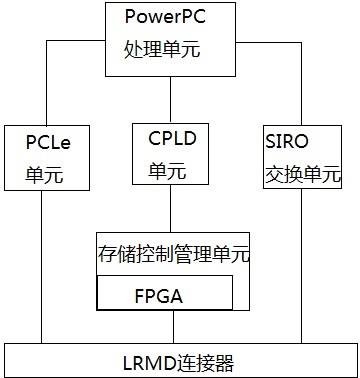

6.本实用新型提出一种基于天脉操作系统的信号处理存储系统,包括powerpc处理单元、存储控制管理单元、cpld单元、pcie单元、srio交换单元、lrmd连接器;

7.所述powerpc处理单元通过pcie1x线与pcie单元连接,通过1xrio接口、iic接口与srio交换单元连接,通过lbe接口与cpld单元连接;

8.所述存储控制管理单元通过4xrio接口、pcie线与srio交换单元连接,所述存储控制管理单元通过用于传输高速信号的gth接口,用于传输低速信号的lvds接口、rs485接口、rs232接口,用于采集低速信号的b码接口与lrmd连接器连接。

9.为了更好地实现本实用新型,进一步地,所述powerpc处理单元通过lbc接口外接有flash存储单元,通过ddr控制器接口外接有ddr存储单元;

10.所述存储控制管理单元通过hpio接口外接有ddr存储单元,通过pcie接口外接有ssd存储单元,通过lbc接口外接有用于存储控制管理单元代码加载的flash存储单元。

11.为了更好地实现本实用新型,进一步地,所述存储控制管理单元、powerpc处理单元均连接有phy控制单元;

12.所述phy控制单元通过变压器与lrmd连接器上的1000base-t接口连接;

13.所述存储控制管理单元还设置有用于数据下载的usb3.0接口。

14.为了更好地实现本实用新型,进一步地,所述pcie单元包括pcie桥、fc子卡、1394子卡、光模块;

15.所述powerpc处理单元通过pcie1x接口与pcie桥连接;所述pcie桥通过两个pcie1x接口分别与fc子卡、1394子卡连接;

16.所述1394子卡通过1394信号端口与lrmd连接器连接;

17.所述光模块通过两个rio接口分别与fc子卡和srio交换单元连接,通过fc接口、rio接口与lrmd连接器连接。

18.为了更好地实现本实用新型,进一步地,所述存储控制管理单元还设置有通用总线控制单元;

19.所述通用总线控制单元通过fifo接口与存储控制管理单元连接,通过can接口与lrmd连接器连接。

20.为了更好地实现本实用新型,进一步地,所述基于天脉操作系统的信号处理存储系统还包括前面板调试板;

21.所述前面板调试板与powerpc处理单元的jtag接口、rs232-0接口连接,并与存储控制管理单元的jtag接口连接。

22.为了更好地实现本实用新型,进一步地,所述基于天脉操作系统的信号处理存储系统还包括电源单元;

23.所述电源单元与lrmd连接器连接。

24.为了更好地实现本实用新型,进一步地,所述存储控制单元还外接有电压监测单元、通过iic接口外接有rtc单元。

25.为了更好地实现本实用新型,进一步地,所述cpld单元外接有fx706复位单元。

26.为了更好地实现本实用新型,更进一步地,所述ddr存储单元为ddr3。

27.本实用新型具有以下有益效果:

28.1)本实用新型设置的存储控制单元内设置有fpga芯片,所述fpga芯片为sram型fpga可编程逻辑芯片xc7vx690t-2ffg1930i,具有693120逻辑单元、高达52920kb bram块、3600 dsp片、24个13.1gth高速串行接口。支持pcie3.0硬核、srio软核。提供信号处理存储系统的1路4x srio、10路1xgth高速数据采集存储,完成b码、rs232、rs485信号的采集处理,通过千兆以太网完成存储数据的卸载,并与多核powerpc处理器进行可靠、高速的数据交互。

29.2)基于多核powerpc处理器架构的p2020双核处理器,该处理器包含两个高性能powerpc架构e500内核,每个内核具备32k字节的一级指令缓存和32k字节的一级数据缓存,处理器集成了512kb字节的二级缓存,同时,还具备2路串口、2路i2c、spi、sdxc、1路usb、通用并口等低速口。可支持2路sgmii千兆网、3路pcie、2路srio。该处理器为信号处理存储系统提供强大的协议解析运算能力和丰富的外设接口;

30.3)进一步的,为更好的实现本发明,对powerpc处理器单元进行了以下设计:

31.设计采用256m字节的nor flash,挂载到p2020处理器的lbs总线,作为系统存储空间,可用作存储应用程序和用户数据;

32.设计采用2gb,64bit ddr3存储器,挂载到p2020 ddr3控制器接口,作为天脉操作系统运行内存使用,提供软件的执行空间;

33.设计采用p2020的srio端口作为高速数据传输通道,用作与外部设备的高速数据交换,自检信息、电子标签、工作日志以及健康状态上报。

34.4)为更好的实现本实用新型,进一步的,对存储管理控制单元的fpga进行了以下设计:

35.设计采用2个2tb容量的vgrm100za321920-wq ssd存储盘做raid,总容量4tb,通过2路x4 pcie3.0接口连接,读写速率达到2.2gb/s;

36.设计采用srio软核作为fpga的高速数据采集存储通道,srio配置为x4模式,线速率为5gbps;

37.设计采用fpga对外引出10路gth用于高速数据采集存储;

38.设计采用fpga挂载1个128m nor flash实现fpga的代码加载。

39.设计采用fpga的hp io挂载2gb ddr3实现fpga的高速数据缓存功能。

40.设计采用rs485接口芯片max3096ese 、max3030eese ;rs232接口芯片max3232,lvds接口芯片max9122eue 实现fpga对外低速信号的采集。

附图说明

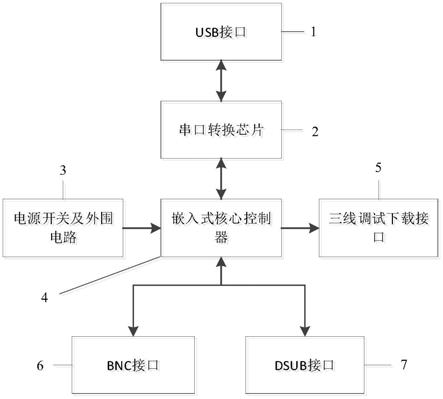

41.图1为本实用新型整体结构示意图;

42.图2为本实用新型存储控制管理单元结构示意图;

43.图3为本实用新型powerpc处理单元结构示意图;

44.图4为本实用新型pcie单元结构示意图;

45.图5为本实用新型电源结构示意图。

具体实施方式

46.为了更清楚地说明本实用新型实施例的技术方案,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,应当理解,所描述的实施例仅仅是本实用新型的一部分实施例,而不是全部的实施例,因此不应被看作是对保护范围的限定。基于本实用新型中的实施例,本领域普通技术工作人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

47.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“设置”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;也可以是直接相连,也可以是通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

48.实施例1:

49.本实用新型提出一种基于天脉操作系统的信号处理存储系统,包括powerpc处理单元、存储控制管理单元、cpld单元、pcie单元、srio交换单元、lrmd连接器;

50.所述powerpc处理单元通过pcie1x高速接口与pcie单元连接,通过1xrio高速接口、iic高速接口与srio交换单元连接,通过lbe接口与cpld单元连接;

51.所述存储控制管理单元通过4xrio高速接口、pcie高速接口与srio交换单元连接,通过gth高速接口、lvds低速接口、rs485低速接口、b码低速接口、rs232低速接口与lrmd连

接器连接,通过lbe接口与cpld单元连接。

52.为了更好地实现本实用新型,进一步地,所述powerpc处理单元通过lbc接口外接有flash存储单元,通过ddr控制器接口外接有ddr存储单元;

53.所述存储控制管理单元通过hpio高速接口外接有ddr存储单元,通过pcie高速接口外接有ssd存储单元。

54.工作原理:通过设置srio交换单元实现与外部设备的信号交互,通过srio交换单元与powerpc处理单元的1xrio接口连接启动系统,实现powerpc处理单元与外部设备的高速数据交换,通过powerpc处理单元启动系统后,可以读取外部设备的自检信息,通过1路srio 1x端口,实现powerpc处理器与外部设备本机自检信息上报,外部设备可查询本机的健康状态、电子标签以及工作日志。通过设置cpld单元将powerpc处理单元与存储控制管理单元连接,通过1路srio 4x端口,可以实现外部高速数据流存储到ssd存储单元,通过10路gth端口,可以实现外部高速数据流存储到ssd存储单元。

55.实施例2:

56.本实施例在上述实施例1的基础上,所述存储控制管理单元、powerpc处理单元均连接有phy控制单元;

57.所述phy控制单元通过变压器与lrmd连接器上的1000base-t端口连接;

58.所述存储控制管理单元还设置有用于数据下载的usb3.0接口。

59.工作原理:通过设置phy控制单元将powerpc处理单元和存储控制管理单元输出的信号传输到变压器,通过变压器与lrmd连接器连接,phy控制单元在发送数据的时候,收到的数据对phy来说,没有帧的概念,都是数据而不管什么地址,数据还是crc,每4bit就增加1bit的检错码,然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去,收数据时的流程反之。而且如果外部设备直接和phy控制单元相连的话,电磁感应和静电,很容易造成phy芯片的损坏。

60.设备接地方法不同也会对phy控制单元的工作造成影响,电网环境不同会导致双方的0v电平不一致,这样信号从a传到b,由于a设备的0v电平和b点的0v电平不一样,这样会导致很大的电流从电势高的设备流向电势低的设备。通过设置变压器,把phy控制单元送出来的差分信号用差模耦合的线圈耦合滤波以增强信号,并且通过电磁场的转换耦合到连接网线的另外一端。这样不但使网线和phy控制单元之间没有物理上的连接而换传递了信号,隔断了信号中的直流分量,还可以在不同0v电平的设备中传送数据。并且变压器设计时设计为耐2kv~3kv的电压,也起到了防雷感应的保护作用。

61.本实施例的其他部分与上述实施例1相同,故不再赘述。

62.实施例3:

63.本实施例在上述实施例1-2任一项的基础上,所述pcie单元包括pcie桥、fc子卡、1394子卡、光模块;

64.所述powerpc处理单元通过pcie1x接口与pcie桥连接;所述pcie桥通过两个pcie1x接口分别与fc子卡、1394子卡连接;

65.所述1394子卡通过1394信号端口与lrmd连接器连接;

66.所述光模块通过两个rio接口分别与fc子卡和srio交换单元连接,通过fc接口、rio接口与lrmd连接器连接。

67.工作原理:通过在fcie单元中设置光模块,将光信号转换为电信号,实现信号的光电转换。通过在光模块上设置rio接口,将采集到的高速信号进行光电转换后传输到srio交换单元,将srio交换单元作为高速数据采集存储的通道,通过4x srio接口将高速数据传输到存储控制管理单元进行处理后,传输到ssd存储单元完成高速数据的采集存储。

68.本实施例的其他部分与上述实施例1-2任一项相同,故不再赘述。

69.实施例4:

70.本实施例在上述实施例1-3任一项的基础上,所述存储控制管理单元还设置有通用总线控制单元;

71.所述通用总线控制单元通过fifo接口与存储控制管理单元连接,通过can接口与lrmd连接器连接。

72.工作原理:通过设置can总线连接can接口,并通过总线控制器控制mark地址的传输,并设置fifo接口将数据从can接口传输到存储控制管理单元中进行处理。

73.本实施例的其他部分与上述实施例1-3任一项相同,故不再赘述。

74.实施例5:

75.本实施例在上述实施例1-4任一项的基础上,所述基于天脉操作系统的信号处理存储系统还包括前面板调试板;

76.所述前面板调试板与powerpc处理单元的jtag接口、rs232-0接口连接,并与存储控制管理单元的jtag接口连接。

77.工作原理:通过设置前面板调试版,通过控制前面板调制板来控制powerpc处理单元、存储控制管理、电源,从而控制pcie单元和srio单元,并设置lrmd连接器将各个单元模块连接,实现了对整个系统数据的处理和存储。

78.本实施例的其他部分与上述实施例1-4任一项相同,故不再赘述。

79.实施例6:

80.本实施例在上述实施例1-5任一项的基础上,所述基于天脉操作系统的信号处理存储系统还包括电源单元;

81.所述电源单元与lrmd连接器连接。

82.工作原理:通过设置电源单元为系统提供28v的稳定电压。

83.本实施例的其他部分与上述实施例1-5任一项相同,故不再赘述。

84.实施例7:

85.本实施例在上述实施例1-6任一项的基础上,所述存储控制单元还外接有电压监测单元、通过iic接口外接有rtc单元。

86.所述cpld单元外接有fx706复位单元。

87.实施例8:

88.本实施例在上述实施例1-7任一项的基础上,所述ddr存储单元为ddr3。

89.工作原理:通过设置2gb,64bit ddr3存储器,挂载到p2020 ddr3控制器接口,作为天脉操作系统运行内存使用,提供软件的执行空间;通过设置2gb ddr3挂载到存储控制管理单元fpga的hp io接口,实现fpga的高速数据缓存功能。

90.通过设置256m字节的nor flash,挂载到powerpc处理单元p2020处理器的lbs总线,作为系统存储空间,可用作存储应用程序和用户数据;通过设置2个2tb容量的

vgrm100za321920-wq ssd存储盘做raid,总容量4tb,分别对控制管理数据和传感器数据进行存储,通过2路x4 pcie3.0接口连接,读写速率达到2.2gb/s;通过设置srio交换单元作为powerpc处理单元的软核,并为存储控制管理单元的fpga提供高速数据采集存储通道,其中,srio配置为x4模式,线速率为5gbps;通过在存储控制管理单元的fpga挂载1个128m nor flash实现存储控制管理单元的fpga的代码加载;通过在存储控制管理单元的fpga的hp io接口挂载2gb ddr3,实现存储控制管理单元fpga的高速数据缓存功能,通过在存储控制管理单元fpga设置rs485接口芯片max3096ese 、max3030eese ;rs232接口芯片max3232,lvds接口芯片max9122eue ,实现存储控制管理单元fpga对外部设备低速信号的采集。

91.本实施例的其他部分与上述实施例1-7任一项相同,故不再赘述。

92.以上所述,仅是本实用新型的较佳实施例,并非对本实用新型做任何形式上的限制,凡是依据本实用新型的技术实质对以上实施例所作的任何简单修改、等同变化,均落入本实用新型的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。