摄像元件及电子相机

1.本发明申请是国际申请日为2018年3月28日、国际申请号为pct/jp2018/012978、进入中国国家阶段的国家申请号为201880022491.6、发明名称为“摄像元件及电子相机”的发明申请的分案申请。

技术领域

2.本发明涉及摄像元件及电子相机。

背景技术:

3.已知在垂直信号线上进行像素信号混合的摄像装置(专利文献1)。但是,以往的摄像装置会出现无法获得与多个像素信号的平均接近的信号的情况。

4.现有技术文献

5.专利文献

6.专利文献1:日本特开2010-259027号公报

技术实现要素:

7.根据本发明的第1方案,摄像元件包括:沿第1方向配置的多个像素,其具有对光进行光电转换而生成电荷的光电转换部,并输出基于由所述光电转换部生成的电荷的信号;第1信号线,从多个所述像素中的一部分像素向该第1信号线输出信号;第2信号线,从多个所述像素中的其他像素向该第2信号线输出信号;以及运算部,其对输出至所述第1信号线且由所述一部分像素的信号混合而成的信号和输出至所述第2信号线的信号进行运算。

8.根据本发明的第2方案,电子相机包括:基于第1方案的摄像元件;以及图像生成部,其基于所述像素的信号生成图像数据。

附图说明

9.图1是示出第1实施方式的摄像装置的构成的框图。

10.图2是示出第1实施方式的摄像元件的像素构成的电路图。

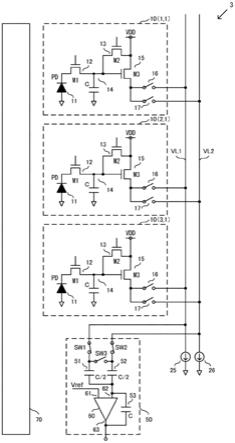

11.图3是示出第1实施方式的摄像元件的一部分构成的电路图。

12.图4是用于说明通过第1实施方式的摄像元件混合而成的像素信号的图。

13.图5是示意性示出由第1实施方式的摄像元件进行的像素信号的混合处理的图。

14.图6是示出第2实施方式的摄像元件的一部分构成的框图。

15.图7是示意性示出由第2实施方式的摄像元件进行的像素信号的混合处理的图。

16.图8是用于说明第2实施方式的摄像元件的一部分电路构成及动作例的图。

17.图9是用于说明第2实施方式的摄像元件的一部分电路构成及其他动作例的图。

18.图10是示出变形例1的摄像元件的一部分构成的电路图。

具体实施方式

19.(第1实施方式)

20.图1是示出第1实施方式的摄像装置的构成的框图。在图1中,示出作为第1实施方式的摄像装置的一例的电子相机1(以下称为相机1)的构成例。相机1包括摄像光学系统(成像光学系统)2、摄像元件3、控制部4、存储器5、显示部6及操作部7。摄像光学系统2具有包含调焦透镜(聚焦透镜)的多个镜头及光圈,将被摄体像成像于摄像元件3。此外,摄像光学系统2也可以能够从相机1装拆。

21.摄像元件3是例如cmos图像传感器。摄像元件3对通过摄像光学系统2形成的被摄体像进行拍摄。如后详述,具有光电转换部的多个像素以二维状配置在摄像元件3上。光电转换部由例如光电二极管(pd)构成。摄像元件3对射入的光进行光电转换而生成像素信号,并将生成的像素信号向控制部4输出。像素信号是基于通过光电转换部进行光电转换得到的电荷而生成的信号。

22.存储器5例如是存储卡等记录介质。在存储器5中记录图像数据等。向存储器5的数据写入或从存储器5的数据读取通过控制部4进行。显示部6显示基于图像数据的图像、快门速度或光圈值等与拍摄相关的信息及菜单画面等。操作部7包含释放按钮、电源开关等各种设定开关等,将与各操作对应的操作信号向控制部4输出。

23.控制部4由cpu、rom、ram等构成,基于控制程序对相机1的各部分进行控制。控制部4针对从摄像元件3输出的像素信号进行各种图像处理,生成图像数据。即,控制部4也是生成图像数据的图像生成部4,基于像素信号生成静态图像数据或动态图像数据。图像处理例如包含灰度转换处理、颜色插补处理、边缘增强处理等公知的图像处理。

24.控制部4进行独立读取摄像元件3的各像素的像素信号的处理(第1控制模式)和将多个像素的信号混合并读取的处理(第2控制模式)。例如,控制部4在进行高解析度的静态图像拍摄的情况下执行第1控制模式,独立读取各像素的像素信号。另外,控制部4在进行动态图像拍摄的情况下执行第2控制模式,将多个像素的像素信号混合并读取。

25.图2是示出第1实施方式的摄像元件3的像素构成的电路图。像素10包括光电转换部11、传输部12、复位部13、浮动扩散部(fd)14、增幅部15、第1选择部16和第2选择部17。光电转换部11是光电二极管pd,具有将射入的光转换为电荷并对光电转换得到的电荷进行蓄积的功能。

26.传输部12由通过驱动信号φtx控制的晶体管m1构成,将由光电转换部11进行光电转换得到的电荷向fd14传输。即,传输部12在光电转换部11与fd14之间形成电荷传输通路。晶体管m1是传输晶体管。fd14的电容c对传输到fd14的电荷进行蓄积(保持)。fd14也是蓄积电荷的蓄积部14。

27.增幅部15使基于蓄积在fd14的电容c中的电荷的信号增幅并输出。增幅部15由漏极(端子)及栅极(端子)分别与电源vdd、fd14连接的晶体管m3构成。另外,晶体管m3的源极(端子)经由第1选择部16与第1垂直信号线vl1连接,并经由第2选择部17与第2垂直信号线vl2连接。增幅部15以后述的电流源(图3的电流源25、26)为负载电流源,作为源极跟随器电路的一部分发挥作用。晶体管m3是增幅晶体管。复位部13由通过驱动信号φrs控制的晶体管m2构成,对电容c的电荷进行复位以使fd14的电压复位。晶体管m2是复位晶体管。

28.第1选择部16由晶体管构成,也是使增幅部15与第1垂直信号线vl1连接或切断的

第1连接部16。第1选择部16的晶体管在导通状态的情况下,将来自增幅部15的信号向第1垂直信号线vl1输出。另外,第2选择部17由晶体管构成,也是使增幅部15与第2垂直信号线vl2连接或切断的第2连接部17。第2选择部17的晶体管在导通状态的情况下,将来自增幅部15的信号输出至第2垂直信号线vl2。构成第1选择部16的晶体管是第1选择晶体管,构成第2选择部17的晶体管是第2选择晶体管。

29.图3示出沿作为第1方向的列方向(垂直方向)及与第1方向交叉的第2方向即行方向(水平方向)配置的多个像素10中的、沿列方向配置的多个像素列的一个像素列的一部分。其他像素列的构成也与图3的像素列的构成相同。摄像元件3包括多个像素10、运算部50和垂直控制部70。此外,垂直控制部70针对多个像素列共用设置。

30.另外,在摄像元件3上,针对沿列方向即纵向排列的多个像素10的列即像素列,设置第1垂直信号线vl1及第2垂直信号线vl2。另外,针对第1垂直信号线vl1设置第1电流源25,针对第2垂直信号线vl2设置第2电流源26。此外,针对第1垂直信号线vl1及第2垂直信号线vl2设置运算部50。此外,在图3所示的例子中,为了简化说明,关于像素10仅示出行方向1像素

×

列方向3像素,摄像元件3具有例如几百万像素~几亿像素或更多像素。另外,在图3中,将上端的像素10设为像素10(1,1),将中央的像素10设为像素10(2,1),将下端的像素10设为像素10(3,1)。

31.第1电流源25经由第1垂直信号线vl1与各像素10连接,第2电流源26经由第2垂直信号线vl2与各像素10连接。第1电流源25及第2电流源26生成用于从各像素10读取信号的电流。第1电流源25将所生成的电流向第1垂直信号线vl1和各像素10的第1选择部16及增幅部15供给。同样地,第2电流源26将所生成电流向第2垂直信号线vl2和各像素10的第2选择部17及增幅部15供给。此外,在本实施方式中,第1电流源25供给的电流值与第2电流源26供给的电流值大致相同。

32.运算部50包含放大器60、电容51、52、53、开关sw1、sw2、sw3而构成,对输入至电容51的信号和输入至电容52的信号进行加法运算。开关sw1、sw2、sw3分别由晶体管构成,通过垂直控制部70进行通断控制。

33.电容51是一个端子经由开关sw1与第1垂直信号线vl1连接,另一端子与放大器60的输入端子62连接的电容(输入电容)。电容52是一个端子经由开关sw2与第2垂直信号线vl2连接,另一端子与放大器60的输入端子62连接的电容(输入电容)。另外,电容53是一个端子与放大器60的输入端子62连接,另一端子与放大器60的输出端子63连接的电容(反馈电容)。电容53具有电容值c,电容51、52分别具有电容值c一半的电容值即1/2c的电容值。向放大器60的输入端子61输入作为恒定电压的基准信号vref。

34.运算部50从输出端子63输出将输入至电容51的信号与输入至电容52的信号相加平均得到的信号。即,运算部50是将所输入的多个信号相加的加法部50。从运算部50输出的信号在由未图示的模拟/数字转换部(ad转换部)等实施了信号处理后,被向相机1的控制部4输出。

35.垂直控制部70基于来自相机1的控制部4的信号将上述驱动信号φtx向各像素10的传输部12供给,并将驱动信号φrs向各像素10的复位部13供给。另外,垂直控制部70分别向第1选择部16及第2选择部17供给驱动信号,分别对第1选择部16及第2选择部17进行通断控制。更详细来说,垂直控制部70向第1选择部16及第2选择部17各自的晶体管的栅极供给

驱动信号,使晶体管成为打开状态(连接状态、导通状态、短路状态)或关闭状态(切断状态、非导通状态、开放状态、截止状态)。按照这种方式,垂直控制部70向各像素10供给驱动信号,对各像素10的动作进行控制。

36.接下来说明第1控制模式。摄像元件3在通过控制部4设定了第1控制模式的情况下,从摄像元件3的全部像素10独立读取像素信号。垂直控制部70以行单位从最上行像素10到最下行像素10(在图3中为从像素10(1,1)到像素10(3,1))依次选择摄像元件3的像素10,并依次从像素10读取像素信号。以下进一步详细说明第1控制模式情况下的像素信号读取方法。

37.垂直控制部70将第1行像素10(1,1)的第1选择部16设为导通状态,将像素10(1,1)的第2选择部17设为截止状态。垂直控制部70将与第1行不同的其他行像素10的第1选择部16及第2选择部17分别设为截止状态。在图3中,像素10(2,1)及像素10(3,1)的第1选择部16及第2选择部17均被设为截止状态。另外,垂直控制部70将运算部50的开关sw1及开关sw3均设为导通状态,将开关sw2设为截止状态。

38.基于由第1行像素10(1,1)的光电转换部11生成的电荷的像素信号,经由像素10(1,1)的第1选择部16被读取至第1垂直信号线vl1。由于开关sw1、sw3均为导通状态,因此,输出至第1垂直信号线vl1的像素10(1,1)的像素信号被分别输入至电容51及电容52。运算部50以将分别输入至电容51及电容52的像素10(1,1)的像素信号相加平均得到的信号为像素10(1,1)的像素信号,从输出端子63输出。

39.在读取来自第1行像素10的像素信号之后,垂直控制部70将第2行像素10(2,1)的第1选择部16设为导通状态,将像素10(2,1)的第2选择部17设为截止状态。另外,垂直控制部70将与第2行不同的其他行像素10的第1选择部16及第2选择部17分别设为截止状态。像素10(2,1)的像素信号经由像素10(2,1)的第1选择部16被读取至第1垂直信号线vl1。运算部50从输出端子63输出将输入至电容51及电容52的像素10(2,1)的像素信号相加平均得到的信号。

40.同样地,在读取来自第2行像素10的像素信号之后,垂直控制部70将第3行像素10(3,1)的第1选择部16设为导通状态,将像素10(3,1)的第2选择部17设为截止状态。另外,垂直控制部70将与第2行不同的其他行像素10的第1选择部16及第2选择部17分别设为截止状态。由此,像素10(3,1)的像素信号被读取至第1垂直信号线vl1,并被分别输入至电容51及电容52。运算部50从输出端子63输出将输入至电容51及电容52的像素10(3,1)的像素信号相加平均得到的信号。

41.按照这种方式,在第1控制模式的情况下,在摄像元件3中,以行单位依次选择像素10,进行从各像素10向第1垂直信号线vl1的像素信号读取。依次从各像素10输出的像素信号在通过运算部50及ad转换部等实施了信号处理后被向控制部4输出。控制部4使用从摄像元件3输出的全部像素10的像素信号,生成图像数据(例如静态图像数据)。

42.此外,对将像素10的像素信号读取至第1垂直信号线vl1的例子进行了说明,但在将第1选择部16设为截止状态、将第2选择部17设为导通状态的情况下,能够将像素信号从像素10读取至第2垂直信号线vl2。在该情况下,垂直控制部70将运算部50的开关sw2及开关sw3均设为导通状态,将开关sw1设为截止状态。

43.此外,对于两行像素,也可以将一行像素的像素信号读取至第1垂直信号线vl1,与

此同时将另一行像素的像素信号读取至第2垂直信号线vl2。在该情况下,能够通过针对每个像素列设置两个运算部50,同时(并行地)对向第1垂直信号线vl1输出的像素信号和输出至第2垂直信号线vl2的像素信号进行信号处理,并向控制部4输出。在图3中,例如,垂直控制部70将第1行像素10(1,1)的第1选择部16设为导通状态,将像素10(1,1)的第2选择部17设为截止状态,并且,将第2行像素10(2,1)的第1选择部16设为截止状态,将像素10(1,1)的第2选择部17将设为导通状态。由此,向第1垂直信号线vl1读取像素10(1,1)的像素信号,向第2垂直信号线vl2读取像素10(2,1)的像素信号。在第1行及第2行像素的同时读取完成时,进行从第3行及第4行像素的同时读取,进而依次进行从以后相互邻接的奇数行及偶数行像素的同时读取。按照这种方式,能够同时进行两行像素的像素信号读取。

44.接下来说明第2控制模式。摄像元件3在通过控制部4设定了第2控制模式的情况下,将多个像素10的信号混合(合成)并读取。例如,摄像元件3将沿列方向配置的三个像素10各自的像素信号混合,并将混合而成的像素信号向控制部4输出。即,摄像元件3将列方向的每三个像素的信号混合并读取。在图3所示的例子中,摄像元件3将像素10(1,1)、像素10(2,1)、像素10(3,1)各自的像素信号混合,并将该混合而成的像素信号向控制部4输出。像素10(2,1)是成为以上混合对象的三个像素10中的中央位置的像素。在摄像元件3中,在生成将多个像素10的信号混合而成的像素信号时,以获得对中央位置的像素10的像素信号加权最大的像素信号的方式,控制来自各像素10的像素信号读取(方法)。以下进一步详细说明第2控制模式情况下的像素信号读取方法。

45.垂直控制部70将第1行及第3行像素10(1,1)、(3,1)的第1选择部16设为导通状态,将第2选择部17将设为截止状态。另外,垂直控制部70将第2行像素10(2,1)的第1选择部16设为截止状态,将像素10(2,1)的第2选择部17设为导通状态。此外,垂直控制部70将运算部50的开关sw1及开关sw2均设为导通状态,将开关sw3设为截止状态。

46.像素10(1,1)及像素10(3,1)各自的第1选择部16成为导通状态,从而像素10(1,1)及像素10(3,1)各自的增幅部15的源极端子与第1垂直信号线vl1电连接。与第1垂直信号线vl1连接的第1电流源25的电流被向像素10(1,1)和像素10(3,1)分流(分配)。在第1垂直信号线vl1中,像素10(1,1)的像素信号与像素10(3,1)的像素信号混合,成为混合像素信号。

47.在该情况下,在像素10(1,1)与像素10(3,1)各自的fd14的电位差小的情况下,第1电流源25向像素10(1,1)和像素10(3,1)供给大致相同大小的电流。由此,输出至第1垂直信号线vl1的混合像素信号成为与像素10(1,1)及像素10(3,1)各自的fd14的电位的平均(值)对应的信号电平(电压)的信号。

48.在像素10(1,1)和像素10(3,1)各自的fd14的电位差大的情况下,第1电流源25的电流大部分流向fd14的电位较高一方的像素增幅部15。因此,在以第1垂直信号线vl1进行信号混合的情况下,与fd14的电位较低一方的像素信号相比,fd14的电位较高一方的像素信号的权重增大。即,输出至第1垂直信号线vl1的混合像素信号没有成为与像素10(1,1)及像素10(3,1)各自的fd14的电位的平均对应的信号电平,而是成为与fd14的电位较高一方的像素fd14的电位对应的信号电平接近的信号。

49.中央位置的像素10(2,1)通过使其第2选择部17成为导通状态,从而与第2垂直信号线vl2电连接。由于像素10(1,1)及像素10(3,1)的第2选择部17是截止状态,因此仅中央位置的像素10(2,1)与第2垂直信号线vl2连接。因此,第2电流源26的电流未被分流,而是全

部流向中央位置的像素10(2,1)的第2选择部17及增幅部15。由此,向第2垂直信号线vl2输出与中央位置的像素10(2,1)的fd14的电位对应的像素信号。

50.经由第1垂直信号线vl1及开关sw1向运算部50的电容51输出由像素10(1,1)的信号与像素10(3,1)的信号混合而成的混合像素信号。经由第2垂直信号线vl2及开关sw2向运算部50的电容52输入中央位置的像素10(2,1)的像素信号。运算部50从输出端子63输出将输入至电容51的混合像素信号与输入至电容52的中央位置的像素10(2,1)的像素信号相加平均得到的像素信号(加算像素信号)。按照这种方式,从输出端子63输出的加算像素信号成为由像素10(1,1)、像素10(2,1)、像素10(3,1)的信号混合而成的信号。

51.如上所述,来自第1电流源25的电流被向像素10(1,1)和像素10(3,1)分流供给,由像素10(1,1)的像素信号与像素10(3,1)的像素信号混合而成的混合像素信号被读取至第1垂直信号线vl1。向中央位置的像素10(2,1)供给来自第2电流源26的全部电流,像素10(2,1)的像素信号被读取至第2垂直信号线vl2。然后,在运算部50中,生成将像素10(1,1)及像素10(3,1)的混合像素信号与像素10(2,1)的像素信号相加平均得到的加算像素信号。因此,能够获得对三个像素中的中央位置的像素10(2,1)的像素信号进行最大加权的加算像素信号。

52.通过上述像素信号读取方法,进行来自第1行~第3行这3行像素10的加算像素信号读取。垂直控制部70在读取来自第1行~第3行像素10的加算像素信号之后,进行来自第4行~第6行像素10的加算像素信号读取。按照这种方式,在第2控制模式下,每3行依次进行加法运算像素信号读取。依次从运算部50输出的列方向的三个像素信号混合而成的加算像素信号,在通过ad转换部等实施了信号处理后被向控制部4输出。控制部4使用从摄像元件3输出的加算像素信号,生成图像数据(例如动态图像数据)。

53.按照这种方式,在第2控制模式下,垂直控制部70将作为混合对象的列方向的三个像素中的上下像素各自的像素信号读取至第1垂直信号线vl1并混合,将中央位置的像素的像素信号读取至第2垂直信号线vl2。然后,运算部50生成将输出至第1垂直信号线vl1的混合像素信号与输出至第2垂直信号线vl2的中央位置的像素的像素信号相加平均得到的加算像素信号。由此,在本实施方式中,在将沿列方向配置的多个像素10的信号混合的情况下,能够对中央位置的像素10的像素信号进行最大加权。按照这种方式,能够利用将中央位置的像素周围(上下)像素的像素信号加入到中央位置的像素的像素信号中得到的加算像素信号来生成图像数据。

54.此外,在第2控制模式下,也可以将像素10(1,1)的像素信号与像素10(3,1)的像素信号读取至第2垂直信号线vl2并混合,将中央位置的像素10(2,1)的像素信号读取至第1垂直信号线vl1。在该情况下,运算部50对输出至第2垂直信号线vl2的混合像素信号和输出至第1垂直信号线vl1的中央位置的像素10的像素信号进行相加平均。

55.另外,在上述实施方式中,以能够对作为混合对象的列方向的多个像素的数量或位置、权重的比率进行变更的方式,在各像素10设有第1选择部16和第2选择部17这两个选择部。但是,例如,在作为混合对象的列方向的多个像素的数量是3个且其位置也固定的情况下,由于不从像素10(1,1)及像素10(3,1)向第2垂直信号线vl2读取像素信号,因此也可以将像素10(1,1)及像素10(3,1)设为不具有第2选择部17的像素构成。

56.以下与对比例对比来说明获得对中央位置的像素10的像素信号实施了加权的加

算像素信号的情况。在将图3的像素10(1,1)、(2,1)、(3,1)的fd14的电压分别设为vfda、vfdb、vfdc时,这些像素各自的像素信号的电压(输出电压)vouta、voutb、voutc能够以下式(1)~(4)表示。

57.vouta=vfda-vth-δov

…

(1)

58.voutb=vfdb-vth-δov

…

(2)

59.voutc=vfdc-vth-δov

…

(3)

60.δov=√(2

×

id/β)

…

(4)

61.在此,vth是像素10的增幅部15的晶体管m3的阈值电压,id是流入增幅部15的晶体管m3的电流(值)。另外,β是根据栅极氧化膜的膜厚、栅极宽度、栅极长度及载流子迁移率求出的值。

62.由上述的式(1)~(3)表示的输出电压vouta、voutb、voutc为在从像素10(1,1)、(2,1)、(3,1)独立读取到像素信号的情况下输出的像素信号的电压。即,输出电压vouta、voutb、voutc是在第1控制模式的情况下依次从像素10(1,1)、(2,1)、(3,1)输出至第1垂直信号线vl1的电压。

63.另外,在第2控制模式的情况下,输出至第1垂直信号线vl1的电压vout1成为基于像素10(1,1)及像素10(3,1)的混合像素信号的电压,因此能够以下式(5)、(6)表示。

64.vout1=(vfda vfdc)/2-vth-(1/2)√(δov

2-δvfd22)

…

65.(5)

66.δvfd2=(vfda-vfdc)2…

(6)

67.此外,在第2控制模式的情况下,输出至第2垂直信号线vl2的电压vout2成为来自像素10(2,1)的输出电压voutb,因此能够以下式(7)表示。

68.vout2=voutb=vfdb-vth-δov

…

(7)

69.将像素10(1,1)、(2,1)、(3,1)的像素信号混合而成的信号、即由运算部50生成的加算像素信号的电压vout,成为将式(5)的电压vout1与式(7)的电压vout2相加平均得到的值,能够以下式(8)表示。

70.vout={[(vfda vfdc)/2-vth-(1/2)√(δov

2-δvfd22)]

[0071]

[vfdb-vth-δov]}/2

…

(8)

[0072]

图4的(a)是表示输出电压vouta、voutb、voutc与加算像素信号的输出电压vout的关系的图。图4的(b)示出在第2控制模式下分别流入像素10(1,1)、(2,1)、(3,1)的增幅部15的电流(ida、idb、idc)。

[0073]

在图4的(a)中,纵轴表示输出电压的大小,横轴表示像素10(2,1)的fd14的电压vfdb的大小。另外,图4的(a)中的vouta是在将vfda设为固定值v2的情况下的像素10(1,1)的输出电压,voutc是在将vfdc设为固定值v1的情况下的像素10(3,1)的输出电压。voutb表示在使vfdb变化了的情况下的像素10(2,1)的输出电压voutb。

[0074]

在图4的(b)中,纵轴表示流入像素10的增幅部15的电流的大小,横轴表示像素10(2,1)的fd14的电压vfdb的大小。另外,在图4的(b)中,ida表示在将vfda设为固定值v2的情况下的像素10(1,1)流入增幅部15的电流,idc表示在将vfdc设为固定值v1的情况下流入像素10(3,1)的增幅部15的电流。另外,idb是在使vfdb变化了的情况下流入像素10(2,1)的增幅部15的电流。

[0075]

如上所述,在第2控制模式下,第1电流源25的电流对应于像素10(1,1)及像素10(3,1)各自的fd14的电压而分开流入像素10(1,1)和像素10(3,1)。在图4的(a)、(b)所示的例子中,vfda比vfdc大,因此ida也比idc大。另外,在第2控制模式下,第2电流源26的电流全部流入中央位置的像素10(2,1)。另外,如上所述,第1电流源25及第2电流源26各自供给的电流的大小(电流值)大致相同。因此,ida、idb、idc的比在1:1:0~0:1:1之间变化。因此,由于ida及idc不超过idb,因此能够获得对中央位置的像素10(2,1)实施了加权的加算像素信号。

[0076]

与此相对,对比例在第1垂直信号线vl1中将像素10(1,1)、(2,1)、(3,1)这三个像素的像素信号混合。即,以上三个像素10的第1选择部16均被设为导通状态,第2选择部17均被设为截止状态。在该情况下,像素10(1,1)、(2,1)、(3,1)的像素信号混合而成的信号的电压vout能够以下式(9)、(10)表示。

[0077]

vout=(vfda vfdb vfdc)/3-vth-(1/3)√(δov

2-δvfd32)

[0078]

…

(9)

[0079]

δvfd3=(vfda-vfdb)2 (vfdb-vfdc)2 (vfdc-vfda)2[0080]

…

(10)

[0081]

图4的(c)、(d)是示出对比例情况下的输出电压及电流的图。此外,在从像素10(1,1)、(2,1)、(3,1)独立读取到像素信号的情况下的输出电压vouta、voutb、voutc,与图4的(a)的情况相同。在对比例的情况下,第1电流源25的电流大部分流向三个像素10中的fd14的电位最高的像素的增幅部15。因此,如图4的(d)所示,在vfdb<v2(=vfda)的范围内,ida最大,在vfdb>v2(=vfda)的范围内,idb最大。其结果为,如图4的(c)所示,输出电压vout在vfdb<v2(=vfda)的范围内为接近vouta的值,在vfdb>v2(=vfda)的范围内为接近voutb的值。

[0082]

图4的(a)、(c)所示的理想平均值是将像素10(1,1)、(2,1)、(3,1)的像素信号混合而成的信号的理想输出电压,由下式(11)表示。

[0083]

理想平均值=(vouta voutb voutc)/3=(vfda vfdb vfdc)/3-vth-δov

…

(11)

[0084]

将图4的(a)所示的本实施方式情况下的输出电压vout与图4的(c)所示的对比例的情况下的输出电压vout进行对比,可知本实施方式的情况为接近理想平均值的值。另外,对比例情况下的输出电压vout在vfdb<v2(=vfda)的范围内为接近vouta的值,并非对中央位置的像素10(2,1)的voutb加权最大的值。与此相对,在本实施方式中,能够获得对中央位置的像素10(2,1)的像素信号实施了加权的输出电压vout。

[0085]

接下来,说明对沿列方向配置的4个以上像素的像素信号进行混合处理的例子。在图3所示的例子中,对列方向的三个像素10的像素信号进行混合处理,但作为混合对象的像素10的数量也可以是任意的。图5是示意性示出列方向的多个像素10的像素信号的混合处理的图。图5的(a)是关于三个像素10、第1及第2垂直信号线vl1、vl2与第1及第2电流源25、26的关系,示意性地示出将图3所示的三个像素的像素信号混合的情况下的构成的图。

[0086]

在图5的(a)中,将中央位置的像素的上下的像素10a、10c各自的像素信号读取至第1垂直信号线vl1并混合,将中央位置的像素10b的像素信号读取至第2垂直信号线vl2。读取至第1垂直信号线vl1的混合像素信号与读取至第2垂直信号线vl2的中央位置的像素10b的像素信号如上所述,通过运算部50进行相加平均。

[0087]

图5的(b)、(c)是示出将列方向的5个像素10的像素信号混合的情况下的像素信号读取方法的图。在图5的(b)所示的例子中,将除了中央位置以外的像素10a、10b、10d、10e各自的像素信号读取至第1垂直信号线vl1并混合,将中央位置的像素10c的像素信号读取至第2垂直信号线vl2。读取至第1垂直信号线vl1的4个像素10a、10b、10d、10e的混合像素信号与读取至第2垂直信号线vl2的中央位置的像素10c的像素信号通过运算部50相加平均。

[0088]

按照这种方式,在对5个像素10的像素信号进行混合的情况下,仅将中央位置的像素10c的像素信号读取至第2垂直信号线vl2,将其余4个像素10a、10b、10d、10e的像素信号读取至第1垂直信号线vl1而进行混合处理。因此,针对中央位置的像素10c的像素信号的权重,与针对其他4个像素10a、10b、10d、10e的像素信号的权重相比,能够设得足够大。

[0089]

此外,通过将第2电流源26生成的电流值设为大于第1电流源25生成的电流值,从而能够使针对中央位置的像素10c的像素信号的权重与针对其他4个像素的像素信号的权重相比更大。在图5的(a)所示的3个像素的情况下也同样地,通过使第2电流源26生成的电流值比第1电流源25生成的电流值大,从而能够使针对中央位置的像素10b的像素信号的权重更大。

[0090]

在图5的(c)所示的例子中,针对列方向的像素列,在第1及第2垂直信号线vl1、vl2的基础上,还分别设有第3垂直信号线vl3和与第3垂直信号线vl3连接的第3电流源27。将中央位置的像素10c的像素信号读取至第3垂直信号线vl3,将与中央位置的像素10c相邻的上下附近的像素10b、10d各自的像素信号读取至第2垂直信号线vl2并混合。将分别与以上的上下像素10b、10d相邻的周边像素10a、10e各自的像素信号读取至第1垂直信号线vl1并混合。在运算部50中,对第1垂直信号线vl1的混合像素信号、第2垂直信号线vl2的混合像素信号和第3垂直信号线vl3的中央像素10c的像素信号进行相加平均,生成加算像素信号。

[0091]

按照这种方式,仅将中央位置的像素10c的像素信号读取至第3垂直信号线vl3,将附近像素10b、10d的像素信号读取至第2垂直信号线vl2并混合,将周边像素10a、10e各自的像素信号读取至第1垂直信号线vl1并混合。因此,能够将针对中央位置的像素10c的像素信号赋予的权重设为比针对其他4个像素10a、10b、10d、10e的像素信号赋予的权重大。

[0092]

在图5的(c)的情况下,也可以使第2电流源26生成的电流值比第1电流源25生成的电流值大。由此,能够将针对两个附近像素10b、10d的像素信号赋予的权重设为比针对两个周边像素10a、10e的像素信号赋予的权重大。在该情况下,优选第3电流源27生成的电流值与第2电流源26生成的电流值相比相同或较大。

[0093]

图5的(d)是示出将列方向的4个像素10的像素信号混合的情况下的像素信号的读取方法的图。第2电流源26生成的电流值设定为大于第1电流源25生成的电流值。将中央的两个像素10b、10c的像素信号读取至第2垂直信号线vl2并混合,将中央的两个像素10b、10c的上下的像素10a、10d的像素信号读取至第1垂直信号线vl1并混合。然后,在运算部50中,基于像素10b、10c的混合像素信号与基于像素10a、10d的混合像素信号被相加平均,生成加算像素信号。如上所述,第2电流源26生成的电流值比第1电流源25生成的电流值大,因此,能够使针对中央的两个像素10b、10c的像素信号的权重比针对上下像素10a、10d的像素信号的权重大。

[0094]

根据上述实施方式,能够获得以下作用效果。

[0095]

(1)摄像元件3包括:多个像素10,其沿第1方向配置,并具有对射入光进行光电转

换以生成电荷的光电转换部11;第1信号线(第1垂直信号线vl1),其混合有从多个像素10中的一部分输出的信号;第2信号线(第2垂直信号线vl2),从多个像素10中的另一部分向该第二信号线输出信号;以及运算部50,其对输出至第1信号线的信号和输出至第2信号线的信号进行运算。由于采用这种方式,因此,在将多个像素的像素信号混合并读取的情况下,能够获得与多个像素信号的平均接近的信号。另外,在将多个像素信号混合的情况下,无论像素的位置如何,均能够防止对fd的电位高的像素的像素信号实施加权。其结果为,能够抑制像素信号的品质降低。

[0096]

(2)另一部分的像素10包含第1像素(在图3中为像素10(2,1)),一部分多个像素10包含以夹着第1像素的方式配置的第2像素及第3像素(在图3中为像素10(1,1)及像素10(3,1))。由于采用这种方式,因此,在对多个像素的像素信号进行混合的情况下,能够获得针对中央位置的像素的像素信号实施了加权的信号。因此,能够使用将中央位置的像素周围(上下)的像素的像素信号加入到中央位置的像素的像素信号中的像素信号来生成图像数据。其结果为,能够防止被加权的像素的位置不均匀,能够防止使用像素信号生成的图像的画质降低。

[0097]

(第2实施方式)

[0098]

参照附图说明第2实施方式的摄像装置及摄像元件。第2实施方式的摄像元件3在通过控制部4设定了第1控制模式的情况下与第1实施方式相同,从全部像素10独立读取像素信号。另外,第2实施方式的摄像元件3在通过控制部4设定了第2控制模式的情况下,将行方向及列方向的多个像素10的信号混合并读取。例如,摄像元件3以3像素

×

3像素的9个像素为一组进行信号混合并读取。在图6所示的例子中,摄像元件3将像素10(1,1)~像素10(3,3)各自的信号混合,并将该混合而成的像素信号向控制部4输出。在摄像元件3中,在生成将行方向及列方向的多个像素10的信号混合而成的像素信号时,以获得对来自中央位置的像素的像素信号加权最大的像素信号的方式,控制各像素10的像素信号读取。

[0099]

图6是示出第2实施方式的摄像元件3的一部分构成的框图。摄像元件3包括多个像素10(3行

×

3列的像素)、每个像素列的第1及第2垂直信号线vl1(vl1a~vl1c)、vl2(vl2a~vl2c)、针对第1垂直信号线vl1的第1电流源25(25a~25c)、针对第2垂直信号线vl2的第2电流源26(26a~26c)、水平混合部40、运算部50(50a~50c)、ad转换部80(80a~80c)、输出部90和垂直控制部70。

[0100]

针对第1垂直信号线vl1(vl1a~vl1c)及第2垂直信号线vl2(vl2a~vl2c)设置运算部50(50a~50c)。各运算部50a~50c与图3所示的运算部50相同,对沿列方向配置的多个像素的像素信号进行加法运算。运算部50b在上述列方向的多个像素的像素信号的加法运算的基础上,如后所述,对3行

×

3列的9个像素的像素信号进行加法运算。另外,针对运算部50(50a~50c)设置ad转换部80(80a~80c)。输出部90针对多个ad转换部80共用设置。此外,在图6中,将左上角的像素10设为第1行第1列的像素10(1,1),将右下角的像素10设为第3行第3列的像素10(3,3),图示出从像素10(1,1)到像素10(3,3)的9个像素10。

[0101]

水平混合部40见后述,其由多个开关构成,进行输出至第1垂直信号线vl1及第2垂直信号线vl2的像素信号间的混合。运算部50进行经由水平混合部40输入的信号间的加法运算。ad转换部80将从运算部50输出的信号转换为数字信号,并将转换后的数字信号向输出部90输出。输出部90具有未图示的信号处理部,针对从ad转换部80输入的信号进行相关

双采样或信号量修正处理等信号处理,并向电子相机1的控制部4输出。

[0102]

垂直控制部70具有垂直混合控制部71、水平混合控制部72和加法运算控制部73。垂直混合控制部71对各像素10的第1选择部16(参照图3)及第2选择部17(参照图3)进行通断控制,对沿列方向(垂直方向)配置的多个像素间的像素信号的混合处理进行控制。水平混合控制部72对构成水平混合部40的多个开关进行通断控制,对沿行方向(水平方向)配置的多个像素间的像素信号的混合处理进行控制。加法运算控制部73通过对运算部50的多个开关进行通断控制,从而将切换与第1垂直信号线vl1及第2垂直信号线vl2和运算部50连接的电容。

[0103]

图7的(a)是示意性示出由第2实施方式的摄像元件3进行的3行

×

3列的9个像素的像素信号的混合处理的例子的图。此外,在图7的(a)及后述的图7的(b)所示的例子中,为了简化说明,像素10仅示出3像素

×

3像素,运算部50仅示出运算部50b。另外,在图7的(a)所示的例子中,水平混合部40具有使第1垂直信号线vl1a与第1垂直信号线vl1b连接或切断的开关swa,和使第1垂直信号线vl1b与第1垂直信号线vl1c连接或切断的开关swb。

[0104]

运算部50b具有第1输入部ia~第6输入部if。第1输入部ia与第1垂直信号线vl1a连接,第2输入部ib与第2垂直信号线vl2a连接。第3输入部ic与第1垂直信号线vl1b连接,第4输入部id与第2垂直信号线vl2b连接,第5输入部ie与第1垂直信号线vl1c连接,第6输入部if与第2垂直信号线vl2c连接。

[0105]

垂直控制部70(参照图6)将水平混合部40的开关swa及开关swb均设为导通状态。另外,垂直控制部70将3像素

×

3像素中的中央位置的像素10e的像素信号读取至第2垂直信号线vl2b。另外,垂直控制部70将中央位置的像素10e周围的8个像素10a~10d、10f~10i的像素信号读取至第1垂直信号线vl1。详细来说,垂直控制部70将第1列像素10a、10b、10c各自的像素信号读取至第1垂直信号线vl1a,将第2列像素10d、10f各自的像素信号读取至第1垂直信号线vl1b,将第3列像素10g、10h、10i各自的像素信号读取至第1垂直信号线vl1c。由此,在第1垂直信号线vl1a中,第1列像素10a、10b、10c各自的像素信号混合而成为混合像素信号,在第1垂直信号线vl1b中,第2列像素10d、10f各自的像素信号混合而成为混合像素信号。同样地,在第1垂直信号线vl1c中,第3列像素10g、10h、10i各自的像素信号混合而成为混合像素信号。

[0106]

另外,由于开关swa及开关swb均为导通状态,因此第1垂直信号线vl1a、第1垂直信号线vl1b、第1垂直信号线vl1c相互电连接。由此,分别输出至第1垂直信号线vl1a、第1垂直信号线vl1b及第1垂直信号线vl1c的混合像素信号进一步混合。即,第1列像素10a、10b、10c的混合像素信号、第2列像素10d、10f的混合像素信号及第3列像素10g、10h、10i的混合像素信号混合。其结果为,在运算部50b的第1及第3及第5输入端子ia、ic、ie输入8个像素10a~10d、10f~10i的混合像素信号,在运算部50b的第4输入端子id输入中央位置的像素10e的像素信号。

[0107]

运算部50b输出将以上除了中央位置以外的8个像素的混合像素信号与中央位置的像素10e的像素信号相加平均得到的加算像素信号。由此,在将3像素

×

3像素的各像素信号混合的情况下,能够获得对中央位置的像素的像素信号实施了加权的像素信号。

[0108]

图7的(b)是示意性示出第2实施方式的摄像元件3进行像素信号的混合处理的另一例的图。在图7的(b)所示的例子中,水平混合部40具有使第2垂直信号线vl2a与第2垂直

信号线vl2c连接或切断的开关swc。垂直控制部70将水平混合部40的开关swc设为导通状态。垂直控制部70将第2列像素10(像素10d、10e、10f)中的中央位置的像素10e的像素信号读取至第2垂直信号线vl2b,将像素10d及10f各自的像素信号读取至第1垂直信号线vl1b。由此,在第1垂直信号线vl1b中,像素10d的像素信号与像素10f的像素信号混合而成为混合像素信号。

[0109]

垂直控制部70将第1列像素10(像素10a、10b、10c)中的中央位置的像素10b的像素信号读取至第2垂直信号线vl2a,将像素10a及10c各自的像素信号读取至第1垂直信号线vl1a。由此,在第1垂直信号线vl1a中,像素10a的像素信号与像素10c的像素信号混合而成为混合像素信号。同样地,垂直控制部70将第3列像素10(像素10g、10h、10i)中的、中央位置的像素10h的像素信号读取至第2垂直信号线vl2c,将像素10g及10i各自的像素信号读取至第1垂直信号线vl1c。由此,在第1垂直信号线vl1c中,像素10g的像素信号与像素10i的像素信号混合而成为混合像素信号。

[0110]

另外,由于开关swc成为导通状态,因此第2垂直信号线vl2a与第2垂直信号线vl2c相互电连接。在该情况下,垂直控制部70使与第2垂直信号线vl2a连接的第2电流源26a及与第2垂直信号线vl2c连接的第2电流源26c中的某一电流的供给停止。例如,垂直控制部70使第2电流源26c进行的电流供给停止。由此,第2电流源26a的电流经由第2垂直信号线vl2a向像素10b供给,并且,经由第2垂直信号线vl2a、开关swc及第2垂直信号线vl2c向像素10h供给。在第2垂直信号线vl2a及第2垂直信号线vl2c中,像素10b的像素信号与像素10h的像素信号混合而成为混合像素信号。

[0111]

运算部50b输出将像素10a及像素10c的混合像素信号、像素10d及像素10f的混合像素信号、像素10g及像素10i的混合像素信号、像素10b及像素10h的混合像素信号、中央位置的像素10e的像素信号相加平均得到的加算像素信号。由此,在将3像素

×

3像素各自的像素信号混合的情况下,能够获得对中央位置的像素的像素信号实施了加权的像素信号。

[0112]

图8是用于说明第2实施方式的摄像元件3的电路构成及动作例的图。参照图8,进一步详细说明图7的(a)的摄像元件3进行的像素信号的混合处理。像素10(2,2)为作为混合对象的9个像素10中的中央位置的像素,与图7的(a)、(b)中的像素10e对应。此外,各像素10的电路构成与第1实施方式的情况相同。

[0113]

水平混合部40具有开关sw41、sw42、sw43、sw44、sw45、sw46。开关sw41使第1垂直信号线vl1a与第1垂直信号线vl1b连接或切断,开关sw42使第1垂直信号线vl1b与第1垂直信号线vl1c连接或切断。开关sw43使第2垂直信号线vl2a与第2垂直信号线vl2b连接或切断,开关sw44使第2垂直信号线vl2b与第2垂直信号线vl2c连接或切断。开关sw45使第1垂直信号线vl1a与第1垂直信号线vl1c连接或切断,开关sw46使第2垂直信号线vl2a与第2垂直信号线vl2c连接或切断。开关sw41、sw42分别是图7的(a)中的开关swa、swb,开关sw46是图7的(b)中的开关swc。

[0114]

运算部50b具有第1输入部ia~第6输入部if、电容51~57、开关sw51~sw59及开关sw61~sw66。电容51的一个端子经由开关sw61与第1垂直信号线vl1a连接,另一端子与放大器60的输入端子62连接。电容52的一个端子经由开关sw62与第2垂直信号线vl2a连接,另一端子与输入端子62连接。电容53的一个端子经由开关sw63与第1垂直信号线vl1b与连接,另一端子与输入端子62连接,电容54的一个端子经由开关sw64与第2垂直信号线vl2b连接,另

一端子与输入端子62连接。电容55的一个端子经由开关sw65与第1垂直信号线vl1c连接,另一端子与输入端子62连接,电容56的一个端子经由开关sw66与第2垂直信号线vl2c连接,另一端子与输入端子62连接。另外,电容57的一个端子与放大器60的输入端子62连接,另一端子与放大器60的输出端子63连接。电容53具有电容值c,电容51~56分别具有电容值c的1/6的电容值即1/6c的电容值。此外,也可以由电容值能够变更的可变电容构成电容51~57。

[0115]

开关sw51使电容51的一个端子与电容53的一个端子连接或切断,开关sw52使电容53的一个端子与电容55的一个端子连接或切断。开关sw53使电容52的一个端子与电容54的一个端子连接或切断,开关sw54使电容54的一个端子与电容56的一个端子连接或切断。另外,开关sw55使电容51的一个端子与电容55的一个端子连接或切断,开关sw56使电容52的一个端子与电容56的一个端子连接或切断。此外,开关sw57使电容51的一个端子与电容52的一个端子连接或切断,开关sw58使电容53的一个端子与电容54的一个端子连接或切断。开关sw59使电容55的一个端子与电容56的一个端子连接或切断。

[0116]

运算部50b从输出端子63输出对分别输入至电容51~电容56的信号进行加法运算得到的信号。从运算部50b输出的信号在通过ad转换部80及输出部90等实施了信号处理后,向相机1的控制部4输出。以下进一步详细说明第2控制模式的情况下的像素信号读取方法。

[0117]

垂直混合控制部71(参照图6)将中央位置周围的像素10(1,1)、(2,1)、(3,1)、(1,2)、(3,2)、(1,3)、(2,3)、(3,3)的第1选择部16均设为导通状态,将第2选择部17均设为截止状态。另外,垂直混合控制部71将中央位置的像素即像素10(2,2)的第1选择部16设为截止状态,将像素10(2,2)的第2选择部17设为导通状态。水平混合控制部72(参照图6)将水平混合部40的开关sw41及开关sw42均设为导通状态,将开关sw43~sw46均设为截止状态。加法运算控制部73(参照图6)将运算部50b的开关sw53及开关sw54均设为导通状态,将开关sw51~sw52及开关sw55~sw59均设为截止状态。另外,加法运算控制部73将运算部50b的开关sw61、sw63、sw64、sw65均设为导通状态,将开关sw62及sw66均设为截止状态。此外,垂直控制部70使第2电流源26a的电流供给和第2电流源26c的电流供给停止。

[0118]

第1列像素10(1,1)、像素10(2,1)及像素10(3,1)各自的第1选择部16成为导通状态,从而以上三个像素10各自的增幅部15的源极端子与第1垂直信号线vl1a电连接。与第1垂直信号线vl1a连接的第1电流源25a的电流被向像素10(1,1)、像素10(2,1)和像素10(3,1)分流。在第1垂直信号线vl1a中,像素10(1,1)、像素10(2,1)及像素10(3,1)各自的像素信号混合而成为混合像素信号。

[0119]

第2列像素10(1,2)及像素10(3,2)各自的第1选择部16成为导通状态,从而这两个像素10各自的增幅部15的源极端子与第1垂直信号线vl1b电连接。与第1垂直信号线vl1b连接的第1电流源25b的电流被向像素10(1,2)和像素10(3,2)分流。在第1垂直信号线vl1b中,像素10(1,2)及像素10(3,2)各自的像素信号混合而成为混合像素信号。

[0120]

第3列像素10(1,3)、像素10(2,3)及像素10(3,3)各自的第1选择部16成为导通状态,从而这三个像素10各自的增幅部15的源极端子与第1垂直信号线vl1c电连接。与第1垂直信号线vl1c连接的第1电流源25c的电流被向像素10(1,3)、像素10(2,3)和像素10(3,3)分流。在第1垂直信号线vl1c中,像素10(1,3)、像素10(2,3)及像素10(3,3)各自的像素信号混合而成为混合像素信号。

[0121]

另外,开关sw41及开关sw42均为导通状态,从而第1垂直信号线vl1a、第1垂直信号

线vl1b与第1垂直信号线vl1c相互电连接。由此,分别输出至第1垂直信号线vl1a、第1垂直信号线vl1b及第1垂直信号线vl1c的像素信号混合。即,第1列像素10(1,1)、(2,1)、(3,1)的混合像素信号、第2列像素10(1,2)、(3,2)的混合像素信号、第3列像素10(1,3)、(2,3)、(3,3)的混合像素信号混合。其结果为,向第1垂直信号线vl1a、vl1b、vl1c输出中央位置周围的像素10(1,1)、(2,1)、(3,1)、(1,2)、(3,2)、(1,3)、(2,3)、(3,3)这8个像素的像素信号混合而成的混合像素信号。

[0122]

中央位置的像素10(2,2)的第2选择部17成为导通状态,从而像素10(2,2)的增幅部15与第2垂直信号线vl2b电连接。与第2垂直信号线vl2b连接的第2电流源26b的电流全部流向像素10(2,2)。向第2垂直信号线vl2b输出像素10(2,2)的像素信号。

[0123]

另外,开关sw53及开关sw54均为导通状态,从而向第2垂直信号线vl2b输出的像素10(2,2)的像素信号被输入至电容52、电容54和电容56。8个像素的混合像素信号被输入至电容51、电容53和电容55。由此,运算部50b从放大器60的输出端子63输出将中央位置的像素即像素10(2,2)的像素信号与除了中央位置以外的上述8个像素混合像素信号相加平均得到的加算像素信号。由此,在本实施方式中,在将列方向及行方向的多个像素10的信号混合的情况下,能够获得对中央位置的像素10的像素信号实施了加权的像素信号。

[0124]

图9是用于说明第2实施方式的摄像元件3的电路构成及其他动作例的图。参照图9,进一步详细说明图7的(b)的摄像元件3进行的像素信号混合处理。

[0125]

垂直混合控制部71将第1列像素中的中央像素10(2,1)的第1选择部16设为截止状态,将第2选择部17设为导通状态。另外,垂直混合控制部71将像素10(2,1)的上下的像素即像素10(1,1)、(3,1)的第1选择部16均设为导通状态,将第2选择部17均设为截止状态。

[0126]

垂直混合控制部71将第2列像素中的中央像素10(2,2)的第1选择部16设为截止状态,将第2选择部17设为导通状态。另外,垂直混合控制部71将像素10(1,2)、(3,2)的第1选择部16均设为导通状态,将第2选择部17均设为截止状态。同样地,垂直混合控制部71将第3列像素中的中央位置的像素10(2,3)的第1选择部16设为截止状态,将第2选择部17设为导通状态。另外,垂直混合控制部71将像素10(1,3)、(3,3)的第1选择部16均设为导通状态,将第2选择部17均设为截止状态。

[0127]

水平混合控制部72将水平混合部40的开关sw46设为导通状态,将开关sw41~sw45均设为截止状态。加法运算控制部73将运算部50b的开关sw54、sw56设为导通状态,将开关sw51~sw53、开关sw55及开关sw57~sw59均设为截止状态。另外,加法运算控制部73将运算部50b的开关sw61~sw65设为导通状态,将开关sw66设为截止状态。此外,垂直控制部70使第2电流源26c的电流供给停止。

[0128]

第1列像素10(1,1)及像素10(3,1)各自的第1选择部16成为导通状态,从而在第1垂直信号线vl1a中,像素10(1,1)及像素10(3,1)各自的像素信号混合而成为混合像素信号。另外,第2列像素10(1,2)及像素10(3,2)各自的第1选择部16成为导通状态,从而在第1垂直信号线vl1b中,像素10(1,2)及像素10(3,2)各自的像素信号混合而成为混合像素信号。同样地,第3列像素10(1,3)及像素10(3,3)各自的第1选择部16为导通状态,从而在第1垂直信号线vl1c中,像素10(1,3)及像素10(3,3)各自的像素信号混合而成为混合像素信号。

[0129]

另外,第1列像素10(2,1)的第2选择部17、第3列像素10(2,3)的第2选择部17、开关

sw46为导通状态,从而像素10(2,1)及像素10(2,3)各自的增幅部15的源极端子电连接。与第2垂直信号线vl2a连接的第2电流源26a的电流被分流至像素10(2,1)和像素10(2,3)。向第2垂直信号线vl2a及第2垂直信号线vl2c输出像素10(2,1)、(2,3)这两个像素的像素信号混合而成的混合像素信号。

[0130]

中央位置的像素10(2,2)的第2选择部17为导通状态,从而像素10(2,2)的增幅部15与第2垂直信号线vl2b电连接。第2电流源26b的电流全部流向像素10(2,2)。然后,向第2垂直信号线vl2b输出像素10(2,2)的像素信号。

[0131]

另外,开关sw54为导通状态,从而输出至第2垂直信号线vl2b的像素10(2,2)的像素信号被输入至电容54及电容56。输出至第1垂直信号线vl1a的像素10(1,1)及像素10(3,1)的混合像素信号被输入至电容51。向第2垂直信号线vl2a及第2垂直信号线vl2c输出的像素10(2,1)及像素10(2,3)的混合像素信号被输入至电容52。另外,输出至第1垂直信号线vl1b的像素10(1,2)及像素10(3,2)的混合像素信号被输入至电容53,输出至第1垂直信号线vl1c的像素10(1,3)及像素10(3,3)的混合像素信号被输入至电容55。

[0132]

运算部50b对中央位置的像素即像素10(2,2)的像素信号、像素10(1,1)、(3,1)的混合像素信号、像素10(2,1)、(2,3)的混合像素信号、像素10(1,2)、(3,2)的混合像素信号、像素10(1,3)、(3,3)的混合像素信号进行加法运算。运算部50b将所生成的加算像素信号从放大器60的输出端子63输出。由此,在本实施方式中,在将列方向及行方向的多个像素10的信号混合的情况下,能够获得对中央位置的像素10的像素信号实施了加权的像素信号。

[0133]

根据上述实施方式,在与第1实施方式相同的作用效果的基础上,还能够获得以下作用效果。

[0134]

(3)像素10在作为第1方向的列方向及作为第2方向的行方向上配置有多个。多个像素10包含配置在第1列的第1、第2及第3像素和配置在第2列的第1、第2及第3像素,第1及第2信号线(第1及第2垂直信号线vl1、vl2)分别针对第1及第2列设置。运算部50进行向与第1列对应的第1及第2信号线输出的信号和向与第2列对应的第1及第2信号线输出的信号的运算。由于采用这种方式,因此能够将列方向及行方向的多个像素10的信号混合。另外,在对多个像素信号进行混合的情况下,无论像素位置如何,均能够防止对fd的电位高的像素的像素信号实施加权。

[0135]

以下变形也在本发明的范围内,也可以将一个或多个变形例与上述实施方式组合。

[0136]

(变形例1)

[0137]

在上述实施方式中,对一个像素配置一个光电转换部的例子进行了说明,但像素的构成不限于此。也可以使像素的构成为一个像素具有两个以上的光电转换部。在该情况下,摄像元件3在设定了第1控制模式的情况下,将来自多个光电转换部中的两个以上光电转换部的信号相加,从全部像素10独立读取像素信号。摄像元件3在设定了第2控制模式的情况下,将例如列方向的多个像素10的信号混合并读取。

[0138]

图10是示出变形例1的摄像元件3的一部分构成的电路图。像素10具有第1光电转换部11a、第2光电转换部11b、第1传输部12a、第2传输部12b、第1复位部13a、第2复位部13b、第一fd14a和第二fd14b。像素10还具有第1增幅部15a、第2增幅部15b、第1选择部16、第2选择部17、加法运算开关部18和耦合开关部19。

[0139]

第1传输部12a由晶体管m1a构成,将由第1光电转换部11a光电转换得到的电荷向第一fd14a传输。第一fd14a对传输至第一fd14a的电荷进行蓄积。第1增幅部15a由晶体管m3a构成,对由蓄积在第一fd14a中的电荷生成的信号进行增幅并输出。第1复位部13a由晶体管m2a构成,使第一fd14a的电压复位。第1选择部16由晶体管由构成,将来自第1增幅部15a的信号向第1垂直信号线vl1输出。

[0140]

第2传输部12b由晶体管m1b构成,将由第2光电转换部11b光电转换得到的电荷向第二fd14b传输。第二fd14b对传输至第二fd14b的电荷进行蓄积。第2增幅部15b由晶体管m3b构成,对由蓄积在第二fd14b中的电荷生成的信号进行增幅并输出。第2复位部13b由晶体管m2b构成,使第二fd14b的电压复位。第2选择部17由晶体管构成,将来自第2增幅部15b的信号输出至第2垂直信号线vl2。

[0141]

加法运算开关部18由晶体管m8构成,使第一fd14a与第二fd14b连接(结合)。加法运算开关部18是加法部18,使第一fd14a与第二fd14b连接,将分别由第1光电转换部及第2光电转换部11a、11b进行光电转换得到的电荷相加。耦合开关部19由晶体管构成,使第1增幅部15a与第2增幅部15b连接。更详细来说,耦合开关部19使第1增幅部15a的晶体管m3a的源极与第2增幅部15b的晶体管m3b的源极连接。另外,可以说耦合开关部19使第1增幅部15a与第1选择部16之间、使第2增幅部15b与第2选择部17之间连接。

[0142]

在第1控制模式下,垂直控制部70将第1行像素10(1,1)的加法运算开关部18设为导通状态,将耦合开关部19也设为导通状态。另外,垂直控制部70例如将第1选择部16设为导通状态,将第2选择部17设为截止状态。分别由第1光电转换部及第2光电转换部11a、11b进行光电转换得到的电荷分别通过第1及第2传输部12a、12b传输并进行加法运算,且蓄积在第1及第二fd14a、14b中。通过第1及第2增幅部15a、15b、耦合开关部19和第1选择部16,生成与加法运算得到的电荷对应的像素信号,并读取至第1垂直信号线vl1。输出至第1垂直信号线vl1的像素信号如上所述,通过运算部50进行加法运算。

[0143]

若从第1行像素10将像素信号读取至第1垂直信号线vl1,则之后在摄像元件3中,以行单位依次选择第2行、第3行的像素10,进行从像素10向第1垂直信号线vl1的像素信号的读取。此外,在第1控制模式下,在将第1选择部16设为截止状态、将第2选择部17设为导通状态的情况下,像素信号被读取至第2垂直信号线vl2。

[0144]

此外,针对两行像素,也可以将一行像素的像素信号读取至第1垂直信号线vl1,与此同时将另一行像素的像素信号读取至第2垂直信号线vl2。在该情况下,通过针对每个像素列设置两个运算部50,从而能够同时对来自两行像素的像素信号进行信号处理,并向控制部4输出。垂直控制部70将像素10(1,1)的第1选择部16设为导通状态,将像素10(1,1)的第2选择部17设为截止状态,将像素10(2,1)的第1选择部16设为截止状态,将像素10(1,1)的第2选择部17为导通状态。由此,向第1垂直信号线vl1读取像素10(1,1)的像素信号,向第2垂直信号线vl2读取像素10(2,1)的像素信号。按照这种方式,能够同时进行两行像素的像素信号读取。

[0145]

在第2控制模式下,垂直控制部70将第1行~第3行像素10(1,1)、(2,1)、(3,1)的加法运算开关部18及耦合开关部19均设为导通状态。另外,垂直控制部70将第1行及第3行像素10(1,1)、(3,1)的第1选择部16设为导通状态,将第2选择部17设为截止状态。此外,垂直控制部70将第2行像素10(2,1)的第1选择部16设为截止状态,将第2选择部17设为导通状

态。由此,在第1垂直信号线vl1中,来自像素10(1,1)的像素信号及来自像素10(3,1)的像素信号混合而成为混合像素信号。另外,向第2垂直信号线vl2读取中央位置的像素10(2,1)的像素信号。像素10(1,1)及像素10(3,1)的混合像素信号和像素10(2,1)的像素信号与上述实施方式的情况同样地,通过运算部50进行加法运算。

[0146]

垂直控制部70在读取来自第1行~第3行像素10的加算像素信号之后,进行来自第4行~第6行的像素10的加算像素信号的读取。此外,在第2控制模式下,也可以将像素10(1,1)的像素信号与像素10(3,1)的像素信号读取至第2垂直信号线vl2并混合,将中央位置的像素10(2,1)的像素信号读取至第1垂直信号线vl1。

[0147]

此外,在图10所示的像素构成的情况下,控制部4还能够进行独立读取来自各像素的多个光电转换部的信号的处理(第3控制模式)。在该情况下,垂直控制部70将加法运算开关部18的晶体管m8设为截止状态,将耦合开关部19的晶体管也设为截止状态。由第1光电转换部11a进行光电转换得到的电荷通过第1传输部12a被传输至第一fd14a。然后,与传输至第一fd14a的电荷对应的像素信号通过第1增幅部15a及第1选择部16被读取至第1垂直信号线vl1。另外,由第2光电转换部11b进行光电转换得到的电荷通过第2传输部12b被传输至第二fd14b。与传输至第二fd14b的电荷对应的像素信号通过第2增幅部15b及第2选择部17被读取至第2垂直信号线vl2。

[0148]

(变形例2)

[0149]

在上述实施方式中,对作为光电转换部使用光电二极管的例子进行了说明。但作为光电转换部也可以使用光电转换膜。

[0150]

(变形例3)

[0151]

在上述实施方式及变形例中说明的摄像元件及摄像装置也可以应用于相机、智能手机、平板电脑、内置于pc的相机、车载相机、在无人航空机(无人机、无线电控制机等)上搭载的相机等。

[0152]

(变形例4)

[0153]

也可以将上述实施方式及变形例中说明的摄像元件应用于将多个基板(例如多个半导体基板)层叠构成的层叠传感器(层叠型摄像元件)。例如,多个像素10配置于第1层基板,电流源25、26、水平混合部40、运算部50和ad转换部80配置于第2层基板,多个垂直信号线vl配置在第1层基板与第2层基板之间。也可以是,多个像素10、电流源25、26和水平混合部40配置于第1层基板,运算部50和ad转换部80配置于第2层基板。另外,层叠传感器也可以设为3层以上。

[0154]

以上对多种实施方式及变形例进行了说明,但本发明不限定于上述内容。在本发明技术思想范围内可想到的其他方式也包含在本发明的范围内。

[0155]

以下优先权基础申请的公开内容作为引用内容引入在本技术中。

[0156]

日本专利申请2017年第63197号(2017年3月28日申请)

[0157]

附图标记说明

[0158]

1摄像装置、3摄像元件、4控制部、10像素、11光电转换部、15增幅部、16第1选择部、17第2选择部、25第1电流源、26第2电流源、50运算部、70垂直控制部。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。