training)程序。于初始化完成后,ddr存储器系统100才能够正常运行。

10.在ddr存储器系统100中,处理电路110与ddr存储器120是固定在电路板(circuit board)上,而存储器总线122的多条布局线路(layout trace)是设计在电路板上。由于布局线路的长度不相同,造成处理电路110发出的时钟信号clk以及第一数据选取信号dqs_t传递的时间不相同。因此,ddr存储器系统100需要进行写入均衡(write leveling)程序使得时钟信号clk与第一数据选取信号dqs_t传递至ddr存储器120时,彼此的信号缘(signal edge)可以对齐(align)。

11.在进行写入均衡(write leveling)程序时,处理电路110发出时钟信号clk以及第一数据选取信号dqs_t至ddr存储器120。接着,处理电路110持续地调整第一数据选取信号dqs_t的延迟时间,亦即调整第一数据选取信号dqs_t与时钟信号clk之间的相位差。当ddr存储器120接收到的时钟信号clk以及第一数据选取信号dqs_t时,会进一步判断时钟信号clk以及第一数据选取信号dqs_t的信号缘是否对齐,并利用数据信号dq回复处理电路110。

12.举例来说,ddr存储器120在第一数据选取信号dqs_t的上升缘(rising edge)取样时钟信号clk,并将取样结果由数据信号dq回复给处理电路110。

13.于写入均衡程序时,当初次取样的结果为低电平,则代表第一数据选取信号dqs_t与时钟信号clk的信号缘未对齐。此时,ddr存储器120产生的低电平的数据信号dq至处理电路110。

14.再者,处理电路110根据低电平的数据信号dq,继续调整第一数据选取信号dqs_t与时钟信号clk之间的相位差,例如增加第一数据选取信号dqs_t的延迟时间,直到ddr存储器120取样的结果为高电平,并产生高电平的数据信号dq至处理电路110为止。当数据信号dq为高电平时,处理电路110即记录当下第一数据选取信号dqs_t与时钟信号clk之间的特定相位差(specific phase difference),并且完成写入均衡(write leveling)程序。

15.另外,当初次取样的结果为高电平时,处理电路110仍无法确认第一数据选取信号dqs_t与时钟信号clk的信号缘是否对齐。

16.此时,处理电路110继续调整第一数据选取信号dqs_t与时钟信号clk之间的相位差,例如减少第一数据选取信号dqs_t的延迟时间,直到ddr存储器120取样的结果为低电平,并产生低电平的数据信号dq至处理电路110为止。

17.接着,处理电路110再增加第一数据选取信号dqs_t的延迟时间,使得ddr存储器120取样的结果为高电平,并产生高电平的数据信号dq至处理电路110。而处理电路110即记录当下第一数据选取信号dqs_t与时钟信号clk之间的特定相位差(specific phase difference),并且完成写入均衡(write leveling)程序。

18.完成写入均衡(write leveling)程序之后,处理电路110会输出具有特定相位差的第一数据选取信号dqs_t与时钟信号clk,此二信号经过存储器总线122上的布局线路后,ddr存储器120即可接收到信号缘彼此对齐的第一数据选取信号dqs_t与时钟信号clk。

19.之后,处理电路110可继续进行写入训练(write training)。在写入训练程序时,处理电路110会调整第一数据选取信号dqs_t、第二数据选取信号dqs_c与数据信号dq的相位关系,并且找到一特定区间(specific margin),用以确保ddr存储器120在特定区间的内皆可成功地利用第一数据选取信号dqs_t与第二数据选取信号dqs_c来锁存(latch)数据信号dq。

20.然而,在现有ddr存储器系统100中,当写入均衡(write leveling)程序完成后,处理电路110仅能够确定ddr存储器120接收到信号缘彼此对齐的第一数据选取信号dqs_t与时钟信号clk,并无法确认是否是正确的信号缘。

21.举例来说,存储器总线122中,当时钟信号clk的布线长于第一数据选取信号dqs_t的布线时,时钟信号clk的传递延迟(propagation delay)较长。因此,当写入均衡(write leveling)程序完成后,时钟信号clk的脉冲可能会慢第一数据选取信号dqs_t的脉冲(pulse)一个时钟周期(clock cycle)到达ddr存储器120。虽然第一数据选取信号dqs_t与时钟信号clk的信号缘互相对齐,但是在后续的运行中ddr存储器120将无法由数据信号dq上正确地获得处理电路110发出的数据。

22.同理,存储器总线122中,第一数据选取信号dqs_t的布线的布线长于时钟信号clk时,第一数据选取信号dqs_t的传递延迟(propagation delay)较长。因此,当写入均衡(write leveling)程序完成后,第一数据选取信号dqs_t的脉冲可能会慢时钟信号clk的一个时钟周期(clock cycle)到达ddr存储器120。虽然第一数据选取信号dqs_t与时钟信号clk的信号缘互相对齐,但是在后续的运行中ddr存储器120也无法由数据信号dq上正确地获得处理电路110发出的数据。

技术实现要素:

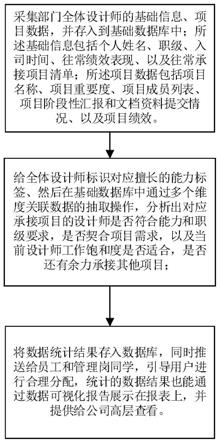

23.本发明提出一种多循环写入均衡程序的处理方法运用于一存储器系统,该处理方法下列步骤:(a)将一写入数据写入一双倍数据率存储器,并读取该写入数据;(b)判断写入的该写入数据与读取的该写入数据是否数据匹配,其中于数据不匹配时,判断一数据信号的一第一延迟时间是否已经调整至一第一上限;(c)当该第一延迟时间未调整至该第一上限时,增加该数据信号的该第一延迟时间后回到步骤(a);(d)当该第一延迟时间调整至该第一上限时,判断一第一数据选取信号的一第二延迟时间是否已经调整至一第二上限;(e)当该第二延迟时间未调整至该第二上限时,增加该第一数据选取信号的该第二延迟时间后回到步骤(a);(f)当该第二延迟时间调整至该第二上限时,判断一位址/指令信号的一第三延迟时间是否已经调整至一第三上限;以及(g)当该第三延迟时间未调整至该第三上限时,增加该位址/指令信号的该第三延迟时间后回到步骤(a)。

附图说明

24.为了对本发明的上述及其他方面有更佳的了解,下文特举优选实施例,并配合附图,作详细说明如下:

25.图1为现有ddr存储器系统示意图。

26.图2为现有ddr存储器的示意图。

27.图3为本发明ddr存储器系统示意图。

28.图4a至图4c为第一数据选取信号dqs_t与时钟信号clk的信号缘对齐的各种情况。

29.图5为本发明的控制电路。

30.图6a与图6b为本发明多循环写入均衡程序的处理方法。

31.图7为位址/指令信号ca/cmd延迟控制中的处理流程。

32.其中,附图标记说明如下:

33.100,300:ddr存储器系统

34.110,310:处理电路

35.120:ddr存储器

36.122:存储器总线

37.132,134:比较器

38.136:延迟电路

39.138:解串器

40.312:存储器控制器

41.314:实体层电路

42.316:存储器与实体层接口

43.510:时钟路径电路

44.512,522,532,542:整数周期延迟器

45.514,524,534,544:串化器

46.516,526,536,546:输出输入电路

47.518,548:延迟线电路

48.520:位址/指令路径电路

49.530:数据选取路径电路

50.540:数据路径电路

51.s602~s656,s702~s706:步骤流程

具体实施方式

52.请参照图3,其所示出为本发明ddr存储器系统示意图。ddr存储器系统300包括一处理电路310与一ddr存储器120。

53.处理电路310中包括一存储器控制器(memory controller)312与实体层电路(phy circuit)314。其中,实体层电路314与ddr存储器120之间利用存储器总线122来传递各种信号。再者,存储器控制器312与实体层电路314之间的接口为存储器与实体层接口316(ddr phy interface,简称dfi接口)。其中,存储器总线122上的信号至少包括:时钟信号clk、位址信号ca、指令信号cmd、数据信号dq、第一数据选取信号dqs_t与第二数据选取信号dqs_c,且第一数据选取信号dqs_t与第二数据选取信号dqs_c的相位相差180度。其中,位址信号ca与指令信号cmd是参考时钟信号clk来运行,数据信号dq是参考第一数据选取信号dqs_t与第二数据选取信号dqs_c来运行。再者,指令信号cmd包括:指令始能信号cs、行位址选取信号cas、列位址选取信号ras、写入使能信号we。

54.在ddr存储器系统300中,由于布局线路的长度不相同,造成处理电路310发出的时钟信号clk以及第一数据选取信号dqs_t传递的时间不相同。因此,ddr存储器系统300需要进行写入均衡(write leveling)程序使得时钟信号clk与第一数据选取信号dqs_t传递至ddr存储器120时,彼此的信号缘(signal edge)可以对齐(align)。

55.于完成写入均衡(write leveling)程序之后,处理电路310会输出具有特定相位差的第一数据选取信号dqs_t与时钟信号clk,此二信号经过存储器总线122上的布局线路后,ddr存储器120即可接收到信号缘彼此对齐的第一数据选取信号dqs_t与时钟信号clk。

然而,处理电路310仅能够确定ddr存储器120接收到信号缘彼此对齐的第一数据选取信号dqs_t与时钟信号clk,并无法确认是否是正确的信号缘。

56.请参照图4a至图4c,其所示出为第一数据选取信号dqs_t与时钟信号clk的信号缘对齐的各种情况。于完成写入均衡(write leveling)程序之后,处理电路310输出的时钟信号clk的上升缘a以及第一数据选取信号dqs_t的上升缘b之间具特定相位差。

57.如图4a所示,在理想状况下,时钟信号clk以及第一数据选取信号dqs_t经过存储器总线122上的布局线路后,ddr存储器120接收到二信号缘a、b彼此对齐的第一数据选取信号dqs_t与时钟信号clk。

58.然而,存储器总线122中,当时钟信号clk的布线长于第一数据选取信号dqs_t的布线时,时钟信号clk的传递延迟(propagation delay)较长。如图4b所示,第一数据选取信号dqs_t的信号缘b先传递至ddr存储器120,经过一个时钟周期(clock cycle)后,时钟信号clk的信号缘a才传递至ddr存储器120。于更糟的情况下,第一数据选取信号dqs_t的信号缘b与时钟信号clk的信号缘a可能相差超过一个以上的时钟周期。

59.再者,存储器总线122中,当第一数据选取信号dqs_t的布线长于时钟信号clk的布线时,第一数据选取信号dqs_t的传递延迟(propagation delay)较长。如图4c所示,时钟信号clk的信号缘a先传递至ddr存储器120,经过一个时钟周期(clock cycle)后,第一数据选取信号dqs_t的信号缘b才传递至ddr存储器120。于更糟的情况下,时钟信号clk的信号缘a与第一数据选取信号dqs_t的信号缘b可能相差超过一个以上的时钟周期。

60.由以上的说明可知,在图4b与图4c的情况下,虽然第一数据选取信号dqs_t与时钟信号clk的信号缘互相对齐,但是在后续的运行中ddr存储器120无法由数据信号dq上正确地获得处理电路310发出的数据。

61.为了解决上述问题,本发明在处理电路310的实体层电路314内部设计了控制电路,并进行多循环写入均衡(multi-cycle write leveling)程序,以确保ddr存储器120接收到的时钟信号clk与第一数据选取信号dqs_t为彼此对齐且正确的信号缘。

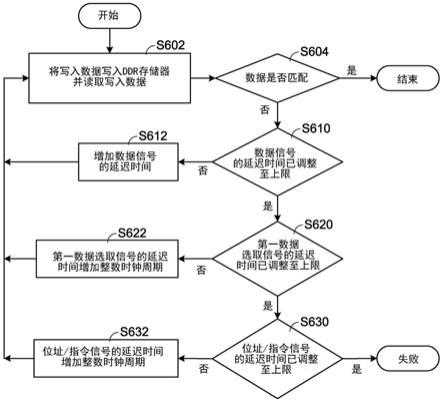

62.请参照图5,其所示出为本发明的控制电路。控制电路设计在实体层电路314内部用以调整时钟信号clk、位址信号ca、指令信号cmd、数据信号dq、第一数据选取信号dqs_t、第二数据选取信号dqs_c的延迟时间。控制电路包括:时钟路径电路(clock path circuit)510、位址/指令路径电路(address/command path circuit)520、数据选取路径电路(dqs path circuit)530与数据路径电路(data path circuit)540。

63.以数据路径电路540为例来说明。数据路径电路540包括整数周期延迟器(cycle based delay circuit)542、延迟线电路(delay line circuit)548、串化器(serializer)544以及输出入电路(i/o电路)546。

64.整数周期延迟器542接收内部时钟信号clkin,并且整数周期延迟器542经由存储器与实体层接口316接收存储器控制器312输出的偶数部分数据(even portion of data)even

dq

与奇数部分数据(odd portion of data)odd

dq

。根据本发明的实施例,整数周期延迟器542可以选择性地将偶数部分数据even

dq

与奇数部分数据odd

dq

延迟0至4个时钟周期,并且产生延迟的偶数部分数据(delayed even portion of data)ed

dq

与延迟的奇数部分数据(delayed odd portion of data)od

dq

。再者,延迟线电路548接收内部时钟信号clkin,并可选择性地将内部时钟信号clkin延迟分数个时钟周期,并且产生延迟的内部时钟信号

clkdin。举例来说,延迟线电路548可将内部时钟信号clkin延迟n/8个时钟周期,其中n为0至7的整数。

65.串化器(serializer)544接收延迟的内部时钟信号clkdin。并且,串化器(serializer)544根据延迟的内部时钟信号clkdin来取样(sample)延迟的偶数部分数据ed

dq

与延迟的奇数部分数据od

dq

,并且产生数据信号dq。再者,输出入电路546接收并输出数据信号dq。

66.由以上的说明可知,在数据路径电路540中,可以选择性地控制数据信号dq的延迟时间,且延迟时间可控制在0个时钟周期至(4 7/8)时钟周期之间。

67.时钟路径电路510包括整数周期延迟器512、串化器514与输出入电路516与延迟线电路518。时钟与指令路径电路520接收偶数部分时钟(even portion of clock)even

clk

与奇数部分时钟(odd portion of clock)odd

clk

,并产生时钟信号clk。其中,时钟信号clk与内部时钟信号clkin有相同的频率。再者,时钟路径电路510的结构与运行关系类似于数据路径电路540,此处不再赘述。

68.位址/指令路径电路520包括整数周期延迟器522、串化器524与输出入电路526。位址/指令路径电路520接收偶数部分位址/指令(even portion of address/command)even

ca/cmd

与奇数部分位址/指令(odd portion of address/command)odd

ca/cmd

,并产生位址/指令信号ca/cmd。再者,位址/指令路径电路520的结构与运行关系类似于数据路径电路540,此处不再赘述。由于本发明仅对位址/指令路径电路520进行整数时钟周期的延迟,所以没有示出延迟线电路。在此领域的技术人员也可以在位址/指令路径电路520中增加延迟线电路。

69.另外,数据选取路径电路530包括整数周期延迟器532、串化器534与输出入电路536。数据选取路径电路530接收偶数部分数据选取(even portion of dqs)even

dqs

与奇数部分数据选取(odd portion of dqs)odddqs,并产生第一数据选取信号dqs_t。当然,第二数据选取信号dqs_c也可以利用类似的电路来产生。再者,数据选取路径电路530的结构与运行关系类似于数据路径电路540,此处不再赘述。由于本发明仅对数据选取路径电路530进行整数时钟周期的延迟,所以没有示出延迟线电路。在此领域的技术人员也可以在数据选取路径电路530中增加延迟线电路。

70.根据本发明的实施例,利用实体层电路314中的控制电路搭配本发明的多循环写入均衡(multi-cycle write leveling)程序的处理方法,可以确认时钟信号clk与第一数据选取信号dqs_t为彼此对齐且正确的信号缘。其中,实体层电路314中的控制电路可调整时钟信号clk、位址信号ca、指令信号cmd、数据信号dq、第一数据选取信号dqs_t、第二数据选取信号dqs_c的延迟时间。

71.请参照图6a与图6b,其所示出为本发明多循环写入均衡程序的处理方法。基本上,当存储器系统300完成写入均衡(write leveling)程序后即可开始进行多循环写入均衡(multi-cycle write leveling)程序。

72.首先,处理电路310先后发出写入指令以及读取指令,用以将写入数据存储至ddr存储器120,并且再由ddr存储器120读取刚刚存储的写入数据(步骤s602)。接着,处理电路310判断数据是否匹配(s604)。

73.根据本发明的实施例,存储器系统300是以正常的运行速度来发出写入指令以及

读取指令。另外,当ddr存储器120回传的写入数据相同于处理电路310输出的写入数据时,代表数据匹配。反之,当ddr存储器120回传的写入数据不同于处理电路310输出的写入数据时,代表数据不匹配。

74.当处理电路310确认数据匹配时,即完成多循环写入均衡程序。反之,当确认数据不匹配时,处理电路310先进行数据信号dq延迟控制。于进行数据信号dq延迟控制时,处理电路310先判断数据信号dq的延迟时间是否已经调整至上限(步骤s610)。当数据信号dq的延迟时间尚未调整至上限时,则增加数据信号dq的延迟时间(步骤s612)后,回到步骤s602。反之,当数据信号dq的延迟时间已经调整至上限时,则进行第一数据选取信号dqs_t延迟控制。

75.举例来说,在数据路径电路540中,数据信号dq的延迟时间可控制在0个时钟周期至(4 7/8)个时钟周期之间。因此,搭配整数周期延迟器542与延迟线电路548,可以控制数据信号dq的延迟时间由小至大,每次增加1/8个时钟周期,直到延迟时间的上限(4 7/8)个时钟周期为止。

76.再者,于进行第一数据选取信号dqs_t延迟控制之前,处理电路310先将数据信号dq的延迟时间回复至最小延迟时间。接着,处理电路310判断第一数据选取信号dqs_t的延迟时间是否已经调整至上限(步骤s620)。当第一数据选取信号dqs_t的延迟时间尚未调整至上限时,则将第一数据选取信号dqs_t的延迟时间增加整数时钟周期(步骤s622)后,回到步骤s602。反之,当第一数据选取信号dqs_t的延迟时间已经调整至上限时,则进行位址/指令信号ca/cmd延迟控制。

77.举例来说,在数据选取路径电路530中,第一数据选取信号dqs_t的延迟时间可控制在0个时钟周期至4个时钟周期之间。因此,整数周期延迟器532可以控制第一数据选取信号dqs_t的延迟时间由小至大,每次增加1个时钟周期,直到延迟时间的上限4个时钟周期为止。

78.再者,于进行位址/指令信号ca/cmd延迟控制之前,处理电路310先将数据信号dq的延迟时间与第一数据选取信号dqs_t的延迟时间回复至最小延迟时间。接着,处理电路310判断位址/指令信号ca/cmd的延迟时间是否已经调整至上限(步骤s630)。当位址/指令信号ca/cmd的延迟时间尚未调整至上限时,则将位址/指令信号ca/cmd的延迟时间增加整数时钟周期(步骤s632)后,回到步骤s602。反之,当位址/指令信号ca/cmd的延迟时间已经调整至上限时,则代表多循环写入均衡程序失败。

79.由于位址/指令信号ca/cmd是参考时钟信号clk运行。换言的,将位址/指令信号ca/cmd延后一个时钟周期可视为调整时钟信号clk一个时钟周期。另外,在位址/指令路径电路520中,位址/指令信号ca/cmd的延迟时间可控制在0个时钟周期至4个时钟周期之间。因此,整数周期延迟器522可以控制位址/指令信号ca/cmd的延迟时间由小至大,每次增加1个时钟周期,直到延迟时间的上限4个时钟周期为止。

80.根据本发明的实施例,当处理电路310确认数据匹配后,处理电路310会记录当下数据信号dq、位址/指令信号ca/cmd、第一数据选取信号dqs_t与第二数据选取信号dqs_c的延迟时间。之后,处理电路310即可继续进行写入训练(write training)程序。如此,即可确定进行写入训练程序时,ddr存储器120可根据第一数据选取信号dqs_t与第二数据选取信号dqs_c由数据信号dq上正确地获得处理电路110发出的数据。

81.另外,如图6b所示,在数据信号dq延迟控制中的延迟数据信号dq(步骤s612)中,对数据路径电路540的详细控制步骤还包括:利用延迟线电路548将数据信号dq的延迟时间增加一个分数时钟周期(步骤s652)。例如,一个分数时钟周期为1/8个时钟周期。接着,判断延迟线电路548是否将延迟时间增加一个时钟周期(步骤s654)。于确认延迟时间增加一个时钟周期时,延迟线电路548停止将延迟时间增加一个时钟周期,并利用周期延迟器542将延迟时间增加一个时钟周期。亦即,延迟线电路548会被重置,使得其控制的延迟时间归0。

82.由以上的说明可知,在数据路径电路540中,搭配整数周期延迟器542与延迟线电路548,即可以控制数据信号dq的延迟时间由小至大,每次增加1/8个时钟周期,直到延迟时间的上限(4 7/8)个时钟周期为止。

83.另外,由于位址/指令信号ca/cmd中的一个渠道(channel)中可能包含了二条位元组通道(byte lanes),例如第0位元组通道(byte-0lane)与第1位元组通道(byte-1lane)。于进行完多循环写入均衡(multi-cycle write leveling)程序之后,可能发生二条位元组通道的延迟时间不同的状况。此时,需要再进一步的调整存储器系统中各个信号的延迟时间。

84.请参照图7,其所示出为位址/指令信号ca/cmd延迟控制中的处理流程。首先,判断指令/位址信号ca/cmd中两个位元组通道之间的延迟时间差异(步骤s702)。接着,将延迟时间较短的位元组通道的延迟时间再增加该延迟时间差异(步骤s704)。再者,将数据信号dq与第一数据选取信号dqs_t的延迟时间再增加该延迟时间差异(步骤s706)。

85.举例来说,第0位元组通道(byte-0lane)的延迟时间为1个时钟周期,第1位元组通道(byte-1lane)的延迟时间为2个时钟周期,则两个位元组通道之间的延迟时间差异为1个时钟周期。再者,由于第0位元组通道(byte-0lane)的延迟时间较短,因此处理电路310进一步将第0位元组通道(byte-0lane)的延迟时间再加上延迟时间差异(亦即,1个时钟周期),使得第0位元组通道(byte-0lane)的延迟时间增加为2个时钟周期。接着,处理电路310再将数据信号dq以及第一数据选取信号dqs_t的延迟时间也再增加延迟时间差异(亦即,1个时钟周期)。如此,将可以确保所有信号的信号缘都是正确的。之后,即可进行写入训练程序。

86.由以上的说明可知,本发明提出一种运用于存储器系统的多循环写入均衡程序的处理方法。当存储器系统进行写入均衡程序后,于进行写入训练之前,先进行本发明的多循环写入均衡程序。如此,将可确保时钟信号clk与第一数据选取信号dqs_t传递至ddr存储器120时,彼此的信号缘(signal edge)可以对齐(align)并且为正确的信号缘。

87.综上所述,虽然本发明已以优选实施例公开如上,然其并非用以限定本发明。本发明所属技术领域中技术人员,在不脱离本发明的精神和范围内,当可作各种的变动与润饰。因此,本发明的保护范围当视后附的权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。