type-c接口下拉控制电路及其供受电芯片与设备

技术领域

1.本实用新型涉及充电连接线领域,特别涉及一种type-c接口下拉控制电路及包含控制电路的供受电设备。

背景技术:

2.在usb type-c规范中,供电方在type-c接口cc引脚上需要有上拉,该上拉可以是电阻rp,如图1;也可以是电流ip,如图2,目的是告知受电方自己的供电能力。参见表1,受电方在type-c接口cc引脚上需要有下拉电阻5.1kω。当受电方没有连接到type-c口时,供电方的cc引脚被上拉到电源电压,供电方通过检测该引脚可知没有受电方,供电方的vbus引脚不供电。当受电方连接到type-c口时,供电方的cc引脚被下拉到一个固定电压,该电压可由rp 和5.1kω分压得到,或由上拉电流乘以5.1kω得到,以额定80ua上拉电流计算,得到408mv,是一个远低于电源的电压,供电方通过检测该引脚可知有受电方连接,供电方的vbus引脚供电。

3.表1规范中受电设备终端参数表

[0004][0005]

然而在实际应用中,一个设备即可以是供电方也可以是受电方,即可以根据情况选择启用供电模式和受电模式,这要求设备的cc引脚即有上拉电阻rp又要有下拉电阻5.1kω,但不能同时有效。当设备本身有电时,可以通过开关打开或者关闭上拉电阻rp或下拉电阻5.1kω,这就需要在上拉电阻或下拉电阻5.1kω上串联开关。这个开关带来新的问题,当该设备本身没电、且做受电方时,开关的输入端电位不确定,导致5.1kω有可能无法正常下拉,供电方无法检测到连接,就不会通过vbus向该设备供电,该设备没有电就不能正常打开5.1kω下拉,进入死循环,该设备不能正常上电,设备无法正常工作。

[0006]

现有技术如图3所示,用一个pmos开关串联5.1kω,pmos管栅极有下拉电阻,并由ctrl控制。原理如下,当该设备连接到供电方时,由于设备本身没电, ctrl可以理解为浮空,被pmos管栅极的下拉电阻下拉到gnd。连接后,供电方的上拉电阻rp或上拉电流连接到pad,pmos管源极电压上升,直到pmos 管开启,5.1kω连接到pad,供电方检测到pad的电压后发现有受电方连接,供电方通过vbus向受电方供电。但是,该方案存在一个问题,pmos管开启电压过高,导致在上拉电流较小的应用场景下,pad电压大于上拉电流与5.1kω的乘积,使供电方检测到cc引脚的pad电压比原本应该检测到的电压高出不少,从而误判没有连接。例如,pmos管阈值电压即开启电压约为0.8v,即pmos 管在v

gs

>=0.8v时才开启,因此pad端的电压>=0.8v。由表2供电设备参数表可知,供电方上拉电流最小为80μa,80μa乘以5.1kω得408mv,只有pad电压的一半,两者相差较大。因此,供电方检测到0.8v后,会以为是

一个10kω下拉,而不会认为是type-c规范规定的5.1kω下拉,因此有可能会误认为没有连接。

[0007]

表2规范中供电设备终端参数表

[0008]

技术实现要素:

[0009]

发明目的:为了解决现有技术中,既可作为供电方也可作为充电方的设备不便于控制其type-c接口上5.1k欧姆下拉电阻的开关的问题,本实用新型提供一种type-c接口下拉控制电路及其供受电芯片与设备。

[0010]

技术方案:一种type-c接口下拉控制电路,包括:

[0011]

第一电阻r1;

[0012]

第二电阻r2,其阻值不小于200kω;

[0013]

低阈值电压nmos管n1,漏极通过第一电阻r1连接type-c接口的cc引脚,源极接地,栅极连接第一nmos管n2漏极;设低阈值电压nmos管n1 导通电阻为r

nmos

,有0.9kω≤r

nmos

r1≤5.7kω;

[0014]

第一nmos管n2,漏极通过第二电阻r2连接type-c接口的cc引脚,源极接地,栅极连接第一信号。

[0015]

进一步地,还包括第二nmos管n3,所述第二nmos管n3的漏极连接低阈值电压nmos管n1的漏极,源极接地,栅极连接第二信号。

[0016]

进一步地,低阈值电压nmos管n1的开启电压不高于为400mv。

[0017]

进一步地,低阈值电压nmos管n1是native nmos管。

[0018]

进一步地,所述第一电阻r1的额定阻值为5.1kω。

[0019]

进一步地,所述第一电阻r1的额定阻值为1kω。

[0020]

进一步地,所述第一信号连接到微控制器或者供受电切换控制模块,第一信号在复位期间时为低电平,在复位结束后启用受电模式时为低电平,在复位结束后启用供电模式时为高电平。

[0021]

进一步地,当包含第二nmos管n3时,所述第一信号为复位信号,复位时为低电平,复位结束为高电平;第二信号连接到微控制器或者供受电切换控制模块,第二信号在复位结束后启用受电模式时为高电平,启用供电模式时为低电平。

[0022]

一种供受电芯片,包含type-c接口及上述的type-c接口下拉控制电路。以及包含该芯片的供受电设备。

[0023]

本实用新型提供一种type-c接口下拉控制电路及其供受电芯片与设备,相比较现有技术,存在以下有益效果:

[0024]

(1)当设备本身没电只能作为受电方时,仍然可以通过控制电路使下拉电阻有效,

使受电设备能够正常被检测,从而正常受电工作;

[0025]

(2)低阈值电压nmos管做开关,开启电压低,即使在最小上拉电流80 μa应用环境下,也能够满足type-c规范,使得供电端能检测到pad有下拉电阻。不会因为实际检测到的pad电压过高,而误认为没有受电设备连接,使设备的检测连接更可靠;

[0026]

(3)电路精简,元器件使用少。

[0027]

(4)低阈值电压nmos管优选采用native nmos,native nmos管在半导体工艺中是一种精度相对较差的非主流器件,当前主流三阱cmos工艺均可提供该类型的mos管,通常需要增加pwell阻挡的版图层,一般工艺中称为 psub、pwell block(简称pwb)或zpw、native等名称,但经过逻辑运算后,实际不增加任何物理的mask层,所以不增加任何额外制造成本。

附图说明

[0028]

图1为type-c接口供电方采用上拉电阻检测有效连接的原理图;

[0029]

图2为type-c接口供电方采用上拉电流检测有效连接的原理图;

[0030]

图3为现有技术使用pmos管控制下拉电阻的控制电路的原理图;

[0031]

图4为实施例一type-c接口下拉控制电路的原理图;

[0032]

图5为实施例二type-c接口下拉控制电路的原理图。

具体实施方式

[0033]

下面结合附图和具体实施例对本发明做进一步解释说明。

[0034]

实施例一:

[0035]

一种供受电设备drp,既可以作为供电设备,也可作为受电设备。该供受电设备内含有供受电芯片,所述供受电芯片内包含type-c接口及该接口cc引脚上的下拉控制电路。当设备本身无电时,可以导通电路使下拉电阻有效,使所连接的供电设备能够检测到5.1kω下拉电阻,从而检测到受电设备的连接。

[0036]

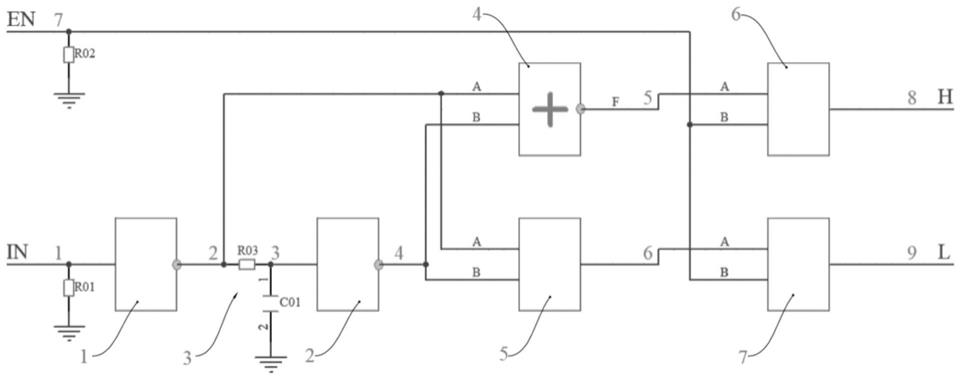

如图4所示,type-c接口下拉控制电路包括:

[0037]

第一电阻r1;

[0038]

第二电阻r2,至少为200kω的高阻值电阻,本实施例中选择1000kω的电阻作为r2;

[0039]

低阈值电压nmos管n1,优选native管,无需增加成本,也可以选择其他低阈值电压nmos管。本实施例选择的低阈值电压nmos管的开启电压为 100mv左右,也可以是不低于400mv的其它低阈值电压nmos。其中,阈值电压指开启的最小电压v

th

。漏极通过第一电阻r1连接type-c接口的cc引脚,源极接地,栅极连接第一nmos管漏极。

[0040]

设低阈值电压nmos管n1导通电阻为ron,根据type-c规范要求,需要满足ron r1在5.1kq*(1

±

10%)的范围内,才能够在第一电阻r1有效时,被供电设备识别到。比如本实施例选择r1为5.1kq,低阈值电压nmos管n1导通电阻ron通常为数q到数百q,可以对r1和低阈值电压nmos管n1的参数选择进行调整,使得两者串联累计电阻在理论上能够满足规范要求即可。

[0041]

第一nmos管n2,该nmos管为普通nmos管,其漏极通过第二电阻r2 连接type-c接口

的cc引脚,源极接地,栅极作为ctrl1端连接第一信号,第一信号一般由微控制器或者供受电切换控制模块提供。该第一信号用于在该设备上电完成后控制5.1kq下拉电阻是否有效,即控制第一电阻r1是否有效。

[0042]

本实施例的控制电路的工作原理如下:

[0043]

本设备通过type-c接口与供电方连接,供电方提供80μa上拉电流经过pad 流入本设备的cc引脚。在本设备自身没电的情况,第一信号输入的ctrl1端可视为浮空,假设低阈值电压nmos管初始时不开启,80μa上拉电流会通过r2 向其栅极充电,直到栅极电压达到开启电压,因为是低阈值电压nmos管,其开启电压较小,最多400mv。然后低阈值电压nmos管导通,电流经过5.1kq 和低阈值电压nmos的导电沟道流向地。80μa上拉电流在5.1kω上产生408mv 压降,pad电压为408mv,低阈值电压nmos的栅极电压为408mv,低阈值电压nmos正常开启。至此,供电设备从外部pad看进去的电阻为5.1kq,故可以被供电设备正常地检测到。

[0044]

供电设备检测到pad电压后,判断出有受电设备连接,并由vbus向受电设备供电。受电设备有电后,开始上电过程。

[0045]

上电完成后通过ctrl1端输入第一信号,以确定5.1kq下拉电阻是否继续有效。第一信号复位时为低电平,复位后启用受电模式时是低电平,复位后启用供电模式时是高电平。若第一信号为高电平,第一nmos管导通,将低阈值电压 nmos的栅极短接到地,低阈值电压nmos管断开,从pad看进去是第二电阻r2,即1000kω高阻值电阻,此时相当于关掉了5.1kω下拉电阻(使5.1kω下拉电阻无效)。若第一信号为低电平,第一nmos管断开,低阈值电压nmos的栅极等于pad电压,当有供电设备的上拉电流流入时,如前所述pad对外呈现 5.1kq下拉,此时相当于保持5.1kq下拉电阻开启(使5.1kω下拉电阻继续有效)。

[0046]

至此,受电设备插入、连接、受电、控制5.1kq下拉电阻开关的全过程结束。

[0047]

理论上,低阈值native nmos关闭后比普通nmos漏电要大,但经计算和实测,漏电仅在微安级以下,未超过usb type-c规范中的允许数额,也完全不影响功能和使用。

[0048]

实施例二:

[0049]

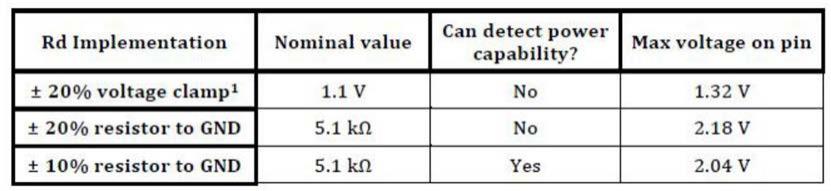

为了进一步增强开关导通能力,提高5.1kω下拉电阻的精度,还可在实施例一的低阈值电压nmos管n1上并联第二nmos管n3,第二nmos管n3为普通nmos管。如图5所示,所述第二nmos管n3的漏极连接低阈值电压nmos 管的漏极,源极接地,栅极作为ctrl2端连接第二信号,第二信号一般由微控制器或者供受电切换控制模块提供。本实施例中,第一信号实际为复位信号,复位时为低电平,复位结束为高电平。第二信号用于在需要保持5.1kω下拉电阻有效时,将第二nmos管n3代替低阈值电压nmos管n1,以此提高电路的导通能力,使得5.1kω下拉电阻的精度更高,避免因低阈值电压nmos管n1导通电阻较大影响开关导通。

[0050]

本实施例控制电路的工作原理如下:

[0051]

本设备通过type-c接口与供电方连接,供电方提供80μa上拉电流经过pad 流入本设备的cc引脚。在本设备自身没电的情况下,第一信号输入的ctrl1端可视为浮空,假设低阈值电压nmos管初始时不开启,80μa上拉电流会通过r2 向其栅极充电,直到栅极电压达到开启电压,因为是低阈值电压nmos管,其开启电压较小,最多400mv。然后低阈值电压nmos管导通,电流经过5.1kq 和低阈值电压nmos管的导电沟道流向地。80μa上拉电流在5.1kω上产生 408mv压降,pad电压为408mv,低阈值电压nmos的栅极电压为408mv,低阈值电压nmos正常开启。至此,从pad看进去的电阻为5.1kq,可以被供电设备正常地检测到。

[0052]

供电设备检测到pad电压后,判断出有受电设备连接,并由vbus向受电设备供电。受电设备有电后,开始上电过程。首先,产生上电复位。此复位期间,第一信号复位为低电平,且第二信号优选为高电平。第一nmos管断开,且第二nmos管优选开启,当供电设备向pad输入上拉电流时,pad对外呈现5.1kq 下拉电阻。上电复位结束后,第一信号为高电平,第二信号根据需要控制,启用受电模式时为高电平,启用供电模式时为低电平。当第二信号为高电平时,第一nmos管导通,且第二nmos管导通,低阈值电压nmos管栅极被短接到地,低阈值电压nmos管断开。由于第二nmos管导通,pad对外呈现5.1kω下拉,电流经过5.1kω电阻和第二nmos管的导电沟道流向地,此时相当于用第二 nmos管代替了低阈值电压nmos管。若需要关掉5.1kω下拉电阻,在上电复位结束后,第一信号为高电平,第二信号被控制设置为低电平,即可关掉5.1k ω下拉。此时,第一nmos管导通,且第二nmos管关断,低阈值电压nmos 管栅极被短接到地,低阈值电压nmos管断开,第二nmos管也断开,从pad 看进去的是第二电阻r2,即1000kq高阻值电阻,此时为关掉了5.1kq下拉电阻。实际上,如作为供电设备,自身总是先上电,复位后就可以关闭5.1kq下拉电阻,当准备好对外供电时,再启用上拉电阻或者上拉电流。

[0053]

至此,受电方插入、连接、受电、控制5.1kq下拉电阻开关的全过程结束。

[0054]

增加并联的第二nmos管n3,之所以能够提高控制电路的导通能力,理由如下:

[0055]

因为低阈值电压nmos管的v

gs

只有几百mv,过驱动电压不高导致导通电阻不可忽略,而且导通电阻随工艺、温度的影响变化较大。最终使从pad看进去的电阻超过5.1kω*(1 10%),导致有可能处于type-c规范要求的边缘,不利于产品的一致性。例如:

[0056]

因为低阈值电压nmos的v

gs

由i

pu

*(r1 r

nmos

)确定,i

pu

为供电方的上拉电流,r1、r

nmos

分别是第一电阻r1阻值和低阈值电压nmos的导通电阻。根据type-c规范,可知最坏情况下i

pu

最小为80μa,假设r1 r

nmos

为5.1kq,则 v

gs

只有408mv。因此低阈值电压nmos的过驱动电压v

on

=v

gs-v

th

,只有几百mv。由于v

on

过小,导通电阻的阻值受工艺、温度的影响变化较大。

[0057]

mos管的导通电阻公式如下:

[0058]

ron=k(v

gs-v

th

)=k*v

on

[0059]von

为过驱动电压。假设v

th

=0.3v,v

on

=0.108v。

[0060]

相比之下,并联的第二nmos管的栅压来自受电设备自身的电源电压,可达到3.3v。假设第二nmos管的v

th

=0.7v,其v

on

=3.3v-0.7v=2.6v,是0.108v 的24倍之多。可以看出,并联的第二nmos管的导通电阻远小于低阈值电压 nmos的导通电阻,此时使用第二nmos管代替低阈值电压nmos管可实现开关导通能力的提高,提高产品特性的一致性。

[0061]

实施例三:

[0062]

实施例三与实施例一或实施例二相比,区别在于第一电阻r1的额定阻值为 1kω。对于下拉电阻1kω的应用场景,该方案也是适用的,但是需要低阈值电压nmos管有更低的阈值电压,其电路结构与工作原理同实施例一或实施例二。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。