一种高性能低功耗的esim卡芯片系统

技术领域

1.本发明涉及esim卡芯片技术领域,尤其涉及一种高性能低功耗的esim卡芯片系统。

背景技术:

2.esim卡是具有iso7816和swp两个接口功能的sim卡,目前市面上的esim卡芯片主要面向移动支付应用,使用在手机等移动设备的芯片。目前的市场广泛使用的esim卡芯片,其芯片设计使用32-bitarm系列risc处理器,内部具有40kb sram、1mb flash用作数据的存储。esim卡芯片多使用ahb、apb总线结构。当今的市场上,各类esim卡应用越来越多,使用到芯片内的加解密模块的功能的场景越来越多,因此对于手机等移动设备的电池待机时长,即有高性能又有较低的功耗的esim卡芯片是将来手机市场的趋势。

3.目前市场上得主流esim卡芯片中,存在两种主流芯片:

4.1、第二种esim卡芯片使用的总线结构为:ahb总线上挂接系统交互频繁、数据吞吐量大、性能要求高的外设模块,包括存储器系统、系统控制模块、des、aes、sm1、sm3、sm4、pke、crc等。存储器安全管理机制,可对算法提供高安全级别的保护。通过调用软件库的方式来实现目标算法。该芯片的apb总线上挂接与系统交互次数较少、数据量小、性能要求低的模块,包括7816、gpio、swp、spi、rng、timer、wdt等。

5.该款esim卡芯片,片上nvm(特指flash)接口主要特性:页大小为512b,支持页/块擦、页写、页写校验、页擦写、页擦写校验、buf清除操作。nvm写操作是以页为最小单位,因此在执行nvm各种页写命令之前,软件必须保证写满整页数据,对于该页内从未写过的地址可以写成全f,否则无法保证未写入地址中数据读出的有效性。

6.该款esim卡芯片的功耗管理:执行wfe指令进入standby状态后,所有中断信号都可以唤醒芯片。standby模式是系统主动进入的的低功耗模式。在7816接口、swp接口都不处于工作状态时系统才可以进入standby模式。在芯片进入standby过程中,任一接口的活动都将直接唤醒芯片退出standby状态。在该芯片中,其iso7816接口在读卡器停止外部时钟情形下,方可以进入低功耗模式。其swp接口在c6管脚处于suspended状态下,当uicc收到shdlc层对uicc请求不再通信的响应信息,且swp接口处于suspended状态时,swp接口方可以进入低功耗模式。

7.该芯片的cpu hold模式包括pke低功耗模式和flash操作低功耗模式,pke低功耗模式具体为:为了防止pke工作时系统功耗过大,可以通过设置功耗控制寄存器的相应参数,选择低功耗模式。选择pke低功耗模式时,cpu启动协处理器运算后,cpu时钟将停止,以降低系统功耗。协处理器运算结束后,自动恢复cpu时钟,退出协处理器低功耗模式。flash操作低功耗模式具体为:为了降低flash erase和program操作时的系统功耗,可以通过设置功耗控制寄存器的flashlpmode参数,选择flash操作低功耗模式。在flashlpmode=1时,cpu启动flash erase或program后,cpu时钟将停止,以降低系统功耗。erase/program结束后,自动cpu唤醒时钟,退出flash操作低功耗模式。

8.从这款芯片的cpu hold模式操作流程可以看到,对于pke,flash的大功耗操作只是将cpu时钟停止,以降低系统功耗,相当于是一种窜行的方式进行工作的。

9.这款芯片的llc层act及shdlc帧解析完全由上层软件来完成,swp仅在硬件层上完成mac层及llc层clt帧协议解析。所以在swp接口上其功能不够强大,因为软件需要按协议做大量的组包拆包及按协议控制通信等等工作,所以在swp接口上其执行效能是很低的。

10.2、第二种esim卡芯片使用的总线结构为:在其ahb总线上只挂了nvm存储器,sram,及cpu等常用模块;其硬件加密协处理器和安全加密模块挂载在apb总线上,由于apb总线访问性能比ahb总线低,apb外设中断中断清除需要花费多个时钟周期,因此其性能不够高,对算法提供的保护不够高级别。其芯片支持etsi ts 102613规范的swp接口功能不够强大,它在swp硬件模块内部提供dma功能来进行数据的搬移,但需要用户自己的程序来解析数据包,从软件层上实现shdlc协议,因此芯片的swp接口的通信管理功能将会花费大量的系统资源,因此在swp接口上功能不够强大。

11.该芯片在swp、7816模块内部使用dma功能用于接口上的收发数据。而在ahb总线上并没有挂载使用dma ip控制器。

12.该芯片的低功耗管理,包括接口休眠的控制和休眠唤醒的控制管理。系统进入深睡眠需各接口均处于休眠状态。

13.该款esim芯片对大功耗的操作,例如nvm擦写,pke算法,cpu应处于浅睡眠状态。当操作完成后,相应的event将唤醒cpu。随即,cpu直接去执行wfe后面的一条命令,不跳转到isr。事件唤醒浅休眠cpu的流程可参见图1。

14.该款esim芯片的ram总容量为40kb,cpu可访问,32kb通用ram,8kb各通讯接口特定缓冲区。nvm页面大小为512b,每个页面包括2个大小为256b的半页。

15.该款esim芯片的页面擦除操作为对512b的页面一次性全部擦除;该款esim芯片的写操作使用半页内指定双字编程,即通过将待写的数据写入到缓冲区内指定位置上,标记将要写入的地址和数据。写入数据必须是若干双字(n*8字节)。启动编程动作后将一次性对这些已被标记的双字进行数据编程。编程后状态:读出值即写入值。nvm编程时间:tfp=100μs 53μs*n,其中,n表示双字数据的个数。该芯片的nvm页面512b编程需要时间2*(100μs 53μs*32)=3592μs。写操作的具体过程为:设置芯片nvm控制寄存器-向nvm目标地址写入待编程的数据,起始地址必须为双字对齐地址,写入个数必须为双字(8字节)的整数倍-设置芯片nvm控制寄存器-向nvm目标页任意地址写入0xffffffff-用户程序设置cpu进入休眠(wfe/wfi)-查询sfr nvmsts是否结束,nvmsts1是否有错误-清除sfr nvmsts和sfr nvmsts1。

16.javacard应用程序称为applet,它必须符合java card规范。java卡applet的基本构成为:

17.1、install()方法:当applet下载至java卡时,就会启动install()方法来安装applet,并传入applet安装所要的参数。

18.2、register()方法:applet安装后要调用register()方法将applet注册给jcre。

19.3、select()方法:运行某一个applet之前,jcvm首先要调用select()方法,将applet选中。

20.4、process()方法:该方法是applet工作时的核心方法。终端给卡发送命令apdu

后,cos首先接收这个apdu,然后,把apdu传递给jcre,jcre把apdu送给当前选择的applet的process方法进行处理。process方法一般设计成分支选择结构,根据命令apdu的不同,执行不同的处理方法,并将处理结果回送jcre,直到返回给终端。我们开发设计一个applet,主要工作就是根据要求,编写process方法。

21.globalplatform环境(以下简称open)的主要职责是为应用提供api、命令分发、应用选定、逻辑通道管理(manage channel命令只被open处理,不会分发给应用)和卡内容的管理。

22.open执行ap代码的装载和相关的卡内容管理。

23.open也要负责已装载到卡里的应用的安装。open要执行为应用装载和安装所定义的安全原则。这些原则包括对应用代码和卡发行者提供的应用装载和/或安装授权书的验证。

24.open另一个重要的职责是apdu命令的分发和应用的选择。当open接收到select命令时,它将select命令中指定的应用设置成被选择的应用,后续的应用命令应该被分发给这个被选定的应用。

25.除了manage channel命令及select命令,所有其它命令直接分发给基本逻辑通道上当前被选定的应用。

26.图2为现有java card的系统框架图,可以看到java card的最底层为hardware,即芯片。位于硬件上的为卡上操作系统os(operating system),通常为定制的微型操作系统(rtos),在操作系统上的则是java card运行时环境jcre(java card runtime environment),jcre包括java card虚拟机jcvm(java card virtual machine),jcvm能够解析并执行java card字节码,从而使得java card应用程序能够在卡片上正常运行。global platform运行时环境open则为应用程序提供命令分发、应用选定、逻辑通道管理和卡内容管理等功能,应用可通过调用位于open之上的gp api来使用这些服务。发卡方安全域isd(issuer security domain)能够管理卡内容、卡生命周期和应用程序生命周期,是其他安全域的基础,是卡片管理者在卡内的代表;而补充安全域ssd(supplementary security domain)则可以为应用提供方提供安全域,是应用提供方在卡片内的代表。jc api(java card application programming interface)是java card的应用程序接口,运行在java card上的应用程序app1、app2可通过jc api来使用jcre提供的服务。

27.目前esim卡基本上都是基于java卡平台实现的。在java平台中,存在多次写flash来备份数据等等写flash的需求,而每一条apdu指令通过事务机制保证擦写flash的原子性。因此提高apdu指令的解析速度及flash的写速度及其重要。

28.从市场化的角度考虑,在esim卡制造商的芯片硬件性能是固定的前提下,一方面可以从java applet源代码的编写方式进行优化,使用更科学的算法设计方法,优化代码执行流程,使得更有规律性,计划性的执行高耗时操作等,可以直接提升该应用的执行效率。但是因为java卡环境下applet的开发方是不可控的,因此从applet的编写角度提出优化要求视乎不可行,本设计发明从java虚拟机执行与dma并行的角度提升性能。一般的java虚拟机需要载入方法表单,并根据偏移位置载入相应的java虚拟机机器码,从而完成方法调用。而java卡的每个组件的表单格式的数据结构的内容都存储在flash存储单元中,读取和解析工作需要多次的flash读取和檫写操作。

29.当目标应用被java虚拟机选择执行时,java虚拟机会找到该应用的java虚拟机机器码对应的flash存储位置,并将其载入java虚拟机进行解析、执行。对于堆栈的操作,由于缓存数据在芯片的ram中操作,而ram读写速度远远大于flash存储域,堆栈操作的执行速度会很快。但是受制于现有java卡芯片硬件水平的限制及芯片成本考虑,不可能将所有的数据放置在ram中操作,所以大部分数据仍只能存储在flash存储器中,而flash存储器的操作速度要远远低于ram储存器,因此在一定的硬件条件基础下,影响java api的执行效率的关键因素在于flash存储器读写速度慢。

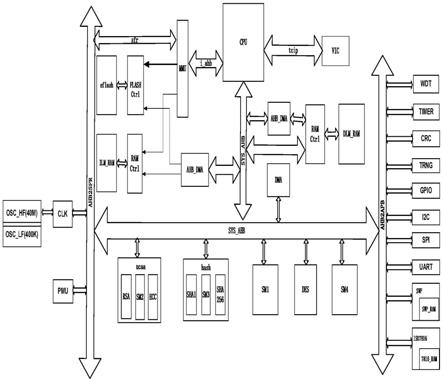

30.从前面市面上的主流esim卡芯片资料来看,都存在写flash时cpu处于停止状态,wfe、fei指令会关闭cpu时钟,即对于nvm中的程序,执行擦、写操作后,后续指令将被挂起,直到擦除、编程操作结束后,才可以继续执行程序,相当于窜行操作,就会影响java卡的执行性能。这些esim卡芯片内部在ahb总线上没有挂载dma控制器,它们在swp接口上的功能不够高效,需要程序自己进行shdlc协议的管理控制,包括组装数据包、解析数据包、通信计时等等处理,因而势必会增加芯片功耗。另外这些芯片都是在通信结束的情况下才可以进行低功耗模式,在java卡技术来看,其功耗控制是基于应用事务的,因而cpu工作时间会较长,会增加芯片功耗。

技术实现要素:

31.本发明的目的在于提供一种高性能低功耗的esim卡芯片系统,从而解决现有技术中存在的前述问题。

32.为了实现上述目的,本发明采用的技术方案如下:

33.一种高性能低功耗的esim卡芯片系统,包括cpu、mmu存储器管理模块、eflash模块、ilm_ram模块、dlm_ram模块、pmu功耗控制模块、clk时钟控制模块、ahb_dma模块、ucaa运算模块、hash运算模块、dma直接存取模块、sm1运算模块、des运算模块、sm4运算模块以及可配置的矢量中断控制器;

34.所述cpu通过i_ahb总线与mmu存储器管理模块相连,所述mmu存储器管理模块经flash_ctrl接口和ram_ctrl接口分别与eflash模块以及ilm_ram模块相连;所述cpu通过sys_ahb总线与ahb_dma模块、ucaa模块、hash模块、dma直接存取模块、sm1运算模块、des运算模块以及sm4运算模块相连;所述ahb_dma模块经flash_ctrl接口与eflash模块相连,所述ahb_dma模块经ram_ctrl接口与ilm_ram模块以及dlm_ram模块相连;

35.所述sys_ahb总线与ahb2apb控制线相连,所述ahb2apb控制线上连接有看门狗、计数器、循环冗余校验模块、纯数字真随机数发生器、可编程io模块、iic接口模块、spi接口模块、uart接口模块、swp接口模块和7816接口模块;

36.所述mmu存储器管理模块经sfr总线与ahb2sfr控制线相连,所述clk时钟控制模块和所述pmu功耗控制模块均连接在ahb2sfr控制线上;所述clk时钟管理模块与osc_hf时钟和osc_lf时钟相连;

37.所述cpu通过支持单个cpu时钟周期访问的紧耦合ip与可配置的矢量中断控制器相连;

38.所述ram_ctrl接口为sram的控制接口,用于控制sram的读写操作;

39.所述flash_ctrl接口为flash的控制接口,用于控制flash的读写操作;

40.所述osc_hf时钟为源时钟或者经过分频后为系统提供正常工作时钟;

41.所述osc_lf时钟为唤醒cpu的唤醒时钟。

42.优选的,针对由open选定的应用,虚拟机对选定的applet应用的process方法执行mmu存储器管理模块的remap操作,即借助dma直接存取模块,从该应用的process方法对应的flash地址处将其对应的执行代码复制到ilm_ram模块的空间上,让其对应的代码在ram内存中执行,从而提高执行效率;

43.所述remap操作的具体过程为:

44.将flash中地址n1kb~n2kb的程序搬移到ilm_ram模块中的n3kb~n4kb空间中;

45.重映射源地址寄存器、重映射目的地址寄存器、重映射长度寄存器;

46.重映射使能寄存器,启动加速机制;使能寄存器重映射后,访问flash的n1kb~n2kb地址空间时,实际为访问sram的n3kb~n4kb空间;

47.寄存器重映射配置完成后,dma直接存取模块开始搬移工作,同时cpu运行java虚拟机代码。

48.优选的,对每个被java虚拟机选定的新应用都会根据其process表单源地址及表单字节数,尽可能多得将flash中的内容搬移到内存中运行,从而提高applet的执行效能。

49.优选的,当需要从flash中读取page内容时,使用dma直接存取模块的页读功能;当要修改flash中page内容时,使用dma直接存取模块的页檫除并写功能。

50.优选的,系统中java主循环由接口上的中断来驱动固件,固件解析完apdu指令后进入wait模式,当系统向主机发送响应数据包完成中断产生后,将cpu从wait模式唤醒,而后进入更深层次的低功耗stop模式;

51.若需要擦写flash,使用dma直接存取模块来按页擦写flash,且程序在ilm_ram模块中运行;在这种情况下,cpu从wait模式下被唤醒两次,一次是dma burst pagewrite完成中断,另一次是接口发送完成中断;而后进入stop模式;

52.系统提供burst写功能,限制每次burst写最大长度为64word。

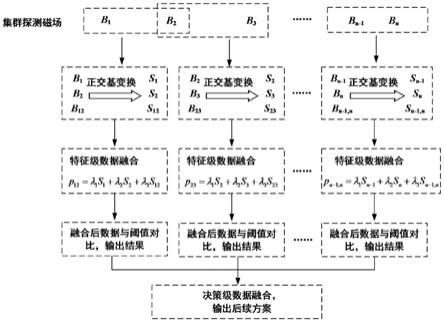

53.优选的,系统包括,

54.指令低功耗模式;cpu执行执行指令进入低功耗的模式,分为stop模式和wait模式;

55.stop模式具体为:设置cup的stop指令,在stop模式下,除通信接口中由有外部时钟和内部osclf直接驱动的部分电路外,系统其它部分的时钟全部停止,模拟模块进入stop状态从而降低系统功耗;通信接口接收到数据/命令后,或接收到复位信号后,退出stop模式,系统时钟恢复为原来值;

56.wait模式具体为:设置cpu的wait指令,cpu进入wait状态,这时cpu的时钟停止,以降低功耗,当中断发生时,cpu退出wait状态;

57.ucaa低功耗模式;当applet要使用ucaa算法时,通过调用系统提供的ucaa apis函数来完成算法,在ucaa apis函数中设置寄存器,选择ucaa低功耗模式;在ucaa低功耗模式下,cpu启动ucaa运算模块后,系统其它部分的时钟将停止,以降低系统功耗;运算结束后,自动恢复系统时钟,退出低功耗状态;

58.在ucaa低功耗模式下,当rsa算法开始运算后,clk时钟管理模块、eflash模块、des运算模块、sm1运算模块都将停止;

59.nvm擦写低功耗模式;当applet要使用擦写flash时,通过调用系统提供的writeflash apis函数来完成,writeflash apis函数根据实际的擦或写或搬移功能设置寄存器,选择nvm擦写低功耗模式;在nvm擦写低功耗模式下,cpu启动flash erase或program后,系统其它部分的时钟将停止,以降低系统功耗;erase/program结束后,自动恢复系统时钟,退出低功耗状态;

60.在nvm擦写低功耗模式下,当flash erase/program期间,clk时钟管理模块、ucaa运算模块、des运算模块、sm1运算模块都将停止。

61.优选的,系统的java虚拟机的工作流程为:

62.s1、系统上电后,cpu执行环境初始化,使用dma直接存取模块的搬移功能,从flash中将7816接口、swp接口和isr接口、writeflash api、java_loop拷贝到ilm_ram模块上,得到系统中可以用于remap的起始地址:0x00a01000;

63.s2、系统java虚拟机初始化;

64.s3、根据接口硬件检测结果,对7816接口和swp接口做寄存器配置,使能寄存器相应的接口中断;设置sys_waitingcnt,设置sys_jobcnt为0;从步骤s4开始进入虚拟机主循环java_loop api,它是iram程序;

65.s4、若sys_waitingcnt不等于0,则调用汇编指令使得系统进入wait模式,重复步骤s4,直到被中断唤醒;若sys_waitingcnt等于0,则进入步骤s5;

66.s5、调用汇编指令使得系统进入最低功耗stop模式;

67.s6、系统接收到apdu指令,退出stop模式,若当前激活接口是7816接口,则设置apdu数据缓冲区指针到7816接口的数据缓冲区;若当前激活接口是swp接口,则设置apdu数据缓冲区指针到swp接口的数据缓冲区;sys_jobcnt减少1;

68.s7、java虚拟机检查apdu指令,若当前指令不是manage channe命令或select命令,则进入步骤s9;若当前指令是manage channel命令,则java虚拟机进行相应的处理,写返回数据到apdu数据缓冲区中,之后进入步骤s10;若当前指令是select命令,则进入步骤s8;

69.s8、由open选定当前目标应用之后,对该应用的process方法执行mmu存储器管理模块的remap操作,即从该应用的process方法对应的flash地址处将其对应的process方法表单字节码对应到的flash页面地址,借助dma直接存取模块的搬移功能,拷贝到ilm_ram模块的空间上,获取该方法的表单字节数remapsize并对齐到整k字节数,若remapsize大于12kb,则设定remapsize等于12kb,重映射原地址寄存器的源地址为表单flash整k字节数地址处,重映射目标地址寄存器的目标地址为0x00a01000,重映射长度寄存器的长度为remapsize,使能寄存器执行重映射功能,此时借助dma直接存取模块与cpu并行执行的特点,将remap的flash内容拷贝到ilm_ram模块上,最大12kb;java虚拟机写返回数据到apdu数据缓冲区中,之后进入步骤s10;

70.s9、java虚拟机调用当前被选定的应用,对apdu指令进行解析,由于重映射了12kb的process方法操作所对应的字节码到ilm_ram模块上,所以能够提高java解析apdu指令的执行效能;若applet的process需要写flash,通过调用系统wrtflash api来将512b的数据写回flash,借助dma burstwrite功能将数据写入到目标flash地址处,在wrtflash api设置sys_waitingcnt增加1,dma直接存取模块完成中断,在该中断服务程序中将会设置sys_

waitingcnt减少1次;写返回数据到apdu数据缓冲区中,之后进入步骤s10;

71.s10、对当前接口,调用系统发送api将apdu数据缓冲区的数据发送给主机,在发送api中设置sys_waitingcnt增加1,并使dma直接存取模块发送完成中断,在该中断服务程序中将会设置sys_waitingcnt减少1;

72.s11、如果sys_jobcnt不等于0,则返回步骤s6;否则返回步骤s4。

73.优选的,所述ucaa运算模块中包含有rsa算法、sm2算法、ecc算法;所述hash运算模块中包含有sha1算法、sm3算法、sha256算法。

74.优选的,所述ilm_ram模块为16kb的单端口sram;所述dlm_ram模块为24kb的单端口sram。

75.本发明的有益效果是:1、系统在ahb总线上挂载了dma直接存取模块,使得程序的执行可以最大程度的并行化,从而大大的提高java卡的执行效能,减少了芯片工作时间,从而降低esim芯片整体功耗。2、在sys_ahb总线上挂载了ilm_ram模块并与cpu通过i_ahb总线相连,在使用中将需要提速的代码放在ilm_ram模块执行可以最大程度的并行化,从而大大的提高java卡的执行效能,减少了芯片工作时间,降低esim芯片整体功耗。3、将7816接口中断服务程序、swp接口中断服务程序、dma中断服务程序,writeflash api等关键功能固件代码定义成逻辑在ilm_ram模块上的,物理在flash上的,在ilm_ram模块中执行的程序,以提高整个芯片指令处理性能。4、在主机端下发apdu select指令,java卡虚拟机接收并解析到要选择一个不同的新的applet时,java卡虚拟机进一步处理取得选定applet的procees方法表单对应得flash页面地址及其表单的字节数大小,将对这段的flash内容进行mmu remap,这样重映射设计是动态的,即切换applet时,就会为新的applet做mmu remap操作,为关键代码做提速处理,从而提高java卡虚拟机的效能。5、使用dma的搬移功能来写flash页面,这实现并行化处理指令,提高芯片执行性能;writeflash api是ilm_ram程序,applet的的procees方法也在ilm_ram模块中运行,因此在进行flash页面编程时同时可以正常运行procees方法,而在java卡应用中写flash页面是经常使用到的操作,因而可以极大的提高java卡的性能。6、对flash的编程操作,都是通过dma直接存取模块进行的,因而能够与cpu运行固件并行化处理。在本芯片里flash最小编程单位为一个word即4个字节,flash写入四个字节需时25微秒,本系统的flash页面512b编程时比市面上的主流esim芯片的flash页面512b编程时间要快上一倍,当java卡应用在使用本发明设计的dma burst读写功能,java卡应用的执行效能更高,由于flash的编程时间大大减少了,因而可以大大降低整个芯片功耗。一个当在flash页面在快要写满时,才需要使用dma burst写功能将flash页面擦除后重新写入数据,在这样的策略下,esim卡在flash上的功耗会大大降低。7、系统低功耗控制架构,基于接口收发数据包状态主动进入低功耗模式的;接口ip的收发缓冲区使得,cpu处于wait模式下,接口自动发送数据包给主机,从而将接口上的cpu处理时间减少到最少,从而降低esim芯片整体功耗。8、swp接口在硬件层面上支持shdlc协议的通信控制,接收到数据包是hci层的数据,无需程序花费很多指令去进行shdlc组包以及shdlc通信协议控制。

附图说明

76.图1是现有的esim芯片事件唤醒浅休眠cpu的流程图;

77.图2是现有的java card系统框架图;

78.图3是本发明实施例中系统的结构示意图;

79.图4是本发明实施例中系统提供burst写功能的原理示意图。

具体实施方式

80.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施方式仅仅用以解释本发明,并不用于限定本发明。

81.如图3所示,本实施例中提供了一种高性能低功耗的esim卡芯片系统,包括cpu、mmu存储器管理模块、eflash模块、ilm_ram模块、dlm_ram模块、pmu功耗控制模块、clk时钟控制模块、ahb_dma模块、ucaa运算模块、hash运算模块、dma直接存取模块、sm1运算模块、des运算模块、sm4运算模块以及可配置的矢量中断控制器;

82.所述cpu通过i_ahb总线与mmu存储器管理模块相连,所述mmu存储器管理模块经flash_ctrl接口和ram_ctrl接口分别与eflash模块以及ilm_ram模块相连;所述cpu通过sys_ahb总线与ahb_dma模块、ucaa模块、hash模块、dma直接存取模块、sm1运算模块、des运算模块以及sm4运算模块相连;所述ahb_dma模块经flash_ctrl接口与eflash模块相连,所述ahb_dma模块经ram_ctrl接口与ilm_ram模块以及dlm_ram模块相连;

83.所述sys_ahb总线与ahb2apb控制线相连,所述ahb2apb控制线上连接有看门狗、计数器、循环冗余校验模块、纯数字真随机数发生器、可编程io模块、iic接口模块、spi接口模块、uart接口模块、swp接口模块和7816接口模块;

84.所述mmu存储器管理模块经sfr总线与ahb2sfr控制线相连,所述clk时钟控制模块和所述pmu功耗控制模块均连接在ahb2sfr控制线上;所述clk时钟管理模块与osc_hf时钟和osc_lf时钟相连;

85.所述cpu通过支持单个cpu时钟周期访问的紧耦合ip与可配置的矢量中断控制器相连;

86.所述ucaa运算模块中包含有rsa算法、sm2算法、ecc算法;具体包含哪些算法可以根据实际情况进行选择。

87.所述hash运算模块中包含有sha1算法、sm3算法、sha256算法;具体包含哪些算法可以根据实际情况进行选择。

88.所述ilm_ram模块为16kb的单端口sram;指令ram,可用于代码重映射。起始地址:0x00a00000

89.所述dlm_ram模块为24kb的单端口sram;数据ram;

90.所述ram_ctrl接口为sram的控制接口,用于控制sram的读写操作;

91.所述flash_ctrl接口为flash的控制接口,用于控制flash的读写操作;

92.所述clk时钟管理模块包括oschf和osclf;

93.所述osc_hf时钟为源时钟或者经过分频后为系统提供正常工作时钟;

94.所述osc_lf时钟为唤醒cpu的唤醒时钟。

95.系统中各个组成模块的详细解释参见表1。

96.表1系统各模块简单描述

97.98.[0099][0100]

本实施例中,系统采用国产具有自主知识产权的32位risc安全cpu核,芯片内置sm1、sm4、aes、des等常用的密码算法硬核,具有功能强、接口多、功耗低的特点。

[0101]

cpu实现中央控制,程序存储空间在片内flash(1mb)中。系统sram大小是16kb 24kb,在本系统中16kb用于remap功能。cpu可以通过系统ahb总线,访问控制相应的寄存器,从而调度各个ip完成特定的工作。系统提供中断和dma服务,实现ip请求的快速响应和数据快速搬运。系统框图如图3所示。

[0102]

cpu采用国产32位安全risc处理器,通过i_ahb总线与mmu相连,通过sys-ahb控制线与ahb总线相连。cpu通过i_ahb总线可以执行ilm_ram模块(instruction local memory bus)中的程序,通过sys_ahb控制线访问dlm_ram模块(data localmemory bus)。

[0103]

本实施例中,针对由open选定的应用,虚拟机对选定的applet应用的process方法执行mmu存储器管理模块的remap操作,即借助dma直接存取模块,从该应用的process方法对应的flash地址处将其对应的执行代码复制到ilm_ram模块的空间上,让其对应的代码在ram内存中执行,从而提高执行效率。

[0104]

本实施例中,由于flash的读写速度较慢;但是读ram的速度最高可达40mhz。所以可以将flash中的程序搬移到ilm_ram模块中运行,以提高程序的执行速度。程序所在位置及大小均可配置(位置可任意配置,大小最多只能到16kb)。

[0105]

当用户欲实现程序加速,将需要加速的程序搬移到ilm_ram模块中以加快程序运行。软件配置remap长度、起始地址和目的地址,开启重映射功能(remap_en),既可以实现程序加速。

[0106]

则所述remap操作的具体过程为:

[0107]

将flash中地址n1kb~n2kb的程序搬移到ilm_ram模块中的n3kb~n4kb空间中;

[0108]

重映射源地址寄存器、重映射目的地址寄存器、重映射长度寄存器;

[0109]

重映射使能寄存器,启动加速机制;使能寄存器重映射后,访问flash的n1kb~n2kb地址空间时,实际为访问sram的n3kb~n4kb空间;

[0110]

重映射配置好相关的寄存器后,dma直接存取模块开始搬移工作,同时cpu运行java虚拟机代码,本系统的dma直接存取模块从flash搬移512字节的数据到内存中只需要8微秒的时间,而从主机端下发select apdu指令到下一条apdu指令被芯片接收到需要毫秒级别的时间,因此在下一条指令被解析时,目标应用的process方法就是在内存中执行的。

[0111]

dma直接存取模块支持存储器和存储器之间、存储器和io设备之间的数据交换,数据传输过程中不需要cpu参与,提高了系统的执行效率。其功能为:提高指令ram、数据ram、外设ram、flash之间数据搬移速度;方便释放cpu,提高系统执行效率;配合实现重映射功能,提高cpu执行指令的速度;配合实现flash的页写操作。

[0112]

本实施例中,在实际用户应用中,会经常性修改flash中内容,通过将一页(page=512b)即64word大小的内容读出后进行部分修改后,整页写回到flash中。由于本设计下的芯片flash编程最小单元一个word(4b),造成每次应用所需的整页写回功能只能通过一个word方式逐步写回。

[0113]

在本系统针对连续写的方式提出了burst写功能,限制每次burst写最大长度为64word,该目的在于加快写入速度,时间对比如下:单次写一个word所需25us,写完64word时间=64*25(us)=1600us;采用burst写,所需15us,写完64word时间=27 63*15 5(us)=977us;对比来说本系统的写入速度能够比原来提升将近40%。

[0114]

系统提供burst写功能的要求为:1、从应用实际操作来分析,首先修改整页前,会先将整页内容读出,软件开销存储进行缓存,修改后再慢慢写回,采用硬件设计,则首先需要一个整页512b的dram缓存。2、同时为了兼容常规的word写功能,增加一位寄存器进行指示当前是burst写还是word写。3、如果采用burst整页写功能,要求应用下发的逻辑地址必须是一个页的起始地址。4、硬件同时会增加整页读写完成的标志或中断控应用进行下一步处理。

[0115]

系统提供burst写功能的原理流程结构如图4所示。将该功能的实现基于dma直接存取模块进行,主要原因是dma直接存取模块本身就需要具备ram与flash之间的读写搬移功能。dma直接存取模块涉及到flash操作的情况,软件启动后可以不查询dma直接存取模块完成状态,继而软件可以同时进行其它并行操作。

[0116]

burst写功能按word方式去进行flash页面512b即的编程需要时间是单次写一个word所需25us,写完64word时间=64*25(us)=1600us,比目前市面上的主流esim芯片的flash页面编程时间快一倍。nvm页面大小为512b,编程需要时间2*(100μs 53μs*32=3592μs。

[0117]

本实施例中,对每个被java虚拟机选定的新应用都会根据其process表单源地址及表单字节数,尽可能多得将flash中的内容搬移到内存中运行,从而提高applet的执行效能。

[0118]

本系统中,当需要从flash中读取page内容时,使用dma直接存取模块的页读功能;当要修改flash中page内容时,使用dma直接存取模块的页檫除并写功能。因为使用了dma直接存取模块的功能,因而能够与cpu运行固件并行化处理,可以大大提高系统的性能。在本系统的芯片flash最小编程单元是一个word即4个字节。通过写入少量的word就可以存储下来相关信息,因此从而可以更好的降低整个esim卡芯片的flash编程功耗。

[0119]

从目前市场上的esim卡芯片来看,都存在nvm擦除或编程期间再次读nvm,后续指令将被挂起状态的情形。针对目前esim卡芯片的此问题,在本发明设计中将程序放在ilm_ram模块中运行,执行擦、写操作,程序可以继续运行,即cpu从ilm_ram模块中取指令并运行,在此同时flash处于擦除或编程状态之下,借此可以提高java卡的运行效能。

[0120]

从目前java卡的现有技术来看,大多使用定制的微型操作系统(rtos),这样的架构下,芯片的功耗控制的不是很好,这些芯片都是在接口通信结束的情况下才可以进行低功耗模式,在java卡技术来看,其功耗控制是基于应用的事务的,因而cpu工作时间会较长,会增加芯片功耗。

[0121]

本发明的系统则不使用定制的微型操作系统(rtos),java主循环由接口上的中断

来驱动固件,固件解析完了apdu指令就进入wait模式,当芯片完成向主机发送响应数据包完成中断产生后,将cpu从wait模式唤醒,而后进入更深层次的低功耗stop模式。如果在需要擦写flash,因为是使用dma直接存取模块来按页擦写flash,并且是在ilm_ram模块中运行程序的,在这种情况下,cpu从wait模式下被唤醒两次,一次是dma burst pagewrite完成中断,另一次是接口发送完成中断;而后进入stop模式。这样的系统架构设计能够使得esim卡的指令交互过程中到达最低功耗状态。

[0122]

在本设计系统架构下,芯片的7816接口ip可以提供255字节的接收发送缓冲区。swp接口ip从硬件层支持shdlc协议,固件接收到的数据是剥离shdlc协议层的原始上层数据包,可以提供128b的接收发送缓冲区,最大可以接收发送4个shdlc数据包。本系统设计的7816接口、swp接口上的接收发送缓冲区可以芯片内核的并行程度,接口发送响应数据包时,cpu进入wait模式,发送完毕后cpu进入stop模式。

[0123]

本实施例中,为减小芯片功耗,设计的pmu功耗管理模块很好地从系统层级上实现了芯片的低功耗管理,在电路结构上以门控时钟取代原始时钟。在ucaa及nvm擦写功耗较大模块工作时,会关闭其他不相关工作模块。在芯片stop模式下,将关闭cpu、dma直接存取模块、swp接口等数字模块,同时也逐级关闭osc_hf时钟、电压调节器、芯片传感器(电压调节器以及芯片传感器为系统基本功能,未在系统结构图中画出)等模拟模块。在芯片wait模式下,关闭cpu时钟、iso7816、swp接口,dma直接存取模块、eflash模块可以继续工作。

[0124]

pmu功耗控制模块实现系统的低功耗控制及管理,包括低功耗模式的进入及退出,低功耗唤醒源配置等,符合内部sfr总线接口时序。

[0125]

系统提供了多种低功耗控制模式,以满足多种场合对功耗的需求。具体如下:

[0126]

1、指令低功耗模式;cpu执行执行指令进入低功耗的模式,分为stop模式和wait模式;

[0127]

stop模式具体为:设置cup的stop指令,在stop模式下,除通信接口中由有外部时钟和内部osclf直接驱动的部分电路外,系统其它部分的时钟全部停止,模拟模块进入stop状态从而降低系统功耗;通信接口接收到数据/命令后,或接收到复位信号后,退出stop模式,系统时钟恢复为原来值;

[0128]

wait模式具体为:设置cpu的wait指令,cpu进入wait状态,这时cpu的时钟停止,以降低功耗,当中断发生时,cpu退出wait状态;

[0129]

2、ucaa低功耗模式;当applet要使用ucaa算法时,通过调用系统提供的ucaa apis函数来完成算法,在ucaa apis函数中设置寄存器,选择ucaa低功耗模式;在ucaa低功耗模式下,cpu启动ucaa运算模块后,系统其它部分的时钟将停止,以降低系统功耗;运算结束后,自动恢复系统时钟,退出低功耗状态;

[0130]

在ucaa低功耗模式下,当rsa算法开始运算后,clk时钟管理模块、eflash模块、des运算模块、sm1运算模块都将停止;

[0131]

3、nvm擦写低功耗模式;当applet要使用擦写flash时,通过调用系统提供的writeflash apis函数来完成,writeflash apis函数根据实际的擦或写或搬移功能设置寄存器,此时的目标地址是flash中的地址,配置完dma的寄存器,并重映射使能寄存器完成中断之后,此writeflash apis立即返回,无需等待;选择nvm擦写低功耗模式;在nvm擦写低功耗模式下,cpu启动flash erase或program后,系统其它部分的时钟将停止,以降低系统功

耗;erase/program结束后,自动恢复系统时钟,退出低功耗状态;

[0132]

在nvm擦写低功耗模式下,当flash erase/program期间,clk时钟管理模块、ucaa运算模块、des运算模块、sm1运算模块都将停止。

[0133]

系统支持多种唤醒方式及唤醒源软件配置。唤醒源为:1、gpio唤醒,支持全部的gpio(gpio0

‑‑

gpio10);2、定时唤醒;3、接口唤醒(7816接口、swp接口、iic接口、spi接口、uart接口);4、中断唤醒。

[0134]

在本发明的系统中,stop低功耗是芯片功耗最低的状态。在stop状态下,osc_hf时钟、电压调节器、芯片传感器等模拟模块全部处于stop低功耗状态,ram、数字电路时钟全部关闭。stop状态的进入和退出采用逐级控制策略,减少电流变化对电压调节器的影响。进入stop过程要逐级关断电路,退出stop过程要逐级开启电路。

[0135]

与现有芯片相比,本系统提供的低功耗控制时钟更多,因而整个芯片的功耗能够更低。

[0136]

本实施例中,由于本系统在ahb总线上挂载了dma控制器(即dma直接存取模块)及ilm_ram模块,因此可以大大提高数据并行处理的速度,可以使得esim卡具有高性能低功耗的特点。

[0137]

iram程序存放于iram中,不同于remap重映射程序执行,iram程序具有的逻辑地址在ilm_ram空间上,cpu可以直接访问并执行其中的程序;iram程序直接由编译器编译生成并存放于flash中;在实际的芯片使用中,可以在芯片上电后由管理程序或者用户程序将存放于flash中的某段iram程序搬移到iram中。

[0138]

在本发明中,将通信接口iso7816/swp isr,writeflash api,java_loop等重要的关键代码,在工程中通过修改链接文件,将这些apis设定成逻辑地址在ilm_ram空间上,物理地址在flash空间中的段中,即编译生成iram程序。

[0139]

系统主要使用的是7816接口和swp接口。支持硬件动态检测外部接口,即7816接口和swp接口的动态检测。7816接口检测结果会以7816复位中断方式通知软件,swp接口检测以接口检测中断方式通知软件。

[0140]

系统的java虚拟机,整个过程分为初始配置、应用激活及应用完成三个阶段。初始配置阶段主要由软件配置swp ip的参数并探测外部是否支持swp接口,以决定是否使能swp接口。初始配置完成后,进入应用激活阶段。由于芯片内各ip支持中断,因此软件可基于接口中断来实现应用,从而可实现对多接口应用的并行处理。

[0141]

初始化设置sys_jobcnt为0,当在7816_isr或者swp_isr中接收到apdu指令时sys_jobcnt会增加1,在java_loop中会将sys_jobcnt减少1。当sys_jobcnt非0时,接着进行apdu指令解析,使用sys_jobcnt来控制虚拟机的处理流程,使得7816接口与swp接口可以并行工作,从而不需要rtos,能够更好的降低系统功耗。

[0142]

初始化设置sys_waitingcnt为0,当applet调用7816接口发送api时sys_waitingcnt会增加1,在7816_isr中当是发送完成时sys_waitingcnt减少1。如果系统使用swp接口,当applet调用swp发送api时sys_waitingcnt会增加1,在swp_isr中当是发送完成时sys_waitingcnt减少1。在java_loop中会根据sys_waitingcnt是否是0,进入wait模式或stop模式。当applet调用writeflash apis时sys_waitingcnt会增加1,在dma_isr中当是发送完成时sys_waitingcnt减少1。

[0143]

系统的java_loop虚拟机的工作流程为:

[0144]

s1、系统上电后,cpu执行环境初始化,使用dma直接存取模块的搬移功能,从flash中将7816接口、swp接口和isr接口、writeflash api、java_loop拷贝到ilm_ram模块上,得到系统中可以用于remap的起始地址:0x00a01000;

[0145]

s2、系统java虚拟机初始化;

[0146]

s3、根据接口硬件检测结果,对7816接口和swp接口做寄存器配置,使能寄存器相应的接口中断;设置sys_waitingcnt,设置sys_jobcnt为0;从步骤s4开始进入虚拟机主循环java_loop api,它是iram程序;

[0147]

s4、若sys_waitingcnt不等于0,则调用汇编指令使得系统进入wait模式,重复步骤s4,直到被中断唤醒;若sys_waitingcnt等于0,则进入步骤s5;

[0148]

s5、调用汇编指令使得系统进入最低功耗stop模式;

[0149]

s6、系统接收到apdu指令,退出stop模式,若当前激活接口是7816接口,则设置apdu数据缓冲区指针到7816接口的数据缓冲区;若当前激活接口是swp接口,则设置apdu数据缓冲区指针到swp接口的数据缓冲区;sys_jobcnt减少1;

[0150]

s7、java虚拟机检查apdu指令,若当前指令不是manage channe命令或select命令,则进入步骤s9;若当前指令是manage channel命令,则java虚拟机进行相应的处理,写返回数据到apdu数据缓冲区中,之后进入步骤s10;若当前指令是select命令,则进入步骤s8;

[0151]

s8、由open选定当前目标应用之后,对该应用的process方法执行mmu存储器管理模块的remap操作,即从该应用的process方法对应的flash地址处将其对应的process方法表单字节码对应到的flash页面地址,借助dma直接存取模块的搬移功能,拷贝到ilm_ram模块的空间上,获取该方法的表单字节数remapsize并对齐到整k字节数,若remapsize大于12kb,则设定remapsize等于12kb,重映射原地址寄存器的源地址为表单flash整k字节数地址处,重映射目标地址寄存器的目标地址为0x00a01000,重映射长度寄存器的长度为remapsize,使能寄存器执行重映射功能,此时借助dma直接存取模块与cpu并行执行的特点,将remap的flash内容拷贝到ilm_ram模块上,最大12kb;java虚拟机写返回数据到apdu数据缓冲区中,之后进入步骤s10;

[0152]

s9、java虚拟机调用当前被选定的应用,对apdu指令进行解析,由于重映射了12kb的process方法操作所对应的字节码到ilm_ram模块上,所以能够提高java解析apdu指令的执行效能;若applet的process需要写flash,通过调用系统wrtflash api来将512b的数据写回flash,借助dma burstwrite功能将数据写入到目标flash地址处,在wrtflash api设置sys_waitingcnt增加1,dma直接存取模块完成中断,在该中断服务程序中将会设置sys_waitingcnt减少1次;写返回数据到apdu数据缓冲区中,之后进入步骤s10;

[0153]

s10、对当前接口,调用系统发送api将apdu数据缓冲区的数据发送给主机,在发送api中设置sys_waitingcnt增加1,并使dma直接存取模块发送完成中断,在该中断服务程序中将会设置sys_waitingcnt减少1;

[0154]

s11、如果sys_jobcnt不等于0,则返回步骤s6;否则返回步骤s4。

[0155]

通过采用本发明公开的上述技术方案,得到了如下有益的效果:

[0156]

本发明提供了一种高性能低功耗的esim卡芯片系统,系统在ahb总线上挂载了dma

直接存取模块,使得程序的执行可以最大程度的并行化,从而大大的提高java卡的执行效能,减少了芯片工作时间,从而降低esim芯片整体功耗。系统在sys_ahb总线上挂载了ilm_ram模块并与cpu通过i_ahb总线相连,在使用中将需要提速的代码放在ilm_ram模块执行可以最大程度的并行化,从而大大的提高java卡的执行效能,减少了芯片工作时间,降低esim芯片整体功耗。系统将7816接口中断服务程序、swp接口中断服务程序、dma中断服务程序,writeflash api等关键功能固件代码定义成逻辑在ilm_ram模块上的,物理在flash上的,在ilm_ram模块中执行的程序,以提高整个芯片指令处理性能。系统在主机端下发apdu select指令,java卡虚拟机接收并解析到要选择一个不同的新的applet时,java卡虚拟机进一步处理取得选定applet的procees方法表单对应得flash页面地址及其表单的字节数大小,将对这段的flash内容进行mmu remap,这样重映射设计是动态的,即切换applet时,就会为新的applet做mmu remap操作,为关键代码做提速处理,从而提高java卡虚拟机的效能。系统使用dma的搬移功能来写flash页面,这实现并行化处理指令,提高芯片执行性能;writeflash api是ilm_ram程序,applet的的procees方法也在ilm_ram模块中运行,因此在进行flash页面编程时同时可以正常运行procees方法,而在java卡应用中写flash页面是经常使用到的操作,因而可以极大的提高java卡的性能。系统对flash的编程操作,都是通过dma直接存取模块进行的,因而能够与cpu运行固件并行化处理。在本芯片里flash最小编程单位为一个word即4个字节,flash写入四个字节需时25微秒,本系统的flash页面512b编程时比市面上的主流esim芯片的flash页面512b编程时间要快上一倍,当java卡应用在使用本发明设计的dma burst读写功能,java卡应用的执行效能更高,由于flash的编程时间大大减少了,因而可以大大降低整个芯片功耗。一个当在flash页面在快要写满时,才需要使用dma burst写功能将flash页面擦除后重新写入数据,在这样的策略下,esim卡在flash上的功耗会大大降低。系统低功耗控制架构,基于接口收发数据包状态主动进入低功耗模式的;接口ip的收发缓冲区使得,cpu处于wait模式下,接口自动发送数据包给主机,从而将接口上的cpu处理时间减少到最少,从而降低esim芯片整体功耗。swp接口在硬件层面上支持shdlc协议的通信控制,接收到数据包是hci层的数据,无需程序花费很多指令去进行shdlc组包以及shdlc通信协议控制。

[0157]

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。