1.本发明涉及语音信号处理领域,具体涉及一种采用嵌入式硬件运行神经网络的语音增强方法。

背景技术:

2.语音增强技术指当纯净目标语音信号在复杂环境中被一种或多种噪声干扰甚至淹没后,通过一定的降噪算法抑制和降低噪声的影响,尽可能地将纯净目标语音提取出来的技术。其被广泛应用于移动通信、人机交互、军事通信等领域,用于消除和减弱各种噪声带来的负面影响。

3.随着物联网技术的发展,语音处理设备朝着智能化、终端化的方向快速发展,语音增强技术被大量应用于硬件平台。但是,物联网技术中的云计算模型,由于大量使用网络带宽,且不能实时反馈的原因,不适用与终端设备。为补充云计算的劣势,边缘计算模式应运而生。

4.边缘计算选择将运算任务分散到靠近数据源的轻量级设备中,在本地对部分数据直接进行采集和运算,实时反馈给用户。而随着半导体制造业工艺水平的提升,fpga(field programmable gate array,fpga)这类半定制集成电路芯片,以及片上系统soc(system on chip,soc)fpga,为边缘计算提供了应用场景。虽然此类嵌入式设备具有本地采集、本地计算的优势,但其传输带宽、存储资源和计算资源的限制也阻碍了其大规模应用的发展。

5.而现有语音增强算法,通常基于机器学习技术,例如生成对抗网络(generative adversarial networks,gan)、自编码器结构的gan和长短记忆(long short-term memory,lstm)等网络模型。这些算法大部分都采用了结构各异且层数较深的神经网络模型,用较高的计算代价换取了部分性能的提升,导致这些复杂的神经网络,难以在资源有限的硬件平台实现。

技术实现要素:

6.针对现有技术中的上述不足,本发明提供的一种采用嵌入式硬件运行神经网络的语音增强方法解决了目前基于神经网络的语音增强系统难以在资源有限的嵌入式硬件平台上实现的问题。

7.为了达到上述发明目的,本发明采用的技术方案为:

8.一种采用嵌入式硬件运行神经网络的语音增强方法,包括以下步骤:

9.s1、通过语音传感器采集语音数据,并通过fpga对语音数据进行傅里叶变换,得到语谱图数据;

10.s2、采用fpga的逻辑单元构建r-ced神经网络,得到r-ced神经网络数字逻辑子系统;

11.s3、通过r-ced神经网络数字逻辑子系统对语谱图数据进行降噪;

12.s4、通过fpga对降噪后的语谱图数据进行时域还原,得到语音增强数据。

13.进一步地,所述步骤s1中,通过zynq7020型硬件平台fpga的可编程逻辑pl端对语音数据进行傅里叶变换;

14.所述步骤s2中,采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建r-ced神经网络;

15.所述步骤s4中,通过zynq7020型硬件平台fpga的处理器系统ps端对降噪后的语谱图数据进行时域还原。

16.进一步地,所述步骤s2包括以下分步骤:

17.s21、采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建神经网络卷积模块;

18.s22、通过神经网络卷积单元搭建r-ced神经网络数字逻辑子系统;

19.s23、采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建神经网络卷积参数存储模块;

20.s24、通过神经网络卷积参数存储模块储存r-ced神经网络数字逻辑子系统中各个卷积核模块的参数。

21.进一步地,所述步骤s21构建的神经网络卷积模块包括:移位寄存器、至少一个乘法组单元、卷积控制单元和累加单元;

22.所述移位寄存器用于通过移位操作,按fpga机器时钟周期,将输入谱图数据和神经网络卷积参数存储模块内存储的卷积运算权重参数搬移至卷积运算模块;

23.所述乘法组单元用于对输入谱图数据和卷积运算权重参数进行乘法运算,得到卷积运算结果;

24.所述卷积控制单元用于通过预设的卷积控制有限状态机对移位寄存器、乘法组单元和累加单元进行时序控制,以实现卷积运算;

25.所述累加单元用于对各个卷积控制单元的运算结果进行累加。

26.进一步地,所述r-ced神经网络数字逻辑子系统还包括输入谱图数据填充模块,用于采用full填充方式,在神经网络卷积模块对输入谱图数据进行卷积运算地过程中,进行padding填0操作。

27.本发明的有益效果为:

28.1)本发明基于嵌入式硬件平台,通过fpga构建实现神经网络,充分利用fpga数字逻辑门阵列的并行性,相对于基于gpu、cpu等处理器的神经网络运行方式,大大提高了处理速度,保障了语音增强处理的实时性。

29.2)使用了内置可编程逻辑pl端和处理器系统ps端的zynq7020型硬件平台fpga,充分利用可编程逻辑pl易于构建并行数据处理的数字逻辑模块和处理器系统ps易于执行复杂串行程序指令的差异性特点,分工执行神经网络降噪和频域信号转时域的操作。

30.3)针对的zynq7020型硬件平台fpga的特性,设计了r-ced神经网络的基础结构-神经网络卷积模块,将卷积的多循环式串行运算,转换为了数字逻辑电路特有的有限状态机控制的流水线式并行运算,有效提成了r-ced神经网络的处理速度。

附图说明

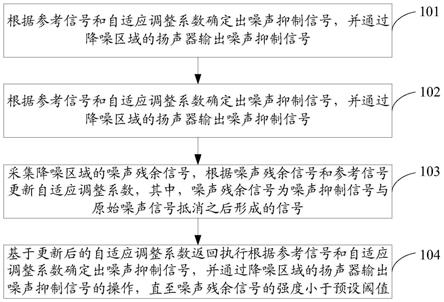

31.图1为本发明实施例提供的一种采用嵌入式硬件运行神经网络的语音增强方法的

流程图;

32.图2为本发明实施例zynq7020型硬件平台fpga结构示意图;

33.图3为神经网络卷积模块的软件程序实现方式示意图;

34.图4为本发明实施例提供的神经网络卷积模块的结构图;

35.图5为本发明实施例提供的移位寄存器的原理示意图;

36.图6为本发明实施例提供的累加单元的行累加结构图;

37.图7为本发明实施例提供的累加单元的列累加结构图;

38.图8为本发明实施例的层状态转换图;

39.图9为本发明实施例的操作状态转换图;

40.图10为本发明实施例的数据搬运状态转换图;

41.图11为本发明实施例的填充操作状态转换图;

42.图12为本发明实施例提供的神经网络卷积参数存储模块的原理示意图。

具体实施方式

43.下面对本发明的具体实施方式进行描述,以便于本技术领域的技术人员理解本发明,但应该清楚,本发明不限于具体实施方式的范围,对本技术领域的普通技术人员来讲,只要各种变化在所附的权利要求限定和确定的本发明的精神和范围内,这些变化是显而易见的,一切利用本发明构思的发明创造均在保护之列。

44.如图1所示,在本发明的一个实施例中,一种采用嵌入式硬件运行神经网络的语音增强方法,包括以下步骤:

45.s1、通过zynq7020型硬件平台fpga的可编程逻辑pl端对语音数据进行傅里叶变换,得到语谱图数据。

46.s2、采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建r-ced神经网络,得到r-ced神经网络数字逻辑子系统。

47.本实施例zynq7020型硬件平台fpga的结构如图2所示,可编程逻辑pl端提供了可用硬件描述语言(例如verilog hdl)控制连接关系的逻辑门阵列,处理器系统ps端提供了可运行软件程序的arm处理器。图2中,虚线表示控制信号的流向,实线表示数据的流向。

48.r-ced神经网络数字逻辑子系统的核心是fpga实现的卷积cnn。本实施例的步骤s2包括以下分步骤:

49.s21、采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建神经网络卷积模块。

50.通常,神经网络卷积模块由软件程序实现,其程序如图3所示,卷积运算可视为乘法的累加,运算包括了输出特征图通道循环、输入特征图通道循环、输入特征图循环和卷积核循环。

51.本发明的核心思想是用硬件化的数字逻辑门电路实现卷积运算的并行化处理,达到其硬件加速的效果。

52.根据并行化分析结果,卷积运算中,各层运算之间串行,单层运算并行,因此加速设计针对单层运算进行。

53.表1 各个神经网络卷积模块参数

[0054][0055]

如图3中的伪代码所示,单层运算中包含四个嵌套的循环,针对其不同特点,采用不同的展开策略,以加速卷积运算:

[0056]

卷积核循环:全部展开,用寄存器存储单个卷积核运算所需的全部特征图数据和卷积核数据;各个神经网络卷积模块参数如表1所示。

[0057]

输入特征图循环:不展开,由于系统中卷积运算的数据来源于fpga片内的ram,因此无法同时输入多个地址获得卷积核在滑动过程中对应的多个不同卷积窗口的特征图数据;

[0058]

输入特征图通道循环:部分展开,将特征图和权重按照通道划分为4个运算通道,在运算通道内,输入特征图的读取和运算是串行的,而在运算通道间是并行的;

[0059]

输出特征图通道循环:部分展开,将权重按照输出特征图通道划分为4个部分,综合按照输入特征图通道循环展开的方式,每个部分都包含4个运算通道,共有16个运算通道。

[0060]

如图4所示,本实施例构建的神经网络卷积模块包括:移位寄存器、至少一个乘法组单元、卷积控制单元和累加单元。

[0061]

移位寄存器用于通过移位操作,按fpga机器时钟周期,将输入谱图数据和神经网络卷积参数存储模块内存储的卷积运算权重参数搬移至卷积运算模块。其工作原理如图5所示。

[0062]

若所有卷积层最大窗口为i

×

j,则移位寄存器个数为j-1,深度为i,权重输入为单个寄存器。移位寄存器无需存满i

×

j个数据,在i

×

(j-1) 1时即可开始向reg寄存器中搬运数据。图5以最大卷积窗口5

×

5,当前卷积窗口4

×

4,权重数据0-15为例。虚线框内为当前卷积窗口所占用位置,如箭头所示,将权重数据存入单个寄存器,每个时钟移位寄存器将有右侧地址数据向左搬运。左侧地址不仅输出数据,且存入上一个移位寄存器的指定地址中。

[0063]

移位寄存器每个时钟输出数据到reg寄存器中,reg寄存器内部每个时钟按箭头方向对数据搬移,指导在有效位置获得卷积窗口的所有权重数据集。

[0064]

乘法组单元用于对输入谱图数据和卷积运算权重参数进行乘法运算,得到卷积运算结果。

[0065]

本实施例的乘法组单元采用流水线设计,每个时钟都会输出卷积窗口里全部元素的乘积结果。

[0066]

累加单元用于对各个卷积控制单元的运算结果进行累加。针对硬件特点,将累加过程分为多级累加的加法器树结构,每级运算的中间结果用寄存器缓存,形成流水线结构。

[0067]

本实施例的累加单元包括add_col(行累加)和add_row(列累加)两部分,如图6和图7所示。add_col模块将并行同步输入的4路数据对应累加后输出,采用流水线处理计算,无需额外参数配置。add_row模块累加数据为串行输入,第一帧数据用ram缓存。累加中,按地址将ram中前一次累加的结果读出,并在相加后写入原地址。完成最后一帧累加后,加上bias偏移值。数据输入完成后,得到一帧输出特征图,送入后级模块。

[0068]

卷积控制单元用于通过预设的卷积控制有限状态机对移位寄存器、乘法组单元和累加单元进行时序控制,以实现卷积运算。

[0069]

卷积控制单元包含两类输入:总控制器指令ctrl_cmd和输入标志信号flag_in。输出包括三类:参数配置信号config,输出标志信号flag_out和读数据信号rd。

[0070]

卷积控制状态机包含三个嵌套的状态机,最外层为层状态,其次是操作状态,最内层为数据搬运状态。各个状态机及状态说明如表2所示。

[0071]

层状态按卷积层划分,在进入第0层运算前完成信号初始化,添加准备状态idle。层状态机转换图如图8所示。

[0072]

idle状态内完成卷积运算相关信号初始化,layer0-layer15状态内完成第0层到第15层的卷积运算。

[0073]

表2卷积控制状态机的组成及说明

[0074][0075]

根据conv_ctrl模块的输出标志信号,up_fm、up_w、get_fm,ps可以判断何时向卷积运算模块输入权重数据和特征图数据,以及何时从卷积模块输出缓存内读取数据。

[0076]

操作状态如图9所示。在config状态内,主要完成对相关模块的参数配置。

[0077]

cal状态内,确定读取权重核特征图数据的实际,以及记录已完成运算的卷积核个数。

[0078]

dm状态内,产生数据更新的标志信号,以及记录已经运算完成的卷积核个数。

[0079]

数据搬运状态如图10所示。

[0080]

数据搬运状态为层状态dm中的子状态。根据不同的数据搬运需求分别为:等待状态wait、搬运特征图状态move_m、搬运权重和特征图状态move_mw、搬运下一次数据状态move_next。

[0081]

s22、通过神经网络卷积单元搭建r-ced神经网络数字逻辑子系统。

[0082]

r-ced神经网络数字逻辑子系统还包括输入谱图数据填充模块,用于采用full填充方式,在神经网络卷积模块对输入谱图数据进行卷积运算地过程中,进行padding填0操作。

[0083]

填充模块执行三个步骤:

[0084]

a1、在原始特征图写入outputram前,先向其预留的空间内写入对应个数的0;

[0085]

a2、原始特征图写入期间,在每行数据写入完成后,再写入对应个数的0;

[0086]

a3、一张特征图写入完成后,继续写入对应个数的0。、

[0087]

填充模块的控制采用了填充操作状态机,其转换图如图11所示。

[0088]

填充操作状态机包含五个状态:idle、up_row、map_row、pad0、down_row。各个状态的具体含义如表3所示。

[0089]

表3 填充操作状态机的组成及说明

[0090][0091]

s23、采用zynq7020型硬件平台fpga的可编程逻辑pl端内的逻辑单元构建神经网络卷积参数存储模块。

[0092]

s24、通过神经网络卷积参数存储模块储存r-ced神经网络数字逻辑子系统中各个卷积核模块的参数。

[0093]

本实施例中,神经网络卷积参数存储模块的设计如图12所示。对于14通道的卷积层而言fm_kk(k=0,1,2,3,

…

)和w_cc(c=0,1,2,3,

…

)分别表示第k,c通道的特征图和权重数据,由于4个ram共有16个通道,因此多余通道填0;

[0094]

图中convx1_x2(x1,x2=0,1,2,3)表示该卷积模块的输入来自第x1个权重ram的x2个通道和第x2个输入特征图ram,因此一共有16个卷积运算模块同时工作;各卷积层输入特征图缓存及搬运方案如表4所示。

[0095]

表4 神经网络卷积参数存储模块存储的各卷积模块输入特征图缓存及搬运方案

[0096][0097]

s3、通过r-ced神经网络数字逻辑子系统对语谱图数据进行降噪。

[0098]

s4、通过zynq7020型硬件平台fpga的处理器系统ps端对降噪后的语谱图数据进行时域还原,得到语音增强数据。

[0099]

综上,本发明具有如下的有益效果:

[0100]

1)本发明基于嵌入式硬件平台,通过fpga构建实现神经网络,充分利用fpga数字逻辑门阵列的并行性,相对于基于gpu、cpu等处理器的神经网络运行方式,大大提高了处理速度,保障了语音增强处理的实时性。

[0101]

2)使用了内置可编程逻辑pl端和处理器系统ps端的zynq7020型硬件平台fpga,充分利用可编程逻辑pl易于构建并行数据处理的数字逻辑模块和处理器系统ps易于执行复杂串行程序指令的差异性特点,分工执行神经网络降噪和频域信号转时域的操作。

[0102]

3)针对的zynq7020型硬件平台fpga的特性,设计了r-ced神经网络的基础结构-神经网络卷积模块,将卷积的多循环式串行运算,转换为了数字逻辑电路特有的有限状态机控制的流水线式并行运算,有效提成了r-ced神经网络的处理速度。

[0103]

本发明中应用了具体实施例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

[0104]

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。