1.本实用新型是有关于一种导电端子,尤指一种具良好抗电解腐蚀及抗化学腐蚀性能的导电端子。

背景技术:

2.现有电连接器,包含复数的导电端子,用以与另一电连接器的导电端子相抵接,达到讯号传递的目的。电连接器的导电端子,其表面电镀有金属镀层,其中包含多数贵重金属。该生产技术不仅生产成本昂贵,而且技术复杂。

3.此外,金属镀层的组成及结构,攸关抗电解腐蚀及抗化学腐蚀的能力,进一步影响导电端子的使用寿命。

技术实现要素:

4.有鉴于此,本实用新型提出一实施例之一种导电端子,适用于电连接器,导电端子具有对接段,对接段包括基材及多层电镀层。

5.多层电镀层配置在基材上,多层电镀层是由基材的表面依次配置,多层电镀层依次包括铜层、第一镍金属或第一镍合金层、第一金层、第二镍金属或第二镍合金层、第二金层、第一铂金属或第一铂合金层、第三金层、及第二铂金属或第二铂合金层。

6.优选地,多层电镀层还包括第四金层,配置在第二铂金属或第二铂合金层上。

7.优选地,铜层的厚度为10微英寸至80微英寸,第一镍金属或第一镍合金层的厚度为1微英寸至600微英寸,第一金层的厚度为1微英寸至40微英寸,第二镍金属或第二镍合金层的厚度为1微英寸至600微英寸,第二金层的厚度为1微英寸至40微英寸,第一铂金属或第一铂合金层的厚度为1微英寸至100微英寸,第三金层的厚度为1微英寸至40微英寸,第二铂金属或第二铂合金层的厚度为1微英寸至100微英寸。

8.优选地,第一镍合金层为镍磷合金层、镍钴合金层、镍钯合金层或镍锡合金层;第二镍合金层为镍磷合金层、镍钴合金层、镍钯合金层或镍锡合金层。

9.优选地,导电端子为下料式端子、折弯式端子、弹簧针端子(pogo pin)或冠簧端子(crown spring terminal)。

10.优选地,导电端子的基材的材质为铜或铜合金。

11.优选地,多层电镀层位于对接段的一部或全部。

12.本实用新型至少一实施例之导电端子,其对接段具有多层电镀层,具有良好的抗电解腐蚀及抗化学腐蚀能力,延长电连接器的使用寿命。制造本实用新型一实施例之导电端子,相较于先前技术,更降低了制造成本。

附图说明

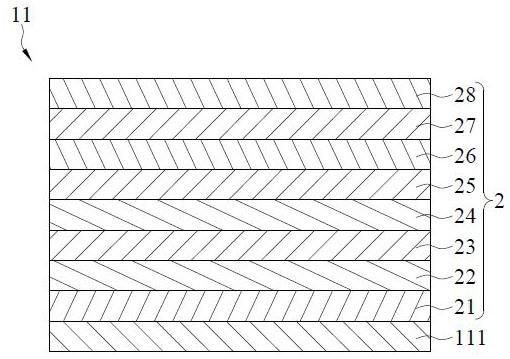

13.图1 绘示优选地导电端子的对接段中,基材及多层电镀层的结构示意图。

14.图2 绘示优选地导电端子的对接段中,基材及多层电镀层的结构示意图。

15.图3 绘示优选地导电端子的对接段中,基材及多层电镀层的结构示意图。

16.图4 绘示优选地导电端子的对接段中,基材及多层电镀层的结构示意图。

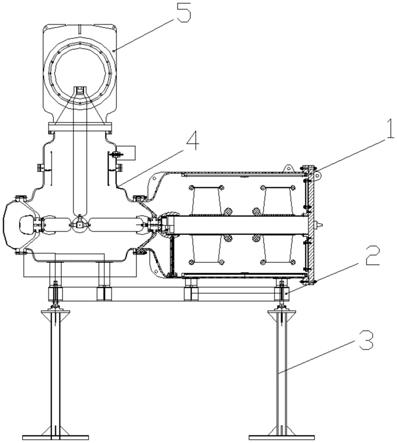

17.图5 绘示出优选地电连接器之截面示意图。

18.图6 绘示出优选地电连接器之截面示意图。

19.图7 绘示出优选地电连接器之截面示意图。

20.图8 绘示出优选地电连接器之截面示意图。

21.图9 系本实用新型优选地导电端子的制作方法之流程示意图。

22.图10 是本实用新型优选地导电端子的制作方法之流程示意图。

23.符号说明

24.100:电连接器

25.1:导电端子

26.11: 对接段

27.111:基材

28.2:多层电镀层

29.21:铜层

30.22:第一镍金属层

31.22’:第一镍合金层

32.23:第一金层

33.24:第二镍金属层

34.24’:第二镍合金层

35.25:第二金层

36.26:第一铂金属层

37.26’:第一铂合金层

38.27:第三金层

39.28:第二铂金属层

40.28’:第二铂合金层

41.29:第四金层

42.s1-s10:步骤。

具体实施方式

43.请参阅图1,绘示优选地导电端子1的对接段11中,基材111及多层电镀层2的结构示意图。本实用新型的导电端子1适用于电连接器100(见图5),导电端子1具有对接段11,对接段11包括基材111及多层电镀层2,其中导电端子1的对接段11用以与另一电连接器的导电端子电性抵接。本实用新型的导电端子1可应用于插头电连接器或插座电连接器(详见后述),本实用新型并无限制。优选地,导电端子1的基材111的材质为铜或铜合金。

44.多层电镀层2配置在基材111上,多层电镀层2是由基材111的表面依次配置,在图1所示的实例中,多层电镀层2共八层,依序为铜层21、第一镍金属层22、第一金层23、第二镍金属层24、第二金层25、第一铂金属层26、第三金层27及第二铂金属层28。经由:第一镍金属层22、第二镍金属层24、第一铂金属层26及第二铂金属层28的搭配,使导电端子1达到良好

的抗电解腐蚀及抗化学腐蚀能力。

45.在不同的电镀层之间电镀金层,例如图1之第一金层23、第二金层25以及第三金层27,是为使该等电镀层易于附着,各电镀层紧密附着防止多层电镀层2出现缝隙。

46.请参阅图2,绘示优选地导电端子1的对接段11中,基材111及多层电镀层2的结构示意图。依据图2所示的实施例,多层电镀层2共八层,依序为铜层21、第一镍合金层22’、第一金层23、第二镍合金层24’、第二金层25、第一铂合金层26’、第三金层27及第二铂合金层28’。以此设置,亦得使导电端子1达到良好的抗电解腐蚀及抗化学腐蚀能力。

47.然而,本实用新型并不以上述图1及图2所示实施例为限,使用者可从第二层中选择电镀镍合金或镍金属;从第四层中选择电镀镍合金或镍金属;从第六层中选择电镀铂金属或铂合金;从第八层选择电镀铂金属或铂合金,端视使用者所需的条件以及制程而定。

48.请参阅图3及图4,分别绘示优选地导电端子1的对接段11中,基材111及多层电镀层2的结构示意图。多层电镀层2还包括第四金层29,配置在第二铂金属上,以作为导电端子1的外观层,如图3所示。依据图4所示实施例,第四金层29是配置在第二铂合金层28’上。

49.优选地,铜层21的厚度为10微英寸至80微英寸,第一镍金属或第一镍合金层22,22’的厚度为1微英寸至600微英寸,第一金层23的厚度为1微英寸至40微英寸,第二镍金属或第二镍合金层24,24’的厚度为1微英寸至600微英寸,第二金层25的厚度为1微英寸至40微英寸,第一铂金属或第一铂合金层26,26’的厚度为1微英寸至100微英寸,第三金层27的厚度为1微英寸至40微英寸,第二铂金属或第二铂合金层28,28’的厚度为1微英寸至100微英寸。使用者依据其制程需求以及所需导电端子1抗电解腐蚀及抗化学腐蚀的能力,而选择各该电镀层的厚度。

50.优选地,第一镍合金层22’为镍磷合金层、镍钴合金层、镍钯合金层或镍锡合金层;第二镍合金层24’为镍磷合金层、镍钴合金层、镍钯合金层或镍锡合金层。换言之,本实用新型的第一镍合金层22’及第二镍合金层24’具有多种选择及组合,第一镍合金层22’与第二镍合金层24’并不一定为同一种镍合金。

51.优选地,导电端子1为下料式端子、折弯式端子、弹簧针端子(pogo pin)或冠簧端子(crown spring terminal)。

52.请参阅图5及图6,分别绘示出优选地电连接器100之截面示意图。电连接器100可以是但不限于usb type c。依据图5所示的实施例,电连接器100为usb type c的插头电连接器,导电端子1为折弯式端子。于此实施例中,多层电镀层2位于对接段11的全部。图6所示实施例之电连接器100与图5相同,其差异在于,图6所示实施例的多层电镀层2位于对接段11的一部,尤指与插座电连接器之导电端子1相抵接的部位。需特别说明的是,多层电镀层2是位于基材111的表面,图5及图6为特别示意对接段11及多层电镀层2的位置,因此在部分导电端子的截面上绘示有多层电镀层2。

53.请参阅图7及图8,分别绘示出优选地电连接器100之截面示意图。电连接器100为usb type c的插座电连接器,导电端子1为折弯式端子。于此实施例中,多层电镀层2位于对接段11的全部。图8所示实施例之电连接器100与图7相同,其差异在于,图8所示实施例的多层电镀层2位于对接段11的一部,尤指与插头电连接器之导电端子1相抵接的部位。

54.请参阅图9,为本实用新型优选地导电端子的制作方法之流程示意图。制作方法包含下列步骤:步骤s1:提供导电端子,导电端子具有对接段,对接段包括基材。步骤s2:于基

材上电镀铜层。步骤s3:于铜层上电镀第一镍金属或第一镍合金层。步骤s4:于第一镍金属或第一镍合金层上电镀第一金层。步骤s5:于第一金层上电镀第二镍金属或第二镍合金层。步骤s6:于第二镍金属或第二镍合金层上电镀第二金层。步骤s7:于第二金层上电镀第一铂金属或第一铂合金层。步骤s8:于第一铂金属或第一铂合金层上电镀第三金层。步骤s9:于第三金层上电镀第二铂金属或第二铂合金层。经由步骤s2至s9,完成在基材上配置多层电镀层。

55.请参阅图10,为本实用新型优选地导电端子的制作方法之流程示意图。依据该实施例,导电端子的制作方法进一步包含一步骤s10:在第二铂金属或第二铂合金层上电镀第四金层,以作为对接段的外观层。

56.本实用新型至少一实施例之导电端子,其对接段具有多层电镀层,具有良好的抗电解腐蚀及抗化学腐蚀能力,延长电连接器的使用寿命。制造本实用新型一实施例之导电端子,相较于先前技术,更降低了制造成本。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。