包括金属-绝缘体-金属型电容结构的集成电路和对应制造方法

1.优先权要求

2.本技术要求于2020年11月3日提交的法国专利申请号2011274的优先权权益,其内容在法律允许的最大范围内通过引用以其整体并入本文。

技术领域

3.实施例和实施方式涉及集成电路,并且具体地涉及集成电路的电容元件。

背景技术:

4.对电容元件的实施例的主要需求是每表面单位具有最高可能的电容值,被称为“表面容量”。

5.为了增加金属氧化物半导体(mos)类型的电容结构的表面容量,已经提出通过填充竖直地深入延伸到半导体衬底中的沟槽来形成导电电极。

6.增加沟槽的深度允许增加表面容量,但这种方法一方面受到与沟槽的深度成正比的沟槽蚀刻时间的限制,另一方面用于蚀刻深沟槽的工具不一定在给定的生产线中被提供,并且将该工具集成到生产线中可能会带来巨大的成本。

7.因此,期望根据不是很受限制并且与提供深度有限的蚀刻沟槽的集成电路生产链兼容的技术,来增加电容元件的表面容量。

技术实现要素:

8.根据一个方面,在这方面提供了一种集成电路,该集成电路包括半导体衬底、在衬底正面上方的导电层、第一金属层级中的第一金属轨道、位于导电层与第一金属层级之间的金属前电介质区域、以及位于金属前电介质区域的体积中的至少一个电容结构,该至少一个电容结构被称为金属-绝缘体-金属型电容结构。金属-绝缘体-金属类型的电容结构包括:第一金属层,被配置成与导电层电连接;第二金属层,被配置成与第一金属轨道电连接;以及电介质层,在第一金属层与第二金属层之间。

9.电容结构将是金属-绝缘体-金属(mim)类型,尽管通常由这些术语指定的电容元件常规地不位于金属前电介质区域处,而是位于互连的最后金属层级中,在互连的最后金属层级处,约束(特别地,约束是空间的)不同于金属前电介质区域中的约束。

10.因此,位于金属前电介质区域中的金属-绝缘体-金属类型的电容结构可能经历由形成在衬底上的其他元件确定的空间应力。然而,根据该方面的mim型电容结构可以有利地被设置在金属前电介质的自由空间中,但其下面的衬底表面由另一元件占据,例如,该另一元件诸如为如上所述的mos类型的电容元件,要不然诸如为位于衬底中或衬底上的电阻元件。

11.因此,电容结构的集成未实际占据衬底上的任何附加表面,因此允许受益于附加电容界面并且在总体尺寸方面是“自由的”。

12.根据一个实施例,导电层由多晶硅制成,并且包括金属硅化物的薄层,并且第一金属层包括与金属硅化物的薄层化学结合的扩散屏障层。

13.这允许确保导电层与每个金属-绝缘体-金属电容结构的第一金属层之间的良好电连接。

14.根据一个实施例,金属-绝缘体-金属类型的每个电容结构被设置在金属前电介质区域的体积中的沟槽中,第一金属层与沟槽的侧面和底部共形,电介质层与第一金属层的侧面和底部共形,第二金属层与电介质层的侧面和底部共形。

15.因此,电容结构的金属、绝缘体和金属的层被布置成以u字形彼此嵌套,并且在沟槽的长度上被布置,以便增加第一导电层与第二导电层之间的界面的尺寸,从而增加每个电容结构的电容值。

16.根据一个实施例,电介质界面将导电层和半导体衬底电绝缘,导电层和电介质界面被配置成与半导体衬底形成金属-氧化物-半导体类型的电容结构。

17.因此,导电层不仅用于电连接mim型电容结构的第一金属层,而且还用于形成mos型电容结构。因此,衬底上被占据的表面被用于两种类型的电容结构,从而利用相等的总体尺寸形成了更大电容值的电容元件。

18.根据一个实施例,导电层包括覆盖半导体衬底表面的水平部分,并且包括垂直于所述表面深入延伸到衬底中的至少一个竖直部分。

19.在表面容量方面,以及在导电层与mos电容结构的竖直和水平部分之间的电连接的总体尺寸方面,该实施例是有利的。

20.根据一个实施例,导电层的竖直部分具有结构,该结构类似于埋入式存取晶体管的竖直栅极的结构,该埋入式存取晶体管属于非易失性存储器的存储器单元。

21.换句话说,提出了将mos型电容结构的制造与(例如,电可擦除和可编程只读存储器(eeprom)类型的)非易失性存储器的制造协同集成,这特别是在成本方面是有利的。

22.根据一个实施例,导电层被配置成电连接到第一金属层级的第二金属轨道,并且半导体衬底被配置成电连接到第一金属层级的第三金属轨道,第二金属轨道和第三金属轨道能够彼此耦合或与第一金属轨道耦合。

23.因此,依赖于金属轨道的耦合,在集成电路的相同实施例中,可以仅使用mim型电容结构、仅使用mos型电容结构、要不然使用并联耦合的两个电容结构。

24.根据一个实施例,导电层位于电阻导电条上方,该电阻导电条属于具有两个端子的电阻元件,第一金属轨道、导电层和电阻元件的端子被耦合,以便与金属-绝缘体-金属类型的所述至少一个电容结构形成电阻-电容电路。

25.再次,mim型电容结构在用于在电阻条的位置处形成rc电路的总体尺寸方面是自由的。

26.根据另一方面,提供了一种集成电路制造方法,该方法包括:在半导体衬底的正面上方形成导电层;在导电层上方形成金属前电介质区域;在金属前电介质区域的体积中形成被称为金属-绝缘体-金属型电容结构的至少一个电容结构,包括:形成被配置成与导电层电连接的第一金属层,在第一金属层上形成电介质层,以及在电介质层上形成第二金属层;以及形成穿过金属前电介质区域的接触,并且在金属前电介质区域上方形成第一金属层级的金属轨道,接触被配置成将第二金属层与第一金属层级的第一金属轨道电连接。

27.根据一个实施方式,导电层由多晶硅形成,第一导电层的形成包括硅化,硅化在导电层上形成金属硅化物的薄层,并且第一金属层的形成包括扩散屏障层的形成,方法包括非氧化退火步骤,非氧化退火步骤能够在扩散屏障层与金属硅化物的薄层之间生成化学结合。

28.根据一个实施方式,金属-绝缘体-金属类型的每个电容结构的形成包括在金属前电介质区域的体积中蚀刻沟槽,第一金属层的形成包括与沟槽的侧面和底部共形的共形沉积,电介质层的形成包括与第一金属层的侧面和底部共形的共形沉积,并且第二金属层的形成包括与电介质层的侧面和底部共形的过量沉积以及每个沟槽的填充,之后是机械-化学平坦化(或化学-机械抛光(cmp)),机械-化学平坦化(或化学-机械抛光(cmp))去除沟槽外部的第二金属层的过量部分。

29.根据一个实施方式,导电层的形成包括电介质界面的形成,该电介质界面将导电层和半导体衬底电绝缘,并且导电层的形成被配置成使得导电层和电介质界面与半导体衬底形成金属-氧化物-半导体类型的电容结构。

30.根据一个实施方式,导电层的形成包括:蚀刻至少一个沟槽,该至少一个沟槽垂直于衬底的表面在衬底中延伸;利用导电材料填充所述至少一个沟槽,该导电材料从沟槽溢出到所述表面的一部分上方,以使导电层包括覆盖所述表面的水平部分,并且包括垂直于所述表面深入延伸到衬底中的至少一个竖直部分。

31.根据一个实施方式,蚀刻所述至少一个沟槽和填充所述至少一个沟槽的步骤与以下步骤同时被实行:用于制造非易失性存储器的存储器单元的方法的形成具有竖直栅极的埋入式存取晶体管的类似步骤。

32.根据一个实施方式,方法包括:形成被配置成将导电层与第一金属层级的第二金属轨道电连接的接触,以及形成被配置成将半导体衬底与第一金属层级的第三金属轨道电连接的接触,第二金属轨道和第三金属轨道能够彼此耦合或与第一金属轨道耦合。

33.根据一个实施方式,方法包括形成电阻导电条,电阻导电条旨在属于具有两个端子的电阻元件,在电阻导电条上方形成导电层,方法包括将第一金属轨道、导电层以及电阻元件的端子耦合,以便与金属-绝缘体-金属类型的所述至少一个电容结构形成电阻-电容电路。

附图说明

34.在检查实施例和实施方式以及附图的详细描述之后,本发明的其他优点和特征将变得明显,这些实施例和实施方式决不是限制性的,其中:

35.图1图示了包括金属-电介质-金属(mim)类型的电容结构的集成电路的一个示例;

36.图2至图9图示了制造方法中的步骤;

37.图10以透视图图示了通过上面关于图2至图9描述的类型的方法获得的结构;

38.图11图示了图10的结构的俯视图;

39.图12和图13分别图示了图10和图11所示的集成电路结构的备选方案的透视图和俯视图;

40.图14图示了关于图1描述的电容结构在制造电阻-电容rc电路的上下文中的应用。

具体实施方式

41.图1图示了集成电路的一个示例,该集成电路具体包括通常由硅制成的半导体衬底sub、金属-电介质-金属(mim)类型的电容结构和金属轨道pm1。

42.在下文中,“金属-电介质-金属类型的电容结构”可以直接通过参考附图标记mimcap来指定,也就是说由术语“电容结构mimcap”来指定。

43.线路前段(feol)半导体部分包括半导体衬底sub和从衬底的正面fa在衬底中和衬底上生产的半导体部件,诸如晶体管、二极管或mos型电容元件。衬底的正面fa通常限定水平平面,并且竖直通常被定向成:“底部”朝向衬底sub的体积,并且“顶部”朝向正面fa的外部,部件形成在正面fa处。

44.线路后段(beol)互连部分包括金属层级m1的堆叠。每个金属层级包括:跟踪互连的路径的金属轨道pm1、接触相邻金属层级的金属轨道的通孔、以及将金属轨道与相邻金属层级电绝缘的金属间电介质层dim1、ca1。最后的互连层级通常旨在用于封装集成电路封装体。

45.位于半导体部分feol与互连部分beol之间的线路中段(meol)部分包括电介质区域dpm,电介质区域dpm通常被称为金属前电介质,用于将在半导体部分feol中形成的结构与互连部分beol的第一金属层级m1电分离和电绝缘。通常,金属接触竖直穿过金属前电介质层dpm,以将半导体部分feol的部件与第一金属层级m1的金属轨道连接。

46.例如,金属前电介质层dpm由磷硅玻璃或可选地由二氧化硅制成。属于金属前电介质区域dpm的停止层ca可以被提供在半导体部分feol处,以停止接触形成的蚀刻。

47.电容结构mimcap位于部分meol中,在金属前电介质区域dpm的体积中。

48.电容结构mimcap包括第一金属层cm1、电介质层cd和第二金属层cm2的叠加。

49.每个电容结构mimcap的第一金属层cm1与属于半导体部分feol的导电层ps电连接。在该示例中,导电层ps位于半导体衬底sub的正面fa上。

50.每个电容结构mimcap的第二金属层cm2经由接触cnt1与第一金属轨道pm1电连接。

51.特别地,位于每个电容结构mimcap的第一金属层cm1与第二金属层cm2之间的电介质层cd的厚度,允许设置电容结构mimcap的电容值。

52.如下面关于图2至图9或图10至图13将出现的,在金属前电介质区域dpm的体积中开设沟槽(trdpm)以容纳电容结构mimcap。沟槽具有形状,该形状在宽度上窄(在图1的视图中水平地)、在长度上细长(垂直于图1的视图),并且沟槽具有深度(在图1的视图中垂直地),该深度旨在允许在电容结构mimcap的顶部与第一金属层级m1之间形成接触cnt1。

53.沟槽被形成为具有最大可能的密度。在这方面,两个沟槽之间的横向空间也可以做得尽可能小。

54.因此,电容结构mimcap被布置成横向间隔开并且纵向延伸的平行条,其底部与导电层ps接触,并且被包围在金属前电介质区域dpm的体积中。

55.例如,第一金属层cm1由氮化钛tin的薄层形成,或者可选地由钛ti的薄层和氮化钛tin的薄层的叠加形成(应当注意,严格来说,氮化钛是一种陶瓷,但在半导体和微电子行业中通常被认为是一种金属化合物)。

56.例如,电介质层cd由金属氧化物形成,有利地因其高介电常数(与二氧化硅的参考介电常数相比)而被选择,例如,该金属氧化物诸如为氧化钽ta2o5或者其他金属或硅氧化物

或氮化物。

57.例如,第二金属层cm2由钛ti的薄层和氮化钛tin的薄层的叠加(或可选地单独由氮化钛tin的薄层)和由金属(诸如钨w)制成的主体形成。

58.例如,导电层ps由多晶硅形成,并且有利地在与电容结构mimcap的第一金属层cm1电接触的上表面上,包括金属硅化物sim(例如,硅化钴cosi2)的薄层。

59.例如,接触cnt1包括扩散屏障薄层和金属主体的叠加。薄扩散屏障层例如由钛ti和氮化钛tin制成,并且该主体由钨w制成。

60.事实上,上面针对第一金属层cm1和第二金属层cm2给出的示例对应于金属接触cnt1的薄扩散屏障层的使用,薄扩散屏障层通常旨在限制金属从接触向半导体部分feol的材料的扩散,同时是导电的。

61.然而,薄扩散屏障层有利地允许将第一金属层cm1与导电多晶硅层ps的金属硅化物sim的薄层化学结合。化学结合由退火阶段产生,并且允许更好的电连接。

62.因此,扩散屏障材料的使用允许改善电容结构mimcap的第一金属层cm1与导电层ps的电连接,并且实现稳定和受控的电容效应。

63.特别地,在薄扩散屏障层的沉积之后的退火阶段引起金属硅化物的硅与薄扩散屏障层的材料(例如钛)之间的合金反应。这种反应不仅改善了薄扩散屏障层与多晶硅之间的通路电阻,而且改善了这种电接触的可靠性。

64.如此生产的结构在接触处具有缺陷的风险较小,并且因此常规地将电容结构mimcap的第一金属层cm1连接到特定的金属线是不需要的。第一金属层cm1实际上直接连接到多晶硅ps的导电层。

65.总之,这允许在不恶化可靠性的情况下,简化各种元件的布置和制造,特别是为了优化电容结构的密度。

66.导电层ps转而可以例如以与mos晶体管的栅极或mos电容元件的电极相同的方式来制成,并且在这种情况下,包括将导电层ps与半导体衬底sub电绝缘的电介质界面ox。

67.事实上,导电层ps和电介质界面ox可以有利地被具体配置成:与半导体衬底sub形成金属-氧化物-半导体moscap类型的电容结构。

68.在下文中,“金属-氧化物-半导体类型的电容结构”可以直接通过参考附图标记“moscap”来被指定,也就是说通过术语“电容结构moscap”来被指定。

69.图2至图9图示了用于制造关于图1描述的电容结构mimcap的示例性方法的步骤的结果。图1和图2至图9共同的元件具有相同的附图标记,并且将不会关于每个附图全都详述。

70.图2图示了在制造包括mos型电容结构moscap的集成电路的示例中,半导体部分feol和金属前电介质区域dpm的制造步骤的结果。

71.电容结构moscap的制造包括在半导体部分feol中、在衬底sub上形成导电层p0,因此,导电层p0被配置成与半导体衬底sub形成被称为金属-氧化物-半导体电容结构moscap的电容结构。

72.例如如图1中所示,电容结构moscap可以是平面的,但是图2至图9的示例有利地对应于如下电容结构moscap,其中导电层p0包括覆盖衬底sub的正面fa的水平部分h,并且包括垂直于所述正面fa深入延伸到衬底sub中的至少一个竖直部分v。

73.在这方面,导电层p0的形成包括:垂直于正面fa蚀刻在衬底sub中延伸的沟槽trsub,在正面fa上以及在衬底sub的蚀刻沟槽trsub的侧面和底部上形成电介质界面ox。因此,电介质界面ox将允许将导电层p0与半导体衬底sub之间的电容界面电绝缘。然后利用导电材料p0,例如多晶硅,来填充沟槽trsub,导电材料p0从沟槽trsub溢出到所述表面fa的一部分上方。然后,特别地,通过光刻掩模来蚀刻导电材料p0,以使导电层p0包括被界定在正面fa上的水平部分h,并且包括在沟槽trsub中的竖直部分v。

74.水平部分h和竖直部分v因此有利地属于单个单片结构,也就是说由单一材料的块制成。备选地,水平部分h和竖直部分v可以单独形成,然后被电连接,从而在沟槽trsub中包括与形成导电层p0并且覆盖沟槽的导电材料分离的导电材料。

75.此外,蚀刻所述至少一个沟槽trsub和填充所述至少一个沟槽trsub的步骤,可以有利地与用于制造非易失性存储器的存储器单元的方法的形成具有竖直栅极的埋入式存取晶体管的类似步骤同时被实行。

76.事实上,电容结构moscap的制造可以与在半导体衬底的存储器区域中蚀刻类似结构的沟槽的步骤,并且与利用竖直栅极的类似性质的导电材料来填充所蚀刻的沟槽的步骤同时被实施,该竖直栅极属于非易失性存储器单元的埋入式存取晶体管。存储器单元通常还包括与存取晶体管串联耦合的浮栅状态晶体管。

77.多晶硅的导电层p0的硅化允许在导电层p0的上表面上形成金属硅化物sim的薄层。

78.然后,金属前电介质区域dpm形成在导电层p0和衬底sub的正面fa上方。金属前电介质区域dpm的形成提供了:形成例如由氮化硅制成的停止层ca,并且形成例如由磷硅玻璃或二氧化硅制成的金属前电介质体积本身。金属前电介质区域dpm的上部通过机械-化学平坦化进行平整。

79.在该阶段,用于制造电容结构moscap的原始方法(其中电容结构mimcap的制造被内接)将提供穿过金属前电介质区域dpm的金属接触的形成。

80.图3图示了用于电容结构mimcap的形成的金属前电介质层dpm中的蚀刻步骤的结果。

81.在金属前电介质区域dpm上使用掩模msk,掩模msk具有包括通过光刻获得的开口ouv的蚀刻图案。开口ouv具有在长度上细长(垂直于图3的视图)的形状,并且被平行设置,在宽度方向上(在图3的视图中水平地)间隔开。

82.借助于各向异性干法蚀刻,例如反应离子轰击蚀刻(例如,反应离子蚀刻(rie)),在金属前电介质区域dpm的体积中开设沟槽trdpm。rie蚀刻最初被配置成:选择性地蚀刻例如由氧化硅制成的金属前电介质材料dpm,并且被位于导电层p0上的停止层ca的材料停止,停止层ca例如由氮化硅制成。其次,rie刻蚀被配置成:选择性地刻蚀停止层ca,以便露出在沟槽trdpm的底部处的导电层p0的硅化表面sim,而不刻蚀或很少刻蚀例如由氧化硅制成的金属前电介质材料dpm。

83.因此,在金属前电介质部分dpm的体积中开设的沟槽trdpm将容纳电容结构mimcap。

84.在该示例中,在金属前电介质部分dpm中开设的沟槽trdpm与导电层p0的竖直部分v对准。尽管如此,沟槽trdpm可以被交错设置在导电层p0的每个竖直部分v之间,或者与导

电层p0的竖直部分v的位置没有任何特定关系。

85.图4图示了在选择性地去除掩模msk之后,形成电容结构mimcap的金属层、绝缘层和金属层的叠加的步骤的结果。

86.首先以共形方式沉积第一金属层cm1,也就是说,以基本恒定的厚度与其放置在其上的结构的轮廓共形,也就是说,在金属前电介质dpm的顶部上、在沟槽trdpm的侧面和沟槽trdpm的底部上沉积第一金属层cm1。

87.因此,第一金属层cm1与导电层p0的金属硅化物sim的薄层接触。

88.第一金属层cm1包括例如氮化钛的至少一个薄层,可选地还包括钛的薄层。

89.第一金属层cm1的形成例如通过物理气相沉积(pvd)或通过化学气相沉积(cvd)(包括其变型,例如利用等离子体辅助(pecvd)、在低压处(lpcvd))或通过原子层沉积(ald)等来进行。

90.第一金属层cm1有利地通过与通常向金属接触提供的扩散屏障层的形成类似的步骤来形成。

91.电介质层cd以共形方式被沉积在第一金属层cm1上,并且特别地与位于沟槽trdpm中的第一金属层cm1的侧面和底部共形。

92.电介质层cd包括例如氧化钽或另一种电介质材料,诸如金属或硅氧化物或氮化物。

93.电介质层cd的形成例如通过pvd或cvd来实行。

94.第二金属层cm2被沉积,以便过量地装填沟槽trdpm内剩余的自由体积。因此,第二金属层cm2通过电介质层cd与第一金属层cm1电分离。

95.有利地,第二金属层cm2的形成包括沉积钛的薄层和氮化钛的薄层,或者可选地仅沉积氮化钛的薄层,然后利用例如钨的金属过量地填充沟槽trdpm内剩余的自由体积。

96.出于附图的可读性的原因,图4至图9中未示出钛的薄层和氮化钛的薄层的细节。

97.形成第二金属层cm2的成分例如通过pvd或cvd来实行。

98.第二金属层cm2的所有成分可以有利地通过与提供扩散屏障层的金属接触形成类似的步骤来形成。

99.实际上,如前面关于图2所提到的以及如将在下面关于图7和图8出现的,电容结构mimcap的制造在形成金属接触时被内接在集成电路制造方法中。因此,利用与用于形成金属接触的技术类似或甚至相同的技术来提供第一金属层cm1和第二金属层cm2的形成,一方面允许使用已知和掌握的技术,另一方面允许不大幅修改集成电路生产链的过程。实际上,在这种情况下,附加电容结构mimcap的形成可以使用与用于制造金属接触的常规方法中使用的那些工具和反应器相同的工具和反应器。

100.图5图示了从位于金属前电介质dpm顶部上的第二金属层cm2、电介质层cd和第一金属层cm1去除过量部分的机械-化学平坦化步骤的结果。此外,机械-化学平坦化被配置成:从金属前电介质区域dpm的上部和金属前电介质区域dpm的体积中的电容结构mimcap的上部去除显著厚度epol。

101.图6图示了沉积与通过机械-化学平坦化去除的厚度epol基本相等的电介质材料dpm的厚度edep的结果,以返回到金属前电介质区域dpm的原始厚度,也就是说,具有与关于图2获得的金属前电介质区域基本相同的高度。

102.因此,电容结构mimcap在宽度上具有窄形状(在图6的视图中水平地)、在长度上细长(垂直于图6的视图),并且具有深度(在图6的视图中竖直地),该深度开始于从金属前电介质区域dpm的顶部的厚度edep的偏差,直到导电层p0。厚度偏差edep将允许在电容结构mimcap的顶部上形成接触cnt1。

103.图7图示了在图2的步骤之后蚀刻孔以形成金属接触的步骤,如将在常规方法中提供的。

104.各向异性干法蚀刻使用掩模mskcnt,掩模mskcnt的图案限定面向电容结构mimcap的第二金属层cm2的开口ouvcnt。

105.开口的对准可以承受电介质层cd的部分厚度上的偏移,而不会引起第二金属层cm2与第一金属层cm1之间的短路。

106.实际上,开口将用导电材料封住和填充,并且提供接触cnt1的形成以电连接电容结构mimcap的第二金属层cm2,有利地允许避免在第一金属层cm1与第二金属层cm2之间形成短路。

107.然而,关于图4或图5描述的步骤的备选方案可以提供在电容结构mimcap的上部上将第一金属层cm1和第二金属层cm2电绝缘。例如,图4的结构上的机械-化学平坦化可以被电介质层cd的水平部分停止。因此将在第二金属层cm2的顶部上获得自由开口,但第一金属层cm1将保持被电介质层cd覆盖。在这种情况下,第二金属层cm2可以在其自由开口处由金属轨道pm1直接电接触,而没有与第一金属层cm1短路的风险。而且,位于第一金属层cm1、电介质层cd和第二金属层cm2的堆叠的电容元件mimcap的生产之外的部分可以被蚀刻。

108.而且,其他开口ouvcnt被定位成与部分feol的要被接触的其他位置相对,例如在衬底sub的正面fa上的接触点cntsub的金属硅化物simsub的薄层上,或在导电层p0的金属硅化物的薄层上(在图7中不可见)。

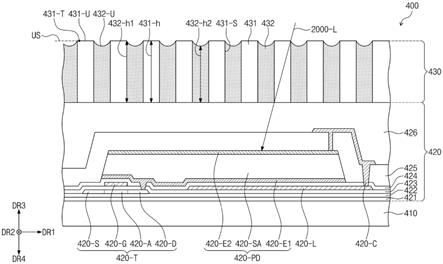

109.图8图示了在开口ouvcnt的侧面和底部上形成金属接触扩散屏障层的结果,金属接触扩散屏障层例如是钛的薄层和氮化钛的薄层的叠加ti/tin。

110.在该方法中的这一点上,例如借助于非氧化退火,有利地实施“利用屏障层填充”(术语取自通常的表达“屏障填充”)的步骤。利用屏障层填充“屏障填充”的步骤允许在薄扩散屏障层的材料(诸如钛)与要被接触的表面的材料(诸如,金属硅化物sim的硅)之间形成合金,以便加强这些层之间的电接触。

111.因此,利用屏障层填充“屏障填充”的步骤特别地改善了电容结构mimcap的第一金属层cm1与由多晶硅p0制成的导电层的金属硅化物sim的薄层的电连接。

112.然后,例如借助于金属w(通常是钨)的过量沉积,并且借助于通过机械-化学平坦化进行平整直到到达金属前电介质区域dpm的顶部,来形成接触cnt1、cnt3(图9)的金属主体w。

113.图9示出了形成第一金属层级m1的结果。

114.在该示例中,第一金属层级m1包括金属轨道pm1,金属轨道pm1经由第一接触cnt1将电容结构mimcap的第二金属层cm2电连接在一起,并且还经由另一接触cnt3将第二金属层cm2与衬底sub电连接。

115.因此,除了在导电层p0与衬底sub之间的电容结构moscap的第一电容界面之外,还通过电容结构mimcap,经由金属轨道pm1提供了在导电层p0与衬底sub之间的附加电容界

面,而无需占用衬底sub上的附加空间。

116.图10以透视图图示了通过上面关于图2至图9描述的类型的方法获得的结构,其中使金属前电介质区域透明。

117.图11图示了图10的结构的俯视图。堆叠的元件通过透明化来表示。

118.坐标系x、y、z定向空间,在该空间中表示图10和图11,上面提到的水平位于xy平面中,在x方向上是纵向并且在y方向上是横向,竖直由z方向指示。图1至图9因此在该定向的yz平面中被表示。

119.上面关于图1和图2至图9描述的元件具有相同的附图标记并且将不再全部详述。

120.尽管如此,在图10和图11的示例中,一方面,电容结构mimcap未对准在电容元件moscap的沟槽trsub上方,而是被定位成与位于电容元件moscap的每个沟槽trsub之间的空间相对。

121.另一方面,应当注意,第一金属层级m1的第一金属轨道pm1经由第一接触cnt1与电容结构mimcap的第二金属层cm2连接。第一金属层级m1的第二金属轨道pm2经由第二接触cnt2与导电层p0连接。第一金属层级m1的第三金属轨道pm3经由第三接触cnt3与衬底的被称为有源区域act的区域连接,该有源区域act包含电容结构moscap,并且通常由浅绝缘区域sti界定。

122.因此,第一金属轨道pm1构成第一电容电极e1的端子,第二金属轨道pm2构成第二电容电极e2的端子,并且第三金属轨道pm3构成第三电容电极e3的端子。

123.电容结构mimcap包括第一电极e1和第二电极e2,并且电容结构moscap包括第二电极e2和第三电极e3。

124.在等效电路图中,电容结构mimcap和电容结构moscap连接到共同的第二电极e2。

125.因此,通过将第一电极e1与第三电极e3连接在一起,获得电容结构mimcap和电容结构moscap的并联组件。还可以通过将第一电极e1与第二电极e2连接在一起来使电容结构mimcap短路,以仅使用电容结构moscap,或者还可以通过将第二电极e2与第三电极e3连接在一起来使电容结构moscap短路,以仅使用电容结构mimcap。

126.换句话说,这允许通过选择使用两个电容结构mimcap、moscap中的任一个或其组合,来调制电路的电容值。

127.最后,应当注意,在图10和图11的示例中,电容结构mimcap的纵向端部被定位成基本与绝缘沟槽sti对有源区域act的界定相对。因此,第一接触cnt1朝向有源区域act的内部定位,而第二接触cnt2朝向有源区域act的外部定位,在绝缘沟槽sti上方。

128.图12和图13图示了图10和图11所示的集成电路的结构的备选方案。

129.在该备选方案中,电容结构mimcap朝向有源区域act的外部纵向延伸,在绝缘沟槽sti上方延伸。因此,第一接触cnt1位于导电层p0外部,而第二接触cnt2位于第一接触cnt1与有源区域act之间,在绝缘沟槽sti上方。第二接触cnt2被定位在电容结构mimcap之间的横向空间中。

130.这特别地允许增加电容结构mimcap的长度,并且因此增加电容结构mimcap的电容值。

131.集成电路的其他元件与图10和图11中所示的示例相同。

132.图14图示了在制造电阻-电容rc电路的上下文中,关于图1描述的金属-电介质-金

属“mim”类型的电容结构mimcap的应用的一个示例。先前关于图1描述的共同元件具有相同的附图标记并且将不再全部详述。

133.在该示例中,半导体部分feol的导电层ps放置在另一导电层p1上,该另一导电层p1被称为电阻导体条p1并且属于电阻元件res。

134.电阻导体条p1例如也由多晶硅制成,并且形成在绝缘区域sti上,绝缘区域sti例如是浅绝缘沟槽类型的。

135.电阻半导体条p1被配置成具有电阻值并且包括两个开放端部。开放端部包括金属硅化物sim的薄层,该金属硅化物sim经由相应的接触cnti、cnto电耦合到第一金属层级m1的金属轨道pmi、pmo。金属轨道pmi、pmo因此实现了电阻元件res的端子in、out。

136.导电层ps通过电介质厚度ono与电阻导体条p1电绝缘,电介质厚度ono包括例如氧化物层、氮化物层和氧化硅层的叠加。

137.有利地,特别是电阻导体条p1、电介质厚度ono和导电层ps的制造可以以制造浮栅晶体管的方式来实行,或者甚至在该制造方法的相同步骤期间同时被实行。

138.根据半导体部分feol的这种生产,借助于上面关于图3至图9描述的方法类型的方法,电容结构mimcap被制造在金属前电介质区域dpm中。

139.因此,通过将电容结构mimcap的第一电极e1与电阻元件res的端子out(被称为输出端子)电耦合,并且通过将电容结构mimcap的第二端子e2与基准电位(也就是说,接地)电耦合,获得图14的rc串联电阻-电容电路的电路图的组件。输出端子out形成rc串联电阻-电容电路的输出,而电阻元件res的另一端子in形成rc串联电阻-电容电路的输入。

140.尽管如此,通过将电容结构mimcap的第一电极e1与电阻元件res的端子in耦合,并且通过将电容结构mimcap的第二电极e2与电阻元件res的端子out电耦合,获得并联电阻-电容电路组件。

141.因此,由于电容结构mimcap在金属前电介质区域的体积中的有利生产,包括电阻元件res和电容元件mimcap的电阻-电容rc电路可以被生产在不大于电阻元件res单独占据的表面的衬底sub的表面上。

142.而且,本发明不限于关于图1至图14描述的实施例和实施方式,而是囊括所有变型,例如选择的材料可以不同于上面给出的示例,要不然位于导电层ps、p0之下的半导体区域feol的元件可以不同并且被应用于其他电组件。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。