1.本发明涉及集成电路领域,尤其涉及一种上电复位电路。

背景技术:

2.在集成电路领域,许多芯片都包含上电复位电路(power-on-reset,por),上电复位电路的作用是在系统上电和下电时产生复位信号,用于数字复位和各种ip启动等,使模拟和数字模块初始化至已知状态。

3.如果电源电压比较低,会导致电路输出的逻辑不确定,此外,从上电到时钟电路的正常起振也是需要时间的,在电源电压达到稳定之前时钟电路无法正常输出时钟信号。所以,需要在芯片上电的时候,给复位端一个复位信号让其中的数字电路在电源电压达到稳定值之前不要工作。

4.基本的上电复位电路会产生一个内部复位脉冲以避免“竞争”现象,并使器件保持静态,直到电源电压达到一个能保证正常工作的阈值。一旦电源电压达到阈值电压,上电复位电路就会释放内部复位信号,状态机开始初始化。通常情况下,电路系统在上电初期,电源电压还未达到稳定的预期状态时,许多电路元器件以及电路节点的电压和逻辑状态是不稳定的。为了使电路系统在每次上电后都能从设计者所期望的状态开始操作,可以利用上电复位电路在电源稳定后的一段时间内产生上电复位信号,该复位信号可以强制电路系统处于设计者所期望的初始状态,待复位信号的有效期结束后,电路系统再从所期望的初始状态开始运行。也就是说,复位信号可以对电路系统中的其他模块进行复位操作,从而消除上电初始时,电路模块的不稳定状态。

5.如图1所示,为传统的上电复位电路,该上电复位电路主要利用电阻r和电容c组成的rc电路来构成复位电路,利用rc电路中对电容的充电来实现信号的延迟,其中的非门电路用于整形以提高电路的抗干扰能力。传统的上电复位电路具有结构简单静态功耗低的优点,但是这样的电路存在以下缺点:(1)为了保证电源稳定一段时间后,复位电路才输出复位信号,因此需要产生延迟的rc电路的时间常数非常大,这样就使得电容非常大,在集成电路中,较大的电容将占用较大的面积;(2)电容对毛刺信号的滤波效果不是很好,若用于产生复位信号的电源电压具有较大的波动,则可能产生错误的复位信号而使得电路误操作,造成系统的不稳定;(3)传统上电复位电路的复位信号将由r、c和第一反相器的阈值电压vth共同决定,但是,由于该电路中各部分的工艺偏差可以叠加,将会导致最终结果与预期结果的偏差;有时将不会产生复位信号,有时可能电源并没有稳定,复位信号却过早地来到。

6.因此,亟需一种上电复位电路,其具有较小的版图面积,且具有较小的静态功耗,并且能产生与电源状态相匹配的稳定精确的复位信号。

技术实现要素:

7.为了解决上述技术问题,本发明提供一种上电复位电路,其特征在于,所述上电复

位电路包括第一级复位电路和第二级复位电路;所述第一级复位电路包括外部电源检测电路,内部电源检测电路以及带隙基准电路;其中,外部电源检测电路分别与内部电源检测电路和带隙基准电路电性连接;所述第一级复位电路用于粗略地对外部电源电压和内部电源电压进行检测;所述外部电源检测电路用于检测外部电源电压,当外部电源电压上升到一定的电压时,输出第一复位信号;所述内部电源检测电路用于检测内部电源电压,当内部电源电压上升到一定的电压时,输出第二复位信号;所述带隙基准电路用于产生基准电压;所述第二级复位电路包括分压电路,比较电路和复位信号产生电路;所述第二级复位电路用于对内部电源电压进行精确地检测;所述分压电路与内部电源电压相连接,用于对内部电源电压进行分压,并获得分压电压;所述比较电路分别与分压电路和带隙基准电路相连接,用于将分压电压和基准电压进行比较;所述复位信号产生电路与比较电路相连接,用于产生上电复位信号,当分压电压高于基准电压时,复位信号产生电路产生上电复位信号。

8.采用本发明中提供的上电复位电路,通过两级复位电路的方式对外部电源电压和内部电源电压进行监测,第一级复位电路在监测时,精度较低但是功耗极低,第二级复位电路需要一定的功耗,但是精度极高。在进行监测时,当第一级复位电路达到一定的设定电压并触发之后,才开始第二级监测,满足条件之后将自动关闭第二级检测,因此,使用本发明中的两级复位电路,在实现了高精度的同时,极大地缩小了功耗。

9.优选地,当所述外部电源检测电路输出第一复位信号时,内部电源检测电路开始检测内部电源电压,所述带隙基准电路开始产生基准电压。

10.优选地,所述第一级复位电路还包括基准电压检测器,用于检测基准电压是否已经到达设定值。

11.优选地,所述外部电源检测电路包括第一电阻器,第一nmos管,第二nmos管,第一poms管,以及第一反相器;其中,所述第一电阻器和所述第二nmos管串联连接在外部电源电压和接地电压之间,所述第一电阻器连接外部电源电压,所述第二nmos管被配置为漏极与所述第一电阻器连接,源级与接地电压连接,栅极与所述第一nmos管和所述第一pmos管的栅极相连接;所述第一nmos管和所述第一pmos管串联连接在外部电源电压和接地电压之间,其中,所述第一pmos管的源级与外部电源电压相连,所述第一nmos管的源级与接地电压相连,所述第一nmos管和所述第一pmos管的栅极相连连接到所述第二nmos管的栅极,所述第一nmos管和所述第一pmos管的漏极相连连接到第一反相器。

12.采用该外部电源检测电路,采用电阻和二极管连接的nmos管的形式产生第一复位信号信号,因为第一复位信号的值主要取决于nmos管的阈值电压,因此,相比于传统的产生复位信号的方式,只有一个变量,因此,受工艺影响较小,增加了信号产生的稳定性。

13.优选地,所述内部电源检测电路包括第二电阻器,第二pmos管,第三pmos管,第三nmos管,第四nmos管,以及第二反相器;其中,第二电阻器和第四nmos管串联连接在内部电源电压和接地电压之间,第二电阻器连接内部电源电压,第四nmos管被配置为漏极与第二电阻器连接,源级与接地电压连接,栅极与第二pmos管和第三nmos管的栅极相连接;第二pmos管和第三nmos管串联连接在内部电源电压和接地电压之间,其中,第二pmos管的源级与内部电源电压相连,第三nmos管的源级与接地电压,第三nmos管和第二pmos管的栅极相连连接到第二nmos管的栅极,第三nmos管和第二pmos管的漏极相连连接到第二反相器;第三pmos管的源级连接至内部电源电压,栅极与第一上电复位电路的输出端电性连接,漏极

与第三nmos管、第二pmos管以及第二nmos管的栅极连接。

14.采用该内部电源检测电路,采用电阻和二极管连接的nmos管的形式产生第二复位信号,因为第二复位信号的值主要取决于nmos管的阈值电压,因此,相比于传统的产生复位信号的方式,只有一个变量,因此,受工艺影响较小,增加了信号产生的稳定性。

15.优选地,所述分压电路包括三个可变电阻,所述三个可变电阻串联在内部电源电压和接地电压之间。

16.优选地,所述比较电路用于将分压电路输出的分压电压和基准电压进行比较,若分压电压低于基准电压,则输出低电平,若分压电压高于基准电压,则输出高电平。

17.优选地,所述上电复位电路用于nand闪存芯片。

附图说明

18.图1为传统的上电复位电路示意图。

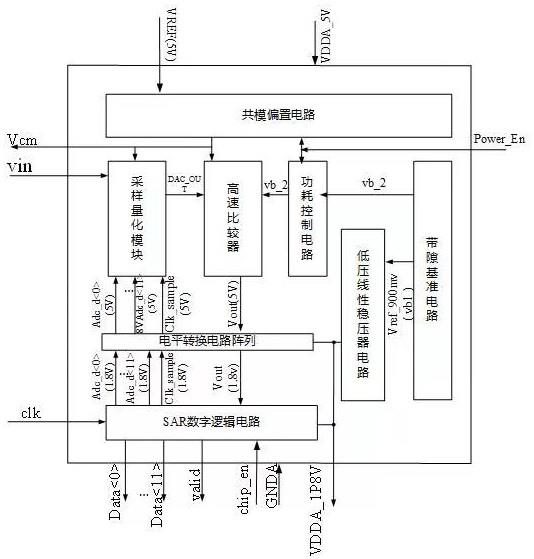

19.图2为本发明的上电复位电路的框架示意图。

20.图3为本发明的第一级上电复位电路的外部电源检测电路。

21.图4为本发明的第一级上电复位电路的内部电源检测电路。

22.图5为本发明的第二级上电复位电路。

23.图6为本发明的上电复位电路的上电顺序示意图。

具体实施方式

24.以下配合图式及本发明的较佳实施例,进一步阐述本发明为达成预定发明目的所采取的技术手段。

25.当前的一些集成电路不直接采用由外部施加的外部电源电压,而是采用内部电压发生器电路产生设定的内部电源电压以降低或者升高外部电源电压,并将产生的内部电源电压施加到内部电路以提高设备的可靠性。而外部电源电压可以作为内部电压发生器电路、带隙基准电路(bandgap)以及io的电源使用。因此,在设计上电复位电路时,需要同时检测内部电源和外部电源的电压,使得集成电路的各个模块均能正常工作。

26.基于以上需求,本发明提供一种上电复位电路。请参照图2所示,图2为本发明的上电复位电路的框架示意图。该上电复位电路包括第一级复位电路和第二级复位电路,其中,第一级复位电路用于粗略地检测内部电源和外部电源电压,使得内部电源和外部电源电压能达到一定的电压值且能使得第二级复位电路中的比较电路可以正常工作;第一级复位电路具有较小的功耗。第二级复位电路用于精确地检测内部电源电压,当电源电压达到目标电压时,产生上电复位信号,对集成电路内部进行初始化。通过对内部电源电压进行精准检测,可以防止芯片受到损害,因为内部模块对电源的敏感性比较高,而且负载也比较大,因此,需要对内部电源电压进行精准检测,当其达到特定的目标电压时,内部模块才能开始工作。

27.第一级复位电路包括外部电源检测电路,内部电源检测电路以及带隙基准电路,其中外部电源检测电路分别与内部电源检测电路和带隙基准电路电性连接。外部电源检测电路用于检测外部电源电压,当外部电源电压上升到一定的电压时,外部电源检测电路将产生第一复位信号por_ext。内部电源检测电路用于检测内部电源电压,当第一复位信号

por_ext产生后,内部直流电源产生内部电源电压,内部电源检测电路开始对内部电源电压进行检测,当内部电源电压上升到一定的电压时,内部电源检测电路将产生第二复位信号por_int。当第一复位信号por_ext和第二复位信号por_int均变为低电平时,系统开始初始化。在初始化时,内部寄存器全部重置,并载入预设的参数,这样可使得芯片能工作在正确的状态。带隙基准电路用于产生基准电压vbg,当第一复位信号por_ext产生后,带隙基准电路启动开始产生基准电压,直至产生稳定的基准电压vbg。为了使得电路更加稳定地工作,第一级复位电路还可以包括基准电压检测器,用于检测基准电压是否已经到达设定值,对于一般的带隙基准电路,基准电压vbg的值为1.24v。

28.第二级复位电路包括分压电路、比较电路和复位信号产生电路。其中,分压电路与内部电源电压相连接,用于对内部电源电压进行分压,以获得分压电压v1;比较电路分别与分压电路和带隙基准电路相连接,用于将分压电压v1与基准电压vbg进行比较,若分压电压低于基准电压vbg,则输出低电平,若分压电压高于基准电压vbg,则输出高电平;复位信号产生电路与比较电路相连接,用于产生上电复位信号ard_rst(即auto-read reset,自动读取参数重置),当分压电压高于基准电压vbg时,产生上电复位信号ard_rst。当产生上电复位信号ard_rst时,系统将自动读取参数,实现复位。

29.本发明中提供的上电复位结构包括两级结构,第一级上电复位电路用于粗略地对外部电源电压和内部电源电压进行检测,当外部电源电压和内部电源电压均达到一定的值时,第一复位信号por_ext和第二复位信号por_int均变为低电平,系统开始复位;第二级上电复位电路用于对内部电源电压进行精确地检测,当内部电源电压达到设置的电压值时,将产生上电复位信号ard_rst,系统将自动读取参数,实现复位。采用该上电复位结构,具有以下优势:通过两级复位电路的方式对外部电源电压和内部电源电压进行监测,第一级复位电路在监测时,精度较低但是功耗极低,第二级复位电路需要一定的功耗,但是精度极高。在进行监测时,当第一级复位电路达到一定的设定电压并触发之后,第二级复位电路才开始监测,满足条件之后将自动关闭第二级检测,因此,使用本发明中的两级复位电路,在实现了高精度的同时,极大地缩小了功耗。

30.请参照图3所示,图3为本发明的第一级上电复位电路的外部电源检测电路的一个实施例。外部电源检测电路包括第一电阻器r1,第一nmos管n1,第二nmos管n2,第一poms管p1,以及第一反相器a1。其中,第一电阻器r1和第二nmos管n2串联连接在外部电源电压vcc_ext和接地电压之间,第一电阻器r1连接外部电源电压vcc_ext,第二nmos管n2被配置为漏极与第一电阻器r1连接,源级与接地电压连接,栅极与第一nmos管n1和第一pmos管p1的栅极相连接。第一nmos管n1和第一pmos管p1串联连接在外部电源电压vcc_ext和接地电压之间,其中,第一pmos管p1的源级与外部电源电压vcc_ext相连,第一nmos管n1的源级与接地电压相连,第一nmos管n1和第一pmos管p1的栅极相连连接到第二nmos管n2的栅极,第一nmos管n1和第一pmos管p1的漏极相连连接到第一反相器a1。其中,第一nmos管n1和第一pmos管p1以及第二nmos管n2的栅极电压记为ref_ext。外部电源检测电路通过第一反相器a1输出第一复位信号por_ext。

31.在实际的工作过程中,当外部电源电压vcc_ext上电时,由于第二nmos管n2仍然处于截止状态,ref_ext电压会随着vcc_ext电压上升。当ref_ext大于等于第二nmos管n2的阈值电压vthm2时,第二nmos管n2进入饱和区,此时第一nmos管n1打开(即ref_ext》vthm1),第

一pmos管p1关闭(即|ref_ext-vcc_ext|《|vthp1|),第一nmos管n1和第一pmos管p1的输出端被第一nmos管n1拉低至接地,由于反相器a1的作用,此时第一复位信号por_ext为高电平。随着vcc_ext继续上升,ref_ext只是略微增加,其差值将持续增加,当|ref_ext-vcc_ext|大于等于第一pmos管p1的阈值电压|vthp1|,此时第一pmos管p1打开,第一pmos管p1处于饱和区,而第一nmos管n1处于线性区,因为第一nmos管n1的驱动能力大于第一pmos管p1,因此,此时第一nmos管n1和第一pmos管p1的输出端仍然为低电平,第一复位信号por_ext为高电平。随着外部电源电压vcc_ext继续上升,上升至外部电源的设定阈值,此时第一nmos管n1进入饱和区,此时第一nmos管n1和第一pmos管p1的输出端上升至高电平,由于反相器a1的作用,将产生具有低电平的第一复位信号por_ext。

32.请参照图4所示,图4为本发明的第一级上电复位电路的内部电源检测电路的一个实施例。内部电源检测电路包括第二电阻器r2,第二pmos管p2,第三pmos管p3,第三nmos管n3,第四nmos管n4,以及第二反相器a2。其中,第二电阻器r2和第四nmos管n4串联连接在内部电源电压vdd_int和接地电压之间,第二电阻器r2连接内部电源电压vdd_int,第四nmos管n4被配置为漏极与第二电阻器r2连接,源级与接地电压连接,栅极与第二pmos管p2和第三nmos管n3的栅极相连接。第二pmos管p2和第三nmos管n3串联连接在内部电源电压vdd_int和接地电压之间,其中,第二pmos管p2的源级与内部电源电压vdd_int相连,第三nmos管n3的源级与接地电压,第三nmos管n3和第二pmos管p2的栅极相连连接到第二nmos管n2的栅极,第三nmos管n3和第二pmos管p2的漏极相连连接到第二反相器a2。第三pmos管p3的源级连接至内部电源电压vdd_int,栅极通过反相器连接至第一上电复位电路的输出端,漏极与第三nmos管n3、第二pmos管p2以及第二nmos管n2的栅极连接,其连接节点的电压记为ref_int。内部电源检测电路通过第二反相器a2输出第二复位信号por_int。

33.在实际的工作过程中,因为第三pmos管p3的栅极通过反相器连接至第一上电复位电路的输出端,因此,当外部电源检测电路未被触发并输出具有高电平的第一复位信号por_ext时,第三pmos管p3的栅极电压为低电平。当外部电源检测电路被触发并输出具有低电平的第一复位信号por_ext时,第三pmos管p3的栅极电压为高电平,此时第三pmos管p3处于截止状态,第一级上电复位电路的内部电源检测电路开始对内部电源的电压进行检测。其工作原理与外部电源检测电路类似。当内部电源电压vdd_int电压上升时,由于第四nmos管n4仍然处于截止状态,ref_int电压会随着vdd_int电压上升。当vdd_int大于等于第四nmos管n4的阈值电压vthm4时,第四nmos管n4进入饱和区,此时第三nmos管n3打开(即ref_int》vthm3),第二pmos管p2关闭(即|ref_int-vdd_int|《|vthp2|),第三nmos管n3和第二pmos管p2的输出端被第三nmos管n3拉低至接地,由于反相器a2的作用,此时第二复位信号por_int为高电平。随着vdd_int继续上升,ref_int只是略微增加,其差值将持续增加,当|ref_int-vdd_int|大于等于第二pmos管p2的阈值电压|vthp2|,此时第二pmos管p2打开,第二pmos管p2处于饱和区,而第三nmos管n3处于线性区,因为第三nmos管n3的驱动能力大于第二pmos管p2,因此,此时第三nmos管n3和第二pmos管p2的输出端仍然为低电平,第二复位信号por_int为高电平。随着内部电源电压vdd_int继续上升,上升至内部电源的设定阈值,此时第三nmos管n3进入饱和区,此时第三nmos管n3和第二pmos管p2的输出端上升至高电平,由于反相器a2的作用,将产生具有低电平的第二复位信号por_int。

34.当外部电源检测电路被触发后,内部电源检测电路开始工作,检测内部电源电压

是否达到一定的值;并且带隙基准电路开始工作,用于产生稳定的基准电压vbg。当内部电源检测电路被触发产生第二复位信号后,集成电路系统开始初始化。在初始化时,内部寄存器全部重置,并载入预设的参数,这样可使得芯片能工作在正确的状态。

35.请参照图5所示,图5为本发明中上电复位电路的第二级复位电路。分压电路用于对内部电源电压进行分压,以获得分压电压v1。其中,分压电路采用由三个串联的可变电阻串联在内部电源电压vdd_int和接地电压vss之间,采用可变电阻可以任意地调节分压电压v1与内部电源电压vdd_int的比值,以便对不同的内部电源电压进行检测。比较电路将分压电压v1与基准电压vbg进行比较,若分压电压低于基准电压vbg,则输出低电平,若分压电压高于基准电压vbg,则输出高电平。当内部电源电压vdd_int恰好变为目标电压时,分压器的输出将等于vbg,则比较器的输出将由低电平变为高电平,复位信号产生电路将会检测到比较器输出的上升沿。复位信号产生电路用于产生上电复位信号ard_rst,当分压电压高于基准电压vbg时,复位信号产生电路将会检测到比较器输出的上升沿,开始产生上电复位信号ard_rst。当产生上电复位信号ard_rst时,系统将自动读取参数,实现复位。

36.请参照图6所示,图6为本发明的上电复位电路的上电顺序示意图。首先,开始上电时,vdd_int等于vcc_ext,外部电源检测电路开始对外部电源电压vcc_ext进行检测,当vcc_ext上升到一定的值时,外部电源检测电路被触发,产生具有低电平的第一复位信号por_ext。

37.当具有低电平的第一复位信号por_ext产生之后,vdd_int将会由内部电压发生器vdc产生,内部电源检测电路开始检测内部电源电压的大小,并且带隙基准电路开始产生vbg。随着内部电源电压vdd_int上升,内部电源检测电路被触发,产生具有低电平的第二复位信号por_int。

38.当具有低电平的第二复位信号por_int产生之后,系统开始进行初始化。经过一段时间,其中内部电压vdd_int继续上升,直到达到预定的电压时,第二级上电复位电路将产生上电复位信号ard_rst,系统将自动读取参数,实现复位。

39.本发明中提供的上电复位电路具有如下优势:(1)本发明中的上电复位电路,采用电阻和二极管连接的nmos管的形式产生第一复位信号和第二复位信号,因为第一复位信号和第二复位信号的值主要取决于nmos管的阈值电压,因此,相比于传统的产生复位信号的方式,只有一个变量,因此,受工艺影响较小,增加了信号产生的稳定性;(2)在本发明中,通过两级复位电路的方式对外部电源电压和内部电源电压进行监测,第一级复位电路在监测时,精度较低但是功耗极低,第二级复位电路需要一定的功耗,但是精度极高。在进行监测时,当第一级复位电路达到一定的设定电压并触发之后,才开始第二级监测,满足条件之后将自动关闭第二级检测,因此,使用本发明中的两级复位电路,在实现了高精度的同时,极大地缩小了功耗。

40.以上所述仅是本发明的优选实施例而已,并非对本发明做任何形式上的限制,虽然本发明已以优选实施例揭露如上,然而并非用以限定本发明,任何熟悉本专业的技术人员,在不脱离本发明技术方案的范围内,当可利用上述揭示的技术内容作出些许更动或修饰为等同变化的等效实施例,但凡是未脱离本发明技术方案的内容,依据本实用发明的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本发明技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。