1.本技术涉及芯片产品验证领域,具体而言本技术实施例涉及一种内存控制器验证装置以及验证系统。

背景技术:

2.内存控制器有单通道类型的也有双通道类型的。例如,ddr5内存控制器是双通道控制器,这是由于ddr5 udimm内存分为两个内存子通道。实际的ddr存储子系统中,ddr5内存控制器和udimm条中间由ddr phy连接。不同的子通道数目会造成内存控制器对模式寄存器的访问复杂度加大。不同的内存包含的模式寄存器的数目具有较大差异,因此造成内存控制器对不同内存的模式寄存器的访问方式也存在较大差异。

3.例如,ddr4 sdram内存有mr0~mr7共8个模式寄存器,通过mpr(multi purpose register)间接完成模式寄存器的操作,而ddr5 sdram的每个内存颗粒均有256个模式寄存器,模式寄存器数量非常庞大。

4.因此如何设计合理的针对ddr5的验证模型以验证内存控制器对各模式寄存器的访问过程成了亟待解决的技术问题。

技术实现要素:

5.本技术实施例的目的在于提供一种内存控制器验证装置以及验证系统,该验证装置和验证系统简化了验证环境(即内存控制器对模式寄存器的访问环境)访问模式寄存器时所需的处理过程,加快了对内存控制器访问内存模式寄存器过程的仿真和调试效率。

6.第一方面,本技术的一些实施例提供一种内存控制器验证装置,所述内存控制器验证装置包括:模式寄存器模块,包括为内存中各内存颗粒分别对应构建的模式寄存器,其中,所述内存是由待验证内存控制器所要实际访问的存储器;至少一个访问控制模块,被配置为通过指针访问所述模式寄存器模块上包括的目标模式寄存器,其中,一个访问控制模块与所述内存的一个内存子通道对应设置。

7.本技术的一些实施例针对同一内存子通道,在验证过程可以把虚拟rank(即通过访问控制模块中设置的指针)中颗粒设置到实际构建的内存颗粒的模式寄存器(即模式寄存器模块)上,这样可以有效验证内存控制器对各模式寄存器的访问控制操作,且这种设计结构,简化了验证环境访问模式寄存器时所需的处理过程,加快了仿真和调试效率。

8.在一些实施例中,所述内存包括n个rank,每个rank包括m个内存颗粒且每个内存颗粒包括l个模式寄存器,其中,所述模式寄存器模块被配置为:包括构建的n个模式寄存器实例,其中,每个模式寄存器实例包括为所述m个内存颗粒中每个内存颗粒构建的l个模式寄存器,一个模式寄存器实例与一个rank对应设置,n为大于或等于1的整数,m以及l均为大于1的整数。

9.本技术的一些实施例为内存包括的所有内存颗粒分别构建模式寄存器,且构建针对内存各bank的模式寄存器实例,这种设计结构可以简化验证环境访问模式寄存器时所需

的处理过程。

10.在一些实施例中,所述内存包括a个内存条,且一个内存子通道包括分布于所述a个内存条上共b个rank;其中,所述模式寄存器模块被配置为:包括构建的a个内存条,针对一个内存子通道所述模式寄存器被配置为包括构建的b个rank,其中,所述构建的b个rank位于所述构建的a个内存条上;所述访问控制模块被配置为包括构建的b个虚拟rank,其中,一个虚拟rank对应一个构建的rank,且每个虚拟rank对应唯一编码;其中,a和b均为大于或等于1的整数。

11.本技术的一些实施例模式寄存器会完全复制实际内存中所有的rank,包括各rank分布的内存条编号,在内存条的正面还是反面等,而访问控制模块不需要构建和内存条相关的要素和信息而只是直接构建与一个内存子通道对应的所有rank的虚拟rank,且对该虚拟rank唯一编码,通过这种设计方式,可以加快对构建的各rank的访问速度,并最终提升验证速度。

12.在一些实施例中,通过所述编码访问每个虚拟rank,且每个虚拟rank通过rank访问指针访问所述模式寄存器模块上对应的目标rank。

13.本技术的一些实施例通过为虚拟rank分配的编码寻找目标虚拟rank,并通过虚拟rank对应的rank访问指针访问在模式寄存器模块上构建的rank,这使得对各构建的rank的访问与rank在dimm(内存条)上的分布形式无关,从而实现在rank水平上对内存颗粒的直接访问。

14.在一些实施例中,所述每个虚拟rank包括一组指针,其中,通过各组指针包括的模式寄存器访问指针可访问位于所述模式寄存器模块上的目标模式寄存器。

15.本技术的一些实施例可以借助虚拟rank包括的模式寄存器访问指针来访问模式寄存器模块上构建的目标模式寄存器,实现了对模式寄存器的快速访问。

16.在一些实施例中,所述模式寄存器被配置为包括多种大小不同的字段且各字段分别对应不同的名字,其中,通过各字段的名字访问所述模式寄存器包括的各种字段。

17.本技术的一些实施例通过为构建的各模式寄存器定义多种字段从而可以实现对各模式寄存器不同字段的访问,细化了访问粒度,丰富了对待验证的内存控制器的验证参数。

18.在一些实施例中,所述模式寄存器模块上各内存颗粒序号和pda id编码之间的映射关系可被动态配置。

19.本技术的一些实施例可以动态配置内存颗粒序号和单颗内存颗粒访问编码之间的映射,极其方便的实现对内存颗粒pda id编码任意组合的测试。

20.在一些实施例中,通过不同识别信号区分所述内存包括的不同内存子通道。

21.本技术的一些实施例,通过不同的识别号可以访问不同的内存子通道,使得针对不同内存子通道的验证操作得以实现,且本技术的一些实施例可动态配置单颗内存颗粒访问编码(即pda id编码)与内存颗粒序号之间的关系。

22.在一些实施例中,所述访问控制模块还包括:指令解码器,被配置为根据接口协议对接口信号进行解析获取内存颗粒操作指令,其中,所述接口协议是所述待验证的内存控制器的向下接口单元所采用的协议;模式寄存器操作指令解析单元,被配置为:对所述内存颗粒操作指令进行解析,获取解析结果;根据所述解析结果进行指令筛选与模式寄存器操

作相关的目标操作指令;子通道模式寄存器应用方法模块,被配置为:获取与所述目标操作对应的目标虚拟rank,并根据与所述目标虚拟rank对应的rank访问指针访问位于所述模式寄存器模块上的目标rank,完成对所述目标rank上所有模式寄存器的所述目标操作;或者,获取与所述目标操作对应的目标虚拟rank和目标模式寄存器,通过与所述目标虚拟rank对应的rank访问指针访问目标rank,并通过所述目标虚拟rank包括的模式寄存器访问指针访问所述目标rank上的所述目标模式寄存器,完成对所述目标模式寄存器的所述目标操作。

23.本技术的一些实施例通过为每个内存子通道设置的指令解码器、模式寄存器操作指令解析单元可以通过接口协议分析筛选出于模式寄存器相关的操作指令,并根据子通道模式寄存器应用方法模块上集成的访问方法以及操作函数完成对构建的模式寄存器的操作,更好的验证了待验证的内存控制器的性能。

24.在一些实施例中,所述子通道模式寄存器应用方法模块至少包括:与模式寄存器的所有操作指令对应的实现函数,以及从内存子通道到目标内存颗粒之间的逻辑转换映射表,其中,通过查找所述逻辑转换映射表获取所述目标模式寄存器在所述模式寄存器模块上的分布位置,通过与所述目标操作对应的实现函数完成所述目标操作。

25.本技术的一些实施例通过在子通道模式寄存器应用方法模块上封装多种操作函数以及映射关系可以方便快捷的实现对构建的模式寄存器的访问和目标操作,更加快速的完成对内存控制器的验证工作。

26.在一些实施例中,所述接口协议为dfi协议,所述内存为udimm,其中,所述模式寄存器操作指令解析单元还被配置为:通过检测所述内存颗粒操作指令筛选得到mpc指令,并获得mpc指令解析结果;若根据所述mpc指令解析结果确认处于pda操作状态,则根据所述pda操作状态得到所述目标模式寄存器。

27.本技术的一些实施例通过设置的模式寄存器操作指令解析单元还可以完成pda操作状态下的各种模式寄存器操作指令,更全面的验证了内存控制器的性能。

28.在一些实施例中,所述内存控制器验证装置还包括构建的影子寄存器,其中,若通过所述模式寄存器操作指令解析单元确认处于pda状态,则所述子通道模式寄存器应用方法模块还被配置为通过所述影子寄存器和所述目标模式寄存器实现与所述影子寄存器对应的目标操作。

29.本技术的一些实施例还可以实现影子寄存器操作,更全面验证了内存控制器的性能。

30.在一些实施例中,所述子通道模式寄存器应用方法模块还被配置当确认所述目标模式寄存器属于禁止访问的模式寄存器时,则会生成错误提示信息。

31.本技术的一些实施例还对禁止访问的模式寄存器进行访问报警,更全面验证了内存控制器的性能。

32.在一些实施例中,所述模式寄存器操作指令解析单元,包括:多个目标类型指令筛选单元,其中,所述多个目标类型指令筛选单元中的各单元被配置为从所述内存颗粒操作指令中筛选得到任一目标类型的模式寄存器操作指令。

33.本技术的一些实施例通过设置的多类指令筛选单元可以更全面的验证内存控制器对模式寄存器的各类操作。

34.在一些实施例中,若所述内存为udimm时,所述模式寄存器操作指令解析单元包

括:mpc命令处理单元,输入端与所述指令解码器的输出端连接,且被配置为从所指令解码器的输出结果中获取mpc指令,并解析所述mpc指令得到mpc指令解析结果;mrw命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出mrw指令,并解析所述mrw指令得到mrw指令解析结果;mrr命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出mrr指令,并解析所述mrr指令得到mrr指令解析结果;vrefca/vrefcs命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出vrefca和/或vrefcs指令,并解析所述vrefca和/或vrefcs指令得到vrefca和/或vrefcs指令解析结果。

35.本技术的一些实施例可以完成针对udimm类型内存的包括mpc命令在内的多种命令的验证。

36.在一些实施例中,所述接口协议为dfi协议,所述模式寄存器操作指令解析单元还包括:pda监控模块,被配置为确认内存处于pda操作状态;其中,所述mpc命令处理单元的输出端与所述pda监控模块的输入端连接其中,所述pda监控模块通过所述mpc指令解析结果确认处于所述pda操作状态;所述mrw命令处理单元的输入端与所述pda监控模块的输出端连接;所述mrr命令处理单元的输入端与所述pda监控模块的输出端连接;所述vrefca/vrefcs命令处理单元的输入端与所述pda监控模块的输出端连接。

37.本技术的一些实施例单独设置的功能模块即pda监控模块确认处于pda操作状态,可以对待验证内存控制器进行更加完整的性能验证。

38.第二方面,本技术的一些实施例提供一种内存模式寄存器建模方法,用于构建如第一方面任一实施例所述的内存控制器验证装置,所述内存模式寄存器建模方法,包括:构建内存中各内存子通道的模式寄存器空间;创建用于访问所述模式寄存器空间中包括的目标内存模式寄存器的访问工具,其中,所述访问工具被配置为根据指针访问所述模式寄存器空间包括的目标模式寄存器并完成对目标模式寄存器的至少一种操作,所述至少一种操作包括如下操作中的一种或多种:对所述目标模式寄存器包括的各种字段的读或写操作,对所述目标模式寄存器整体的读或写操作和对影子寄存器访问操作。

39.在一些实施例中,所述构建至少一个内存通道中各内存通道的模式寄存器空间,包括:基于dfi界面,对内存颗粒的空间关系建模,并将同一个内存子通道包括的所有构建的与内存颗粒对应的模式寄存器阵列映射到dfi接口对应的虚拟rank模式寄存器阵列上。

40.在一些实施例中,在所述创建用于访问所述模式寄存器空间中包括的目标内存模式寄存器的访问工具之后,所述内存模式寄存器建模方法还包括:添加行为模型,并将所述访问工具以及所述行为模型添加至内存子通道模型中,其中,所述行为模型用于模拟至少部分模式寄存器的行为。

41.在一些实施例中,在所述将所述访问工具以及所述行为模型添加至内存子通道模型中之后,所述内存模式寄存器建模方法还包括:将所述内存子通道模型和内存控制器进行封装。

42.在一些实施例中,所述对内存颗粒的空间关系建模,包括:创建待构建的模式寄存器的各字段类型以及各字段类型的名称;根据所述各字段类型创建一个模式寄存器,得到构建模式寄存器;根据内存颗粒包括的所有模式寄存器的数量创建多个所述构建模式寄存器,得到内存颗粒模式寄存器组;根据rank上包括的内存颗粒的总数目,创建多个所述内存

颗粒模式寄存器组,得到rank模式寄存器组,其中,所述rank位于与待验证的内存控制器实际连接的内存上;根据所述内存包括的各内存子通道类型,创建多个所述rank模式寄存器组,得到内存子通道模式寄存器组,其中,所述内存颗粒、所述rank以及所述内存子通道均位于所述内存上,所述内存为待验证的内存控制器实际所要访问的存取器。

43.在一些实施例中,所述各字段分别对应不同的比特位数,最长字段的长度等于一个模式寄存器的长度,最短字段的长度为1且字段的总数目与最长字段的长度相同。

44.第三方面,本技术的一些实施例提供一种验证方法,所述验证方法基于如第一方面任一实施例提供的内存控制器验证装置对待验证的内存控制器访问模式寄存器的过程进行验证,所述验证方法包括:针对每个内存子通道,完成在dfi接口的当前指令解码,得到指令解码结果;根据所述指令解码结果确认所述当前指令属于与内存模式寄存器操作相关的内存模式寄存器操作指令;确认所述内存模式寄存器操作指令是针对一个可寻址的目标模式寄存器的,则通过与目标虚拟rank对应的rank访问指针访问目标rank并通过所述目标虚拟rank包括的内存颗粒访问指针访问所述目标模式寄存器,完成对所述目标模式寄存器的操作;其中,所述操作是所述当前指令对应的函数,所述目标模式寄存器位于所述目标rank上,所述目标rank位于模式寄存器模块上,所述目标虚拟rank是构建的用于访问所述目标rank上各模式寄存器的指针组,所述模式寄存器模块包括针对内存中各内存颗粒构建的模式寄存器,所述内存是由待验证内存控制器实际所要访问的存储器。

45.在一些实施例中,所述验证方法还包括:确认所述内存模式寄存器操作指令是针对一个目标虚拟rank的,则通过与所述目标虚拟rank对应的rank访问指针访问目标rank包括的所有模式寄存器,完成对所述所有模式寄存器的操作。

46.在一些实施例中,所述验证方法还包括:确认所述内存模式寄存器操作指令是针对影子模式寄存器的操作,则通过调用影子寄存器处理函数完成所述操作。

47.在一些实施例中,所述验证方法还包括:若确认所述内存模式寄存器操作指令所要访问的虚拟rank不存在或者目标模式寄存器属于禁止访问的,则生成错误提示信息。

48.第四方面,本技术的一些实施例提供一种验证系统,所述验证系统包括:待验证的内存控制器,被配置为将用于访问内存颗粒的操作转换到内存包括的各独立的子内存通道上;控制器向下接口单元,被配置为将所述待验证的内存控制器上包括的各独立的内存子通道连接至相应内存通道的目标接口协议环境中;以及如第一方面任意实施例所述的内存控制器验证装置;其中,所述内存控制器验证装置通过所述控制器向下接口单元与所述待验证的内存控制器连接。

49.在一些实施例中,所述控制器向下接口单元包括dfi接口单元。

附图说明

50.为了更清楚地说明本技术实施例的技术方案,下面将对本技术实施例中所需要使用的附图作简单地介绍,应当理解,以下附图仅示出了本技术的某些实施例,因此不应被看作是对范围的限定,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他相关的附图。

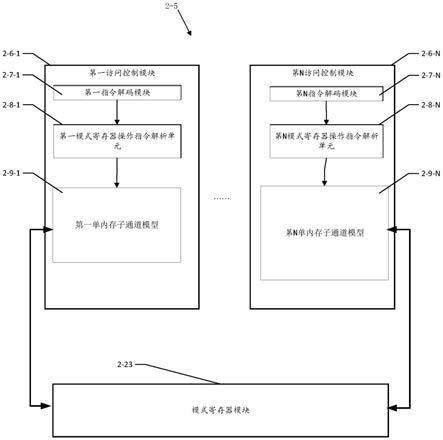

51.图1为本技术实施例提供的验证内存控制器的系统的组成示意图之一;

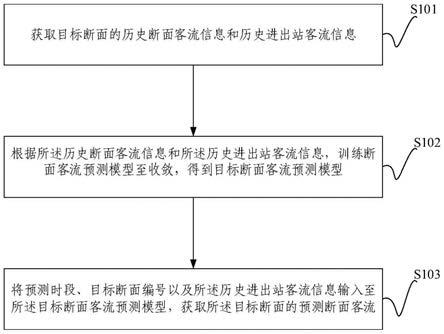

52.图2为本技术实施例提供的内存模式寄存器建模方法的流程图;

53.图3为本技术实施例提供的验证内存控制器的装置的组成示意图之一;

54.图4为本技术实施例提供的模式寄存器操作指令解析单元的组成示意图之一;

55.图5为本技术实施例提供的模式寄存器操作指令解析单元的组成示意图之二;

56.图6为本技术实施例提供的一种实际中ddr5 sdram controller和phy、以及dram内存之间的系统构成示意图;

57.图7a和图7b为本技术实施例提供的基于图6中所示的系统在dfi接口层面的验证内存控制器的装置组成示意图;

58.图8为本技术实施例提供的建模以及验证过程示意图。

具体实施方式

59.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述。

60.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。同时,在本技术的描述中,术语“第一”、“第二”等仅用于区分描述,而不能理解为指示或暗示相对重要性。

61.下面简要阐述本技术一些实施例涉及的英文缩写的含义。

62.ddr5 sdram(或称ddr5内存):第五代双倍数据速率同步动态随机访问存储器,该存储器为计算机系统主内存。

63.sdram mode registers:ddr5 sdram的模式寄存器,模式寄存器用于配置内存颗粒,在ddr5 sdram上每颗内存颗粒有256个模式寄存器。

64.dual channels:ddr5 dimm本身从单通道变为双通道(即两个内存子通道),左右两边的数据总线各为独立的通道。对于ddr5每个dimm将有两个通道,每个通道的宽度为40位。

65.dimm:dual inline memory module,双列直插内存模块。

66.udimm:unbuffered dimm,即无缓冲双列直插内存模块,其地址和控制信号不经缓冲器,无需做任何时序调整,直接到达dimm上的sdram芯片。

67.rdimm:registered dimm,即带寄存器的双列直插内存模块,其在cpu和内存颗粒之间的内存条上加了一个寄存器来寄存指地址和控制信号。

68.lrdimm:load reduced dimm,低负载双列直插内存模块,其不使用比较复杂的寄存器而是使用简单缓冲,缓冲降低了在下层主板上的电力负载,但对能源与内存性能几乎无影响。

69.phy:port physical layer,端口物理层。phy连接一个数据链路层的设备到一个物理媒介。针对ddr5的存储子系统来说,就是连接ddr5内存控制器和ddr5 sdram的中间设备。

70.dfi:ddr phy interface,ddr phy接口,也即内存控制器和phy之间的接口。

71.ecc:error checking and correcting,即错误检查和纠正。ecc内存技术可以检测和纠正一些比特错误,进而提高系统稳定性。

72.cs_n:chip select,rank的片选信号。

73.pda:per sdram addressability,就是单颗内存颗粒访问。

74.uvc:universal verification component,通用验证组件。对uvm来说也即uvm的

验证组件uvm verification component。

75.mpc:multi-purpose command,多目的指令。

76.vrefca:地址线参考电压指令。

77.vrefcs:片选线参考电压指令。

78.ecc:“error checking and correcting”的简写,中文名称是“错误检查和纠正。

79.mrr:mode register read,模式寄存器读。

80.mrw:mode register write,模式寄存器写。

81.下面结合ddr4和ddr5阐述本技术一些实施例所要解决的技术问题。

82.ddr4 sdram内存有mr0~mr7共8个模式寄存器,通过mpr(multi purpose register)间接完成模式寄存器的操作,同时,ddr4 sdram是单通道内存,其在dfi协议接口上的处理方式,是把每个dimm上的内存都归属到同一个单一内存子通道,因此可以理解的是,针对ddr4的把每个dimm上的内存都归属到同一个单一内存子通道的处理方法无法处理ddr5 sdram udimm上分属两个独立的内存通道的情况。

83.ddr5内存控制器是双通道控制器,ddr5 udimm也分为两个内存子通道。实际的ddr存储子系统中,ddr5内存控制器和udimm条中间由ddr phy连接。ddr5 udimm条上的sdram颗粒密度通常有x4、x8和x16三种,在不使能ecc功能时,每个通道分别需要8颗、4颗以及2颗sdram颗粒,而在使能ecc功能时,每个通道则分别需要额外增加2颗、1颗以及1颗sdram颗粒且增加的内存颗粒用于专门存放ecc数据。

84.dr5 sdram内存颗粒具有256个模式寄存器,这256个模式寄存器用来完成对各内存颗粒的模式配置,或者与外部交互内存颗粒的功能状态。ddr5 udimm是双通道(即包括两个内存子通道)的,其rank分属于两个独立的内存子通道。ddr5内存控制器的每个子通道都支持多个rank,这些rank跨越分布在多条udimm上,由位于同一内存子通道的sdram颗粒组成。因此,ddr5内存控制器的每个子内存通道都需要访问多条udimm,并且只能访问每个udimm上对应通道的那些sdram颗粒,不能影响另一个通道的sdram颗粒。

85.本技术的发明人在研究中发现ddr5内存控制器这种跨越多条dimm的特定颗粒、然后归一化到单个内存通道的rank的设计方式,使dfi协议层面的模拟和验证变得复杂困难,基于dfi协议接口的验证组件必须模拟ddr5内存通道跨越多个dimm、跨越dimm正反面、分为两相互独立的个子通道的设计逻辑,以及实现shadow registers或pda等特性。

86.结合上述分析不难发现,ddr4 sdram内存模式寄存器的验证思路,不适合ddr5 sdram内存模式寄存器的建模,缺陷和局限性明显。

87.请参看图1,图1为本技术的一些实施例提供的验证系统,该验证系统包括:待验证的内存控制器1-2、控制器向下接口单元1-3以及内存控制器验证装置2-5。

88.待验证的内存控制器1-2,至少被配置为将用于访问内存颗粒的操作转换到各独立的内存控制器子通道上(内存控制器子通道的数目与要实际访问的内存包括的内存子通道的数目相同,且一个内存控制子通道与一个内存子通道对应设置且相互连通),以最终实现对内存控制器验证装置2-5上模式寄存器的访问和操作。需要说明的是,内存控制器和内存包括的内存颗粒之间所有操作类型包括:数据传输以及状态控制和维护等多种操作,本技术的实施例用于验证内存控制器对内存上模式寄存器的访问以及操作,可以理解的是,访问内存上模式寄存器的操作是“状态控制和维护”操作中的一部分。

89.例如,待验证的内存控制器所要访问的内存包括多个独立的内存子通道时,则该待验证的内存控制器也包括与内存子通道数目相等的子通道,进而使得该待验证的内存控制器通过一个子通道实现对内存的多个rank的访问。

90.控制器向下接口单元,被配置为将所述待验证的内存控制器上包括的各独立的内存控制器子通道连接至相应内存子通道的目标接口协议环境中。例如,内存控制器向下接口单元包括dfi接口单元。

91.内存控制器验证装置2-5,该内存控制器验证装置通过控制器向下接口单元1-3与待验证的内存控制器1-2连接。在本技术的一些实施例中,该内存控制器验证装置2-5至少被配置为:基于单颗内存的模式寄存器建模、在dfi协议(或其他控制器向下的接口协议)层面映射到逻辑通道(例如,一个逻辑通道包括图6的第一指令解码器2-7-1、第一模式寄存器操作指令解析单元2-8-1、第一单内存子通道模型2-9-1以及模式寄存器模块2-23,)、在内存子通道层面实现与内存颗粒对应的模式寄存器的直接访问等验证思维和实现方法。

92.需要说明的是,本技术一些实施例的验证系统可以适用于对udimm、rdimm、lrdimm等进行验证的方案,也可以适用于ddr5 sdram之外的其他设备。例如,通过本技术的一些实施例,可以封装一个待验证的内存控制器、以及其两个子内存通道的模型,模拟真实的内存控制器工作场景。

93.下面首先介绍本技术一些实施例提供的内存模式寄存器建模方法,用于构建如图1的内存控制器验证装置2-5。

94.如图2所示,在本技术的一些实施例中,内存模式寄存器建模方法包括:s101,构建内存中各内存子通道的模式寄存器空间;以及s102,创建用于访问所述模式寄存器空间中包括的目标内存模式寄存器的访问工具。可以理解的是,s101涉及的内存就是待验证的内存控制器实际工作时所要访问的内存,通过构建与实际内存相同的模式寄存器空间可以更好的模拟验证待验证的内存控制器对各模式寄存器的访问操作过程。

95.需要说明的是,s102涉及的访问工具被配置为根据指针访问s101构建的模式寄存器空间包括的目标模式寄存器并完成对目标模式寄存器的至少一种操作,所述至少一种操作包括如下操作中的一种或多种:对所述目标模式寄存器包括的各种字段的读或写操作,对所述目标模式寄存器整体的读或写操作和对影子寄存器访问操作。

96.为了能够快速的访问各rank,在本技术的一些实施例中,s101示例性包括:基于dfi界面,对内存颗粒的空间关系(例如,空间关系包括:位于那个内存条,位于内存条的正面还是反面,位于那个rank上等)建模,并将同一个内存子通道包括的所有构建的与内存颗粒对应的模式寄存器阵列映射到dfi接口对应的虚拟rank模式寄存器阵列上。需要说明的是,这种映射关系需要进行记录(例如,由后续构建的子通道模式寄存器应用方法模块存储该映射关系),且通过这种映射关系,后续在验证过程中可以通过rank访问指针访问位于模式寄存器模块上的目标rank。

97.为了模拟模式寄存器的一些操作,在一些实施例中,在所述创建用于访问所述模式寄存器空间中包括的目标内存模式寄存器的访问工具之后,所述内存模式寄存器建模方法还包括:添加行为模型,并将所述访问工具以及所述行为模型添加至内存子通道模型中,其中,所述行为模型用于模拟至少部分模式寄存器的行为。

98.例如,实际内存的内存颗粒会把其温度状态实时更新刷新到模式寄存器mr4,而把

dqs振荡器的计数值(dram dqs oscillator count)的低位和高位分别更新到mr46、mr47两个模式寄存器中。mr4、mr46、mr47都是只读的,因此只能通过mrr指令来读取。本技术一些实施例在建模时封装行为模型,可以使得当捕捉到对类似mr4、mr46、mr47等寄存器的mrr操作时,构建的内存模式寄存器验证装置可以模拟真实内存颗粒可能的温度或技术状态,从模式寄存器模型返回一个对应的随机数,作为mrr的返回值。

99.也就是说,本技术的一些实施例通过封装的行为模型可以模拟相关的模式寄存器返回一个随机值。这种用于模拟内存颗粒的行为状态的函数也就简称为“行为模型”。

100.在本技术的一些实施例中,在所述将所述访问工具以及所述行为模型添加至内存子通道模型中之后,所述内存模式寄存器建模方法还包括:将所述内存子通道模型和内存控制器进行封装。

101.在一些实施例中,所述对内存颗粒的空间关系建模,包括:创建待构建的模式寄存器的各字段类型以及各字段类型的名称;根据所述各字段类型创建一个模式寄存器,得到构建模式寄存器;根据内存颗粒包括的所有模式寄存器的数量创建多个所述构建模式寄存器,得到内存颗粒模式寄存器组;根据rank上包括的内存颗粒的总数目,创建多个所述内存颗粒模式寄存器组,得到rank模式寄存器组,其中,所述rank位于与待验证的内存控制器实际连接的内存上;根据所述内存包括的各内存子通道类型,创建多个所述rank模式寄存器组,得到内存子通道模式寄存器组,其中,所述内存颗粒、所述rank以及所述内存子通道均位于所述内存上,所述内存为待验证的内存控制器实际所要访问的存取器。

102.在本技术的一些实施例中,所述各字段分别对应不同的比特位数,最长字段的长度等于一个模式寄存器的长度,最短字段的长度为1且字段的总数目与最长字段的长度相同。

103.例如,本技术的一些实施例提供一种通道一致性的ddr5 udimm sdram内存模式寄存器建模方法,该建模方法包括:

104.首先,基于dfi界面,对udimm sdram内存颗粒的空间关系建模,接着把同一个内存通道所属的sdram内存映射到dfi接口对应的rank上,完成单个内存通道的模式寄存器空间的构建。

105.其次,创建ddr5 sdram内存模式寄存器访问工具,添加行为模型,然后封装到内存通道模型中。这些访问工具和行为模型充分解析了sdram内存颗粒的空间关系与内存通道的dfi接口之间的关系,使得内存通道的dfi环境可以简单地直接访问每个sdram的模式寄存器,而不用再关注sdram内存颗粒位置分布的问题。

106.由此,实现了ddr5 udimm sdram内存模式寄存器的通道一致性建模。

107.可以理解的是,通过上述的建模方法能够实现ddr5 sdram模式寄存器的建模和封装;实现ddr5 sdram模式寄存器内存通道建模和封装,便于验证环境中复用;实现ddr5 sdram模式寄存器内存通道模型和ddr5 sdram控制器的封装,便于按内存通道数扩展,便于按内存控制器数量扩展;支持pda功能;支持shadow registers功能;支持x4,x8,x16 devices;支持mr4、mr46、mr47等功能;模型结构支持rdimm和lrdimm的拓展和实现。

108.需要说明的是,后文会以一个已经构建完成的内存控制器验证装置并结合开发程序进一步示例性阐述内存模式寄存器建模方法。为避免重复,对于建模方法的实现细节在此不做过多赘述。

109.下面结合图3示例性阐述已经构建好的内存控制器验证装置2-5的示例性架构。

110.如图3所示,本技术的一些实施例提供一种内存控制器验证装置2-5,该内存控制器验证装置包括:模式寄存器模块2-23以及至少一个访问控制模块2-6-1。

111.模式寄存器模块2-23包括为内存中各内存颗粒分别对应构建的模式寄存器,其中,所述内存是由待验证内存控制器所要实际访问的存储器。

112.需要说明的是,由待验证内存控制器所要实际访问的存储器是指待验证的内存控制器实际工作时需要访问的内存,也就是说非验证环境中待验证内存模式寄存器所要访问的内存。例如,待验证的内存控制器实际访问的内存包括5个内存颗粒,则本技术一些实施例构建的模式寄存器模块2-23包括为这5个内存颗粒分别对应构建的模式寄存器。不难理解的是,通过构建的模式寄存器可以验证待验证的内存控制器的性能,并在性能达到要求后将待验证的内存控制器与内存连接进行实际访问控制。

113.至少一个访问控制模块(如图3的n个访问控制模块,该n个访问控制模块包括:与第一内存子通道对应设置的第一访问控制模块2-6-1,

……

,直至与第n内存子通道对应设置的第n访问控制模块2-6-n),其中,各访问控制模块,被配置为通过指针访问模式寄存器模块2-23上包括的目标模式寄存器。

114.本技术一些实施例不限定访问控制模块所要访问的目标模式寄存器的具体数目。例如,当模式寄存器模块上构建了多个rank(与实际访问的内存包括的所有rank一一对应),在本技术的一些实施例中,目标模式寄存器是位于整个rank上的所有寄存器(正如下文所记载的通过与虚拟rank对应的rank访问指针访问这些模式寄存器)。在本技术的一些实施例中,由访问控制器模块所要访问的目标模式寄存器为一个寄存器。在本技术的一些实施例,目标模式寄存器也可以是与访问控制模块所在的子通道对应的所有模式寄存器。

115.需要说明的是,一个访问控制模块与由待验证内存控制器所要访问的内存的一个内存子通道对应设置,因此本技术的实施例可以根据待验证的内存控制器的数量或者一个待验证的内存控制器包括的内存子通道的数量来确定设置的访问控制模块的数量,可拓展技术方案应用场景。不难理解的是,本技术的一些实施例针对同一内存子通道,在验证过程可以把虚拟rank(即通过访问控制模块中设置的指针)中颗粒设置到实际构建的内存颗粒的模式寄存器(即模式寄存器模块)上,这样可以有效验证内存控制器对各模式寄存器的访问控制操作,且这种设计结构,简化了验证环境访问模式寄存器时所需的处理过程,加快了仿真和调试效率。

116.下面示例性阐述各访问控制模块和模式寄存器模块的示例性结构。

117.不难理解的是,模式寄存器模块上构建的各单元(包括构建的内存条、rank、模式寄存器等)是与待验证的内存控制器所要实际访问的内存结构一致的。

118.在本技术的一些实施例中,由待验证内存控制器所要访问的内存包括n个rank,每个rank包括m个内存颗粒且每个内存颗粒包括l个模式寄存器,则模式寄存器模块2-23示例性包括:构建的n个模式寄存器实例且每个模式寄存器实例包括为所述m个内存颗粒中每个内存颗粒构建的l个模式寄存器,其中,一个模式寄存器实例与一个rank对应设置,n为大于或等于1的整数,m以及l均为大于1的整数。

119.例如,内存为ddr5,该ddr5包括8个rank且每个rank包括10个内存颗粒sdram,每个内存颗粒对应256个模式寄存器,则模式寄存器模块2-23包括构建的8个模式寄存器实例

(与rank对应),且每个模式寄存器实例为所有内存颗粒构建的包括10*256个模式寄存器。

120.也就是说,本技术的一些实施例为内存包括的所有内存颗粒分别构建模式寄存器,且构建针对内存各rank的模式寄存器实例,这种设计结构可以简化验证环境访问模式寄存器时所需的处理过程。

121.在本技术的一些实施例中,由待验证内存控制器所要访问的内存包括a个内存条,且一个内存子通道包括可访问分布于所述a个内存条上共b个rank,则模式寄存器模块包括构建的a个内存条,针对一个内存子通道模式寄存器模块包括构建的b个rank,其中,所述构建的b个rank位于所述构建的a个内存条上,且访问控制模块包括构建的b个虚拟rank,其中,一个虚拟rank对应一个在模式寄存器模块上构建的rank,且每个虚拟rank对应唯一编码,需要说明的是,a和b均为大于或等于1的整数。

122.例如,内存包括两个内存条且包括两个内存子通道,且在一个内存子通道内该内存包括位于两个内存条上的共4个rank,则模式寄存器模块包括构建的两个内存条以及构建的4个rank,构建的4个rank分别位于构建的两个内存条的正面和反面,且访问控制模块包括构建的4个虚拟rank(之所以称为虚拟rank是由于虚拟rank对应的是访问指针,并不实际对应内存空间),一个虚拟rank与一个构建的rank对应,可通过虚拟rank访问与该虚拟rank对应的构建的一个rank。例如,在对待验证内存控制器进行验证时可以通过为各虚拟rank提供的唯一编码来访问各虚拟rank,并最终达到访问构建的一个rank的目的。例如,通过所述编码访问每个虚拟rank,且每个虚拟rank通过rank访问指针访问在模式寄存器模块上一个构建的rank。

123.也就是说,本技术的一些实施例的模式寄存器模块会完全复制实际内存中所有的rank,包括各rank分布的内存条编号,在内存条的正面还是反面等,而访问控制模块不需要构建和内存条相关的要素和信息而只是直接构建与一个内存子通道对应的所有rank的虚拟rank(该虚拟rank与一个rank访问指针对应,通过rank访问指针可访问模式寄存器模块上对应的目标rank,且该虚拟rank包括一组模式寄存器访问指针,通过模式寄存器访问指针可以访问模式寄存器模块上的具体的模式寄存器),且对该虚拟rank唯一编码,通过这种设计方式,可以加快对构建的各rank(即位于模式寄存器模块上的各rank)的访问速度,并最终提升验证速度。本技术的一些实施例通过为虚拟rank分配的编码寻找目标虚拟rank,并通过虚拟rank对应的rank访问指针访问构建的rank(即位于模式寄存器模块上的各rank),这使得对各rank的访问与rank在dimm(即位于模式寄存器模块上的各内存条)上的分布形式无关,从而实现在rank水平上对sdram内存颗粒的直接访问。与相关技术必须先确定要访问的内存条,再确认rank在内存条的正面还是反面等繁琐的操作相比,本技术的实施例显然提升了对rank的访问速度,使得验证过程更加快速。

124.例如,通过为虚拟rank分配的编码访问每个虚拟rank,且每个虚拟rank通过rank访问指针访问所述模式寄存器模块上对应的目标rank。每个虚拟rank包括一组指针,其中,通过各组指针包括的模式寄存器访问指针可访问位于所述模式寄存器模块上的目标模式寄存器。不难理解的是,当来自于待验证的内存控制器的指令是针对某个rank上所有模式寄存器整体的操作时,则只需要获取与目标虚拟rank对应的rank访问指针(该指针是通过查找预先存储的映射表获取的,映射表用于存储各虚拟rank与构建的rank之间的对应关系)来访问目标rank并对目标rank上所有模式寄存器完成目标操作即可。当来自于待验证

的内存控制器的指令是针对某个模式寄存器(即目标模式寄存器)的操作时,则需要获取与目标虚拟rank对应的rank访问指针(该指针是通过查找预先存储的映射表获取的,映射表用于存储各虚拟rank与构建的rank之间的对应关系)并获取目标虚拟rank上存储的模式寄存器访问指针来访问目标模式寄存器完成目标操作。

125.为了精细化对构建的各模式寄存器的访问粒度,在本技术的一些实施例中,位于模式寄存器模块上的各模式寄存器还被配置为包括多种大小不同的字段且各字段分别对应不同的名字,其中,通过各字段的名字访问所述模式寄存器包括的各种字段。也就是说,本技术的一些实施例通过为构建的各模式寄存器定义多种字段从而可以实现对各模式寄存器不同字段的访问,细化了访问粒度,丰富了对待验证的内存控制器的验证参数。后文中会通过程序方式进一步细化各字段的定义过程,为避免重复在此不做过多赘述。

126.为了方便的实现对内存颗粒pda id编码任意组合的测试,在本技术的一些实施例中,所述模式寄存器模块上各内存颗粒序号和pda id编码之间的映射关系可被动态配置。需要说明的是,内存条上每一颗内存颗粒,都有一个唯一的识别编码。内存条在出厂时,产商为每颗内存颗粒都指定了唯一的pda识别码(即pda id),对应到本技术的实施例中模式寄存器模块上与各内存颗粒分别对应建立的模式寄存器也具有该pda识别码,同时,内存控制器可以通过pda枚举(pda enumerate)指令,为每一颗内存重新编写一个新的识别码。本技术的一些实施例正是通过动态配置内存颗粒序号和pda id编码之间的映射,极其方便的实现对内存颗粒pda id编码任意组合的测试。

127.为了验证内存控制器对不同的内存子通道的访问,在本技术的一些实施例中,通过不同识别信号区分所述内存包括的不同内存子通道。

128.在本技术的一些实施例中,访问控制模块包括:指令解码器、模式寄存器操作指令解析单元单内存子通道模型(例如,该单内存子通道模型进一步包括:多个虚拟rank以及子通道模式寄存器应用方法模块)。

129.例如,如图3所示,与第一内存子通道对应设置的第一访问控制模块2-6-1包括:第一指令解码器2-7-1、第一模式寄存器操作指令解析单元2-8-1以及第一单内存子通道模型2-9-1。第n访问控制模块2-6-n包括:第n指令解码器2-7-n、第n模式寄存器操作指令解析单元2-8-n以及第n单内存子通道模型2-9-n。需要说明的是,各内存子通道的访问控制模块的结构相同,以下仅以第一内存子通道的第一访问控制模块为例示例性阐述访问控制模块的结构。

130.第一指令解码器2-7-1至少被配置为根据接口协议对接口信号进行解析获取内存颗粒操作指令,其中,所述接口协议是所述待验证的内存控制器的向下接口单元所采用的协议。例如,在一些实施例中该向下接口单元为dfi接口,对应的协议为dfi接口协议。

131.第一模式寄存器操作指令解析单元2-8-1被配置为:对所述内存颗粒操作指令进行解析,获取解析结果;根据所述解析结果进行指令筛选得到与模式寄存器操作相关的目标操作指令。例如,当内存为udimm内存,这些目标操作指令包括:mpc、mrw、mrr、vrefca等。可以理解的是,在这些实施例中,第一模式寄存器操作指令解析单元2-8-1包括所有需要和模式寄存器互动的命令处理单元,例如,包括mpc命令处理单元、mrw命令处理单元、mrr命令处理单元、vrefca/vrefcs命令处理单元以及监测是否在pda状态的pda监控模块。

132.第一单内存子通道模型2-9-1至少包括多个虚拟rank(图3未示出,可以参考图7b

的虚拟rank0 2-11-1、虚拟rank1 2-12-1等)以及子通道模式寄存器应用方法模块(图3未示出,可以参考图7b的channel register utilities 2-24-1),且所述虚拟rank被配置为通过rakn访问指针或位于各虚拟rank上的模式寄存器访问指针访问位于模式寄存器模块上的目标模式寄存器,以使所述待验证内存控制器完成针对所述目标模式寄存器的所述目标操作。

133.在一些实施例中,上述子通道模式寄存器应用方法模块至少包括:与模式寄存器的所有操作指令对应的实现函数,以及从内存子通道到目标内存颗粒之间的逻辑转换映射表,其中,通过查找所述逻辑转换映射表获取所述目标模式寄存器在所述模式寄存器模块上的分布位置,通过与所述目标操作对应的实现函数完成所述目标操作。

134.例如,子通道模式寄存器应用方法模块被配置为:获取与所述目标操作对应的目标虚拟rank,并根据与所述目标虚拟rank对应的rank访问指针访问位于所述模式寄存器模块上的目标rank,完成对所述目标rank上所有模式寄存器的所述目标操作;或者,获取与所述目标操作对应的目标虚拟rank和目标模式寄存器,通过与所述目标虚拟rank对应的rank访问指针访问目标rank,并通过所述目标虚拟rank包括的模式寄存器访问指针访问所述目标rank上的所述目标模式寄存器,完成对所述目标模式寄存器的所述目标操作。

135.为了丰富对待验证的内存控制器的验证内容,在本技术的一些实施例中,所述内存控制器验证装置还包括设置的影子寄存器(图中未示出),其中,若通过所述模式寄存器操作指令解析单元确认处于pda状态,则所述子通道模式寄存器应用方法模块还被配置为通过所述影子寄存器和所述目标模式寄存器实现与所述影子寄存器对应的目标操作。需要说明的是,模式寄存器操作指令解析单元是确认内存条上某一个rank所包含的至少部分内存颗粒处于pda状态。

136.例如,模式寄存器操作指令解析单元会根据解码出的指令,判断当前是否在pda状态。ddr5的部分内存模式寄存器比较特殊,只能通过vrefca、vrefcs、mpc的set rtt_ca/cs/ck等指令来完成写入。这些指令尝试写入这些模式寄存器时,实际上是先把数据写入到一个临时寄存器中。在没有发出mpc加上8’b0001_1111的操作字之前,这些模式寄存器的值并没有立即更新,如果做读取操作,返回的都是之前的数值;而只有等到发出mpc加上8’b0001_1111的操作字时,内存颗粒才会临时寄存器中的值,逐一写入到对应的模式寄存器中,之后再做读取操作的话,返回的才是真正的最新写入的数值,这些临时寄存器,也叫影子寄存器,其访问方法和普通模式寄存器一样。例如,在本技术的一些实施例中,为影子寄存器构建了和模式寄存器模块2-23完全一样的规格,以便于实现从影子寄存器向普通寄存器的赋值操作;同时,在本技术的一些实施例中子通道模式寄存器应用方法模块封装了从影子寄存器到模式寄存器的操作,使得验证时只需要简单调用相关方法函数即可完成对目标寄存器的赋值和操作,而不用考虑影子寄存器到目标寄存器的细节,从而大大简化了验证的复杂度。需要说明的是,本技术的附图并未标注出影子寄存器的部分,但是这并不影响本领域技术人员对技术方案的理解。

137.为了避免待验证的内存控制器访问禁止访问的模式寄存器,在本技术的一些实施例中,子通道模式寄存器应用方法模块还被配置当确认所述目标模式寄存器属于禁止访问的模式寄存器时,则会生成错误提示信息。

138.可以理解的是,子通道模式寄存器应用方法模块属于访问工具,这个访问工具封

装所有和模式寄存器相关的操作,包括模式寄存器字或域(field)级别的读、写操作,模式寄存器(register)级别的读、写操作,以及影子寄存器访问操作等。子通道模式寄存器应用方法模块还封装了映射表,可以根据映射表获取由模式寄存器操作指令解析单元筛选出的目标操作所针对的目标模式寄存器在模式寄存器模块上的具体位置,并通过rank访问指针和模式寄存器访问帧访问所述目标模式寄存器,并实现对目标模式寄存器的目标操作。例如,目标操作为mrr且该目标操作针对的是第一内存条上背面的一个rank上的所有模式寄存器的操作,则子通道模式寄存器通过查找映射表可以得到目标操作所针对的模式寄存器的具体位置,获取目标操作针对的虚拟rank,并根据与虚拟rank对应的rank访问指针访问目标rank并完成模式寄存器读操作。

139.也就是说,本技术的一些实施例通过为每个内存子通道设置的指令解码器、模式寄存器操作指令解析单元以及单内存子通道模型可以使得各逻辑通道能够独立的访问内存颗粒。

140.需要说明的是,上述仅示例性描述了第一指令解码器、第一模式寄存器操作指令解析单元以及第一单内存子通道模型,而其它访问控制模块上包括的指令解码器、模式寄存器操作指令解析单元以及单内存子通道模型的功能与对应单元的功能类似,为避免重复不对其他模块做出过多赘述。

141.下面结合具体的内存颗粒指令类型示例性阐述模式寄存器操作指令解析单元的结构。

142.在本技术的一些实施例中,上述接口协议为dfi协议,上述内存为udimm,则模式寄存器操作指令解析单元还被配置为:通过检测所述内存颗粒操作指令筛选得到mpc指令,并获得mpc指令解析结果;若根据所述mpc指令解析结果确认处于pda操作状态,则根据所述pda操作状态得到所述目标模式寄存器。

143.也就是说,本技术的一些实施例通过设置的模式寄存器操作指令解析单元还可以完成pda操作状态下的各种模式寄存器操作指令,更全面的验证了内存控制器的性能。

144.为了筛选出尽可能多的模式寄存器相关的操作指令,以更加全面的验证内存控制器对模式寄存器的访问过程,在本技术的一些实施例中,模式寄存器操作指令解析单元,包括:多个目标类型指令筛选单元,其中,所述多个目标类型指令筛选单元中的各单元被配置为从所述内存颗粒操作指令中筛选得到任一目标类型的模式寄存器操作指令。本技术的一些实施例通过设置的多类指令筛选单元可以更全面的验证内存控制器对模式寄存器的各类操作。

145.具体地,在本技术的一些实施例中,如图4所示,若所述内存为udimm时,所述多个目标指令筛选单元包括:mpc命令处理单元,输入端与所述指令解码器的输出端连接(用于接收输入的ddr5 commands),且被配置为从所指令解码器的输出结果中获取mpc指令,并解析所述mpc指令得到mpc指令解析结果;mrw命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出mrw指令,并解析所述mrw指令得到mrw指令解析结果;mrr命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出mrr指令,并解析所述mrr指令得到mrr指令解析结果;vrefca/vrefcs命令处理单元,与所述mpc命令处理单元的输出端连接,且被配置为从输入信号中检测出vrefca和/或vrefcs指令,并解析所述vrefca和/或vrefcs指令得到vrefca和/或vrefcs指令解析结果。

146.本技术的一些实施例可以完成针对udimm类型内存的包括mpc命令在内的多种命令的验证。

147.在本技术的一些实施例中,如图5所述接口协议为dfi协议,所述模式寄存器操作指令解析单元还包括:pda监控模块(即图4的pdamonitor),被配置为确认内存(或者内存条上某个rank所包含的所有内存颗粒)处于pda操作状态;其中,所述mpc命令处理单元(即图5的mpc)的输出端与所述pda监控模块的输入端连接其中,所述pda监控模块通过所述mpc指令解析结果确认处于所述pda操作状态;所述mrw命令处理单元(即图5的mrw)的输入端与所述pda监控模块的输出端连接;所述mrr命令处理单元(即图5的mrr)的输入端与所述pda监控模块的输出端连接;所述vrefca/vrefcs命令处理单元(即图5的vrefca vrefcs)的输入端与所述pda监控模块的输出端连接。需要说明的是,这些连接可以是基于总线的连接。

148.本技术的一些实施例单独设置的功能模块即pda监控模块确认处于pda操作状态,可以对待验证内存控制器进行更加完整的性能验证。

149.下面结合图6和图7a和图7b示例性阐述本技术一些实施例提供的内存控制器验证系统(包含内存控制器验证的装置)的结构。图7a和图7b是以内存控制器有两个内存子通道为例呈现(即,图7a的两个输出分别通过第一连线2-5-1以及第二连线2-5-2分别与图7b的部分进行通信,具体地图7a的第一dfi通道1-3-1输出通过第一连线2-5-1与图7b对应内存子通道通信,图7a的第二dfi通道1-3-2输出通过第二连线2-5-2与图7b另一内存子通道通信),因此,可以封装一个待验证的内存控制器、以及其两个子内存通道的模型,模拟真实的内存控制器工作场景(即模拟图6的工作场景)。

150.图6示例性提供一种实际中内存控制器(即ddr5 sdram controller)、内存物理接口phy以及内存dram内存之间的系统构成。与图6不同的是,图7a和图7b是采用本技术的一些实施例提供的验证内存控制器的装置与图6的内存控制器连接组成的验证内存控制器系统。

151.在图6中,每个ddr5内存控制器具有两个内存子通道,每个内存子通道支持4个rank,且由内存控制器访问的内存是以x8密度的内存颗粒类型。需要说明的是,当使用x4密度的内存颗粒类型时,图6第一内存条dimm0和第二内存条dimm1上面的内存颗粒数量要增加一倍,当使用x16密度的颗粒时,每条内存条dimm上面只需要8颗颗粒。

152.系统总线1-1(即图6的system bus)用于连接处理器(例如,cpu)和内存控制器1-2,通过该连接可以完成处理器和内存控制器之间指令和数据的传输。

153.内存控制器1-2(即图6的ddr5 sdram controller 0)被配置为生成各内存控制器子通道的操作信号,且该内存控制器具有两个独立的内存控制器子通道,即第一内存控制器子通道1-2-1(即图6的sub-channel a)和第二内存控制器子通道1-2-2(即sub-channel b),这些内存控制器子通道的功能在于将操作信号转换为相应的接口信号,这是由于该内存控制器所要访问的内存为ddr5,而ddr5是双通道的。

154.不难理解的是,一方面,内存控制器1-2需要将系统总线的指令和数据转换成对内存子通道的相关内存颗粒的指令和数据,另一方面,内存控制器也会把内存子通道的内存颗粒的数据和状态返回给系统总线。

155.内存物理接口1-4(即图6的端口物理层phy0)是数据链路层的物理媒介,该内存物理接口用于连接内存控制器1-2和第一内存条1-11(即图6的dimm0),并连接内存控制器1-2

和第二内存条1-17(即图6的dimm1)。内存物理接口1-4也分为两个通道,内存物理接口第一内存物理接口子通道1-4-1和第二内存物理接口子通道1-4-2。

156.内存控制器第一内存控制器子通道1-2-1完成内存控制器到第一内存子通道之间的指令发送、数据访问或状态维护等。第一内存控制器子通道通过第一dfi通道1-3-1(即图6的dfi_controller0_channel_a)连接第一内存物理接口子通道1-4-1。

157.第二内存控制器子通道1-2-2完成内存控制器到第二内存子通道之间的指令发送、数据访问和状态维护等。第二内存控制器子通道通过第二dfi通道1-3-2(即图6的dfi_controller0_channel_b)连接第二内存物理接口子通道1-4-2。

158.第一内存条1-11和第二内存条1-17都是内存控制器要访问的内存单元dimm,俗称内存条。dimm也叫双列直插内存模块,在一个基板上面安装了多颗dram内存颗粒,用于存储数据。以ddr5每个内存子通道支持4个rank为例,每个dimm有两个rank,所以内存控制器1-2总共需要两个dimm,如第一内存条1-11和第二内存条1-17。

159.如图6所示,第一内存条dimm0有第一内存条正面1-8(即图6的front side)和第一内存条反面1-10(即图6的back side)。第一内存条正面1-8包含从第一个内存颗粒1-6-1到第十个内存颗粒1-6-2(图6仅标出了这两个内存颗粒),总共10个内存颗粒,这10个内存颗粒在第一内存条正面按左右两边5个一组,分别属于第一内存条正面第一内存子通道1-7-1和第一内存条正面第二内存子通道1-7-2。第一内存条反面1-10也有总共10个内存颗粒,这10个内存颗粒在该第一内存条反面按左右两边5个一组,分别属于第一内存条反面第一子通道1-9-1和第一内存条反面第二子通道1-9-2。

160.第二内存条dimm1有第二内存条正面1-14和第二内存条反面1-16,其中,第二内存条正面1-14包含从第一个内存颗粒1-12-1到第十个内存颗粒1-12-2,总共10个内存颗粒,这10个内存颗粒在第二内存条正面按左右两边5个一组,分别属于第二内存条正面第一子通道1-13-1和第二内存条正面第二子通道1-13-2。第二内存条反面1-16也有总共10个内存颗粒,这10个内存颗粒在该第二内存条反面按左右两边5个一组,分别属于第二内存条反面第一子通道1-15-1和第二内存条反面第二子通道1-15-2。

161.第一内存物理接口子通道1-4-1通过第一ddr5 sdram接口1-5-1完成对4个rank的访问(包括图5左半部分的rank0、rank1、rank2以及rank3),这4个rank跨越第一内存条dimm0和第二内存条dimm1并且都属于同一个内存子通道,分别是:

162.第一内存条正面第一内存子通道1-7-1对应于第一内存条dimm0的内存颗粒sdram0/1/2/3/8,组成rank0。

163.第一内存条反面第一内存子通道1-9-1对应于第一内存条dimm0的内存颗粒sdram7/6/5/4/9,组成rank1。

164.第二内存条正面第一内存子通道1-13-1对应于第二内存条dimm1的内存颗粒sdram0/1/2/3/8,组成rank2。

165.第二内存条反面第一内存子通道1-15-1对应于第二内存条dimm1的内存颗粒sdram7/6/5/4/9,组成rank3。

166.需要说明的是,上述第一内存条正面第一内存子通道1-7-1、第一内存条反面第一内存子通道1-9-1、第二内存条正面第一内存子通道1-13-1以及第二内存条反面第一内存子通道1-15-1均属于第一内存子通道(或称为sub-channela)。

167.同理,第二内存物理接口子通道1-4-2通过第二ddr5 sdram接口1-5-2完成对4个rank的访问(包括图6右半部分的rank0、rank1、rank2以及rank3),这四个rank跨越第一内存条dimm0和第二内存条dimm1并且都属于同一个内存子通道,分别是:

168.第一内存条反面第二内存子通道1-7-2对应于第一内存条dimm0的内存颗粒sdram9/4/5/6/7,组成rank0。

169.第一内存条反面第二内存子通道1-9-2对应于第一内存条dimm0的内存颗粒sdram8/3/2/1/0,组成rank1。

170.第二内存条正面第二内存子通道1-13-2对应于第二内存条dimm1的内存颗粒sdram9/4/5/6/7,组成rank2。

171.第二内存条反面第二内存子通道1-15-2对应于第二内存条dimm1的内存颗粒sdram8/3/2/1/0,组成rank3。

172.需要说明的是,上述第一内存条反面第二内存子通道1-7-2、第一内存条反面第二内存子通道1-9-2、第二内存条正面第二内存子通道1-13-2以及第二内存条反面第二内存子通道1-15-2均属于第二内存子通道(或称为sub-channelb)。

173.由此可见,图6的每个内存子通道所访问的内存颗粒,跨越了多个dimm条(dimm0和dimm1)、跨越了dimm条的正反两面(back side和front side)、跨越了dimm条的左右两侧(left side和right side)。可以理解的是,每个内存子通道还必须实现对单颗内存颗粒(即图6的每个sdram单元)的访问,比如shadow registers、pda等特性。因此,内存控制器需要复杂的逻辑设计,才能实现内存子通道对内存颗粒的访问。为了验证内存控制设计的用于访问内存颗粒的逻辑是否准确,需要对待验证的内存控制器进行内存颗粒访问逻辑的验证,使得设计的内存控制器的模式寄存器访问逻辑准确,这也是本技术一些实施例所要解决的技术问题。

174.当从dfi接口层面(图6的dfi_controller0_channel_a或dfi_controller0_channel_b)对内存控制器进行验证时,任何需要访问内存颗粒模式寄存器的地方则验证装置都需要处理上述内存颗粒与内存通道之间的映射关系,从而让验证变得复杂。因此,亟需一种创新方案,使得验证内存控制器的装置能够简化对模式寄存器的操作,实现内存通道和内存颗粒之间的一致性。

175.下面结合图7a和图7b示例性阐述本技术的一些实施例提供的验证内存控制器的装置的结构,该装置可以用于验证在图7a环境中工作的内存控制器的性能。与图6不同的是,图7b上的内存条以及内存条上的模式寄存器都是模拟生成的。通过图7b的模型可以验证待验证的内存控制器对内存颗粒对应的模式寄存器的访问性能。也就是说,图6中描述的是实际的物理连接示意图,图7b表述的是验证环境中对内存条的建模形式,图7b中的模式寄存器都是testbench通过程序代码来模拟的真实内存条的模式寄存器。

176.如图7a和图7b所示,该图示例性提供了基于dfi测试环境dfi testbench environment开发的controller0_uvc(即内存控制器验证装置2-5)。图7b的内存控制器验证装置包括与单颗内存颗粒对应的单内存颗粒模式寄存器组2-16-1(该模式寄存器组包括256个模式寄存器)、构建的与内存上rank对应的单rank模式寄存器组2-17-1(即单rank模型)、模式寄存器模块2-23(即图7的model of sdram registers for dual dimm,该模块包括多dimm物理模型)、构建的单内存子通道的单内存子通道模型(例如,与第一内存子通道

对应建立的第一单内存子通道模型2-9-1,该模型对应于图7b的virtual logical model of sub-channel a),模式寄存器的多dimm物理模型到内存子通道之间的映射算法(即图7b上左右两侧各四条带双向箭头的粗实线的算法),dfi接口对模式寄存器的控制方法(包括mrw、mrr、vrefca、vrefcs或mpc等指令,shadow registers功能,pda功能等等)。

177.请参考图7a和图7b,本技术一些实施例的验证内存控制器的系统包括:

178.系统总线1-1(即图7a的system bus)以及待验证的内存控制器1-2(即图7a的ddr5 sdram controller 0)。需要说明的是,为避免重复针对图7a和图7b与图6相同的附图标记对应的内容不做过多赘述,下面重点示例性阐述验证内存控制器的装置2-5的示例性结构。

179.dfi顶层验证环境2-4(即图7b的dfi testbench environment)包括验证内存控制器环境或称为验证内存控制器的装置2-5(即图7b的controller0_uvc),该装置用来模拟真实的内存物理接口phy和内存条的行为,使得验证工作得以脱离对实际的内存物理phy和对实际内存条模型的依赖。

180.内存控制器验证的装置2-5包括:第一内存子通道2-6-1的验证环境(即一个内存子通道对应的访问控制模块)、第二内存子通道2-6-2的验证环境(即另一个内存子通道对应的又一访问控制模块)以及模式寄存器模块2-23(该模型用于构建待验证内存控制器所要访问的内存上全部dimm sdram的模式寄存器模型)。需要说明的是,各访问控制模块的结构是一样的。

181.第一内存子通道的验证环境2-6-1(对应于图7b的dfi_env_channel_a)用来模拟内存物理接口phy和内存条dimm在第一内存子通道(或称为内存子通道a)上的响应,该第一内存子通道的验证环境2-6-1包括第一dfi指令解码器2-7-1(作为指令解码器的一个具体示例)、第一内存通道模型的访问器2-8-1(作为模式寄存器操作指令解析单元的一个具体示例)以及第一单内存子通道模型2-9-1(包括多个虚拟rank以及子通道模式寄存器应用方法模块)。需要说明的是,各单内存子通道模型用于实现dfi接口对模式寄存器的控制方法。

182.例如,当内存控制器通过内存子通道访问模式寄存器时,内存控制器验证装置首先把该内存子通道的操作,分配到对应的内存子通道的虚拟rank上;然后通过图7b的子通道模式寄存器应用方法模块2-24-1channel register utilities,实现对真实的内存颗粒模式寄存的映射和访问。子通道模式寄存器应用方法模块2-24-1既封装了模式寄存器的所有操作指令,又封装了从子内存通道到具体内存颗粒之间的逻辑转换,从而使得testbench只需要简单的调用相关功能函数,避免频繁地转换内存通道到具体的内存条、正反面、左右子通道的空间关系。

183.第二内存子通道的验证环境2-6-2(对应于图7b的dfi_env_channel_b)用来模拟内存物理接口phy和内存条dimm在第二内存子通道上的响应,该第二内存子通道的验证环境2-6-2包括第二dfi指令解码器2-7-2(作为指令解码器的一个具体示例)、第二内存通道模型的访问器2-8-2(作为模式寄存器操作指令解析单元的一个具体示例)以及第二单内存子通道模型2-9-2(包括多个虚拟rank以及子通道模式寄存器应用模块)。

184.第一dfi指令解码器2-7-1(对应于图7b的decode ddr5 sdram command)用于对dfi接口的信号进行解析得到待验证的内存控制器当前对内存颗粒dram的操作指令,该第一dfi指令解码器2-7-1的输入包括dfi接口中的片选信号cs_n和地址ca[13:0],输出是解码后的得到的针对ddr5的操作指令(例如,该第一指令解码器根据输入多位信号的电压特

征通过查找操作指令映射表得到当前操作指令)。例如,这些操作指令示例性包括:激活指令active、rfu指令、模式寄存器写指令(即model register write)或模式寄存器读指令(即model register read)、mpc指令、verfca指令、verfcs指令、读指令或者写指令等。可以理解的是,这些操作指令中有一些是针对模式寄存器的操作(例如,模式寄存器写指令mrw、模式寄存器读指令mrr、mpc指令),而另一些不是针对模式寄存器的操作(例如,读指令或者写指令等),因此本技术的实施例为了更好的验证待验证的内存控制器对模式寄存器的访问或者操作仅需要关注和模式寄存器相关的操作指令即可。

[0185]

需要说明的是,这里的dfi接口是ddr5的dfi5.0或者dfi5.1,其信号包括:命令接口信号(即command interface signals)、写数据接口信号(即write data interface signals)、读数据接口信号(即read data interface signals)、更新接口信号(即update interface signals)和状态接口信号(即status interface signals)等。

[0186]

第二dfi指令解码器2-7-2与第一dfi指令解码器2-7-1功能一样,因此对于该解码器的功能和结构可以参考前述对第一dfi指令解码器2-7-1的相关描述,为避免重复在此不做过多赘述。

[0187]

第一内存子通道模型的访问器2-8-1(即对应图7b的proces command to sdram model register)用于监测与其连接的dfi指令解码器输出的操作指令,若该访问器监测到与模式寄存器操作相关的操作指令(例如,pda、mrr、mrw、mpc、vrefca、vrefcs、shadow register等功能相关的操作指令)时,则立即调用该内存通道寄存器模型中由子通道模式寄存器应用模块提供的方法(即由channel register utilities模块提供的方法)把模式寄存器相关的操作指令匹配到对应的目标模式寄存器上。需要说明的是,子通道模式寄存器应用方法模块channel register utilities提供的方法,解析了当前操作应该发生在dimm0/1中的哪个内存条、front side和back side中的哪个面、left side和right side中的哪一边(哪个内存子通道)、单个rank中的哪个内存颗粒,从而使得testbench仅仅需要知道当前访问的rank即可,大大简化了testbench的复杂度。

[0188]

需要说明的是,第一内存通道模型的访问器2-8-1的输入是相应dfi指令解码器输出的所有操作指令,其输出是筛选得到的与模式寄存器操作相关的所有目标操作指令。例如,目标操作指令包括mpc指令、mrw指令等。

[0189]

可以理解的是,第二内存通道模型的访问器2-8-2与第一内存通道模型的访问器2-8-1结构和功能类似,为避免重复在此不做过多赘述。

[0190]

第一单内存子通道模型2-9-1(即图7b的virtual logical model of sub-channel a)指向第一内存子通道的虚拟内存模式寄存器通道模型,该模型中实现一种数据结构,其声明其他数据类型的引用,完成对相应数据实体(即模式寄存器模块上构建的各模式寄存器、或者构建的各rank)的引用,节约内存消耗,提升仿真速度。这些数据结构引用,即包括单颗粒寄存器模型引用(例如,可以访问图7b示出的每个内存颗粒包括的256个模式寄存器mr[0:255]中的任意一个),也可以包括其他类型的数据结构引用(例如,可以访问相应内存子通道内的任意一个rank上的所有模式寄存器)。第一内存子通道的虚拟内存寄存器通道模型声明了该通道包含的所有内存颗粒的模式寄存器引用,同时对应地组合到四个虚拟rank上,分别是:

[0191]

第一内存子通道可访问的第一虚拟逻辑模块2-11-1包括的sdram0/1/2/3/8,组成

第一单内存子通道模型2-9-1对应子通道的虚拟rank0。

[0192]

第一内存子通道可访问的第二虚拟逻辑模块2-12-1包括的sdram7/6/5/4/9,组成第一单内存子通道模型2-9-1对应子通道的虚拟rank1。

[0193]

第一内存子通道可访问的第三虚拟逻辑模块2-14-1包括的sdram0/1/2/3/8,组成第一单内存子通道模型2-9-1对应子通道的虚拟rank2。

[0194]

第一内存子通道可访问的第三虚拟逻辑模块2-15-1包括的sdram7/6/5/4/9,组成第一单内存子通道模型2-9-1对应子通道的虚拟rank3。

[0195]

第二单内存通道模型2-9-2指向第二内存子通道的虚拟内存模式寄存器通道模型。相应地,其声明的模式寄存器引用对应下面的四个虚拟rank,分别是:

[0196]

第二内存子通道可访问的第一虚拟逻辑模块2-11-2包括的sdram0/1/2/3/8,组成第二单内存子通道模型2-9-2对应子通道的虚拟rank0。

[0197]

第二内存子通道可访问的第二虚拟逻辑模块2-12-2包括的sdram7/6/5/4/9,组成第二单内存子通道模型2-9-2对应子通道的虚拟rank1。

[0198]

第二内存子通道可访问的第三虚拟逻辑模块2-14-2包括的sdram0/1/2/3/8,组成第二单内存通道模型2-9-2对应子通道的虚拟rank2。

[0199]

第二内存子通道可访问的第四虚拟逻辑模块2-15-2包括的sdram7/6/5/4/9,组成第二单内存通道模型2-9-2对应子通道的虚拟rank3。

[0200]

第一子通道模式寄存器应用模块2-24-1(对应于图7b的channel register utilities)用于实现第一单内存子通道模型2-9-1对模式寄存器的访问方法,用于对待验证的内存控制器的当前模式寄存器操作指令所针对的内存子通道和目标rank进行解析,根据解析结果访问在模式寄存器模块2-23上单个模式寄存器或者多个模式寄存器(例如位于同一rank上的所有模式寄存器)并对该模式寄存器执行相关操作。可以理解的是,该处的操作是由第一内存通道模型的访问器2-8-1输出的操作指令。

[0201]

第二子通道寄存器应用模块2-24-2与第一子通道寄存器应用模块2-24-1结构和功能类似,为避免重复对其不做过多赘述。

[0202]

模式寄存器模块2-23(对应于图7b的model of sdram register for dual dimms)包括所有dram内存颗粒的模式寄存器建模实例(即图7b的sdrami对应的各小方块上标注的m[0:255],i取值为从0到9),该模式寄存器模块构建了由待验证的内存控制器1-2所要访问的所有dimm,所有rank上包括的全部模式寄存器模型。也就是说,图6的模式寄存器模块2-23构建的第一内存条dimm0和第二内存条dimm1上的包括全部内存颗粒的所有模式寄存器。

[0203]

下面分别说明为第一内存子通道和第二内存子通道构建的四个rank与图6实际内存条上分布的实际rank的对应关系,对应关系如下:

[0204]

图7b构建的第一内存子通道上的rank0 2-17-1对应图6第一内存条dimm0的front side 1-8的rank0,具体的对应图6的第一内存条上rank0上第一内存子通道的rank 0 1-7-1包括的sdram0/1/2/3/8。

[0205]

图7b构建的第一子内存通道rank 1 2-18-1对应图6第一内存条的back side 1-10的第一内存子通道rank1,具体地对应图6第一内存条上第一内存子通道的rank1 1-9-1包括的sdram7/6/5/4/9。

[0206]

图7b构建的第一子内存通道rank 2 2-20-1对应图6第一内存条dimm0 1-11第一内存子通道front side的rank2,具体地对应图6第一内存条上第一内存子通道的rank2 1-13-1包括的sdram0/1/2/3/8。

[0207]

以此类推,可以理解的是,图6实际内存的每一个rank和每一个内存颗粒对应的模式寄存器均在图7b的模式寄存器模块2-23找到对应单元。也就是说,图7b的模式寄存器模块2-23模拟了实际内存上所有的rank和各rank上内存颗粒的模式寄存器。

[0208]

下面通过程序示例性阐述如何构建如图7b所示的本技术一些实施例的验证内存控制器的装置。如下图所示:

[0209]

3.1创建轻量级的模式寄存器字类型(即field类型simple_reg_field)。

[0210]

ddr5 sdram的内存颗粒规模很大,x8类型带ecc功能每个rank需要5颗内存颗粒,每个内存子通道支持4个rank因此共需20颗内存颗粒,单个内存控制的两个内存子通道总共需要40颗内存颗粒,如图5所示。x4类型带ecc功能每rank需要10颗内存颗粒,每个内存通道支持4个rank因此共需40颗内存颗粒,单个内存控制的两个内存子通道总共需要80颗内存颗粒。x16类型颗粒不使能ecc,每个内存通道支持4个rank共需8颗内存颗粒,单个内存控制的两个子通道总共需要16颗内存颗粒。

[0211]

ddr5 sdram每颗内存颗粒都有256个8-bits的模式寄存器,当为之建模时,x8类型总共需要40x256=10240个模式寄存器;x4类型需要80x256=20480个模式寄存器;x16类型需要16x256=4096个模式寄存器。每个模式寄存器可能有多个字段field,而且字段彼此之间的读写属性、初始值、响应方式等都不相同。

[0212]

为了降低建模的内存消耗,加快仿真速度,本技术的一些实施例提出一种快速的寄存器字段类型field,以便复用与构建模式寄存器类型。考虑到这是基于dfi接口的验证应用需求,以及ddr5 sdram内存颗粒模式寄存器的常用读写访问类型,本技术一些实施例的字段类型field包括针对各字段的:读、写、读写属性、边界检查、register和field两级同步、名称设定等方法,相比uvm的内置方法,更加简单高效。需要说明的是,这些字段都是根据ddr5协议中对模式寄存器的描述而声明、定义的。本技术的一些实施例为每个字段都定义了唯一的名字,因此验证时可以按照字段名字来访问相应字段。设置不同的字段,可以方便精确访问对应的字段,提高效率,精准控制。所述两级同步指的实现字段和整个寄存器之间的同步刷新。例如,改写了模式寄存器的某个字段后,整个模式寄存器的值也要立即同步更新;而改写整个模式寄存器的值,那么该寄存器中的每个字段的值,也要立即同步更新。

[0213]

具体方法及示意代码如下:

[0214][0215]

(1).声明字段类型field的基本属性,包括:

[0216]

field所属的模式寄存器mode register的名称reg_name,字段field的名字field_name和字段值field_val,字段field的读写属性access_type,字段field的起始地址field_lsb和截止地址field_msb,字段默认值field_val_def。

[0217]

也就是说,本技术的一些实施例为模式寄存器模块2-23上构建的每个模式寄存器都设置如上所述的“读、写、读写属性、字段地址范围名称设定”这些字段。

[0218]

(2).实现字段field的写new(),field_write(),读field_read()等功能;

[0219]

field的new(),是用过field_lsb和field_msb获得访问的具体的bits范围,然后通过寄存器值的引用reg_val,把字段默认值field_val_def写入到对应的比特位bits里。需要说明的是,字段默认值是ddr5协议中规定的默认数值,而字段值指的是本技术一些实施例在声明字段时,可以自主写入其他值。

[0220]

field的写field_write(),是通过filed_name做索引获得访问的具体的bits范围,然后通过寄存器值的引用reg_val,把字段值field_val写入到对应的比特位bits里。需要说明的是,reg_val也就是模式寄存器的8个bits所对应的值,如果一个8bits的模式寄存器包含多个字段,那么某个字段的值field_val只是reg_val的一部分。

[0221]

field的读field_read(),是通过filed_name做索引获得访问的具体的bits范围,然后通过寄存器值的引用reg_val,把reg_val中对应的bits的值读出到field_val。

[0222]

(3).实现field边界检查。

[0223]

确保字段声明时field_lsb和field_msb都在模式寄存器mr bit0到bit7的8-bits空间内,同时,字段值field_val以及字段默认值field_val_def不应该超出bits[field_msb-field_lsb:field_lsb]所能表达的值域。

[0224]

也就是说,当为一个模式寄存器声明字段时,每个字段所占用的空间都逐个排列,所有字段的空间不能超过一个模式寄存器的总的8bits的空间。

[0225]

(4).实现对读写属性access_type的检查和兼容性操作,详情如下:

[0226]

ddr5 sdram模式寄存器主要有只读r、只写w、可读可写r/w、读置位可写sr/w或保留rfu,其中,

[0227]

只读r:field_read()可以把其值读出,不可写入field_write()。

[0228]

只读w:field_write()可以把值写入,不可读出field_read()。

[0229]

可读可写r/w:field_read()可以把其值读出,field_write()可以把值写入。

[0230]

读置位可写sr/w:field_read()可以把其值读出,然后该field的所有bits都要被置位为1,field__write()可以把值写入;

[0231]

保留rfu:保留给将来使用的字段field。内存控制器会忽略这些rfu的bits,为了避免往dram中写入不支持的值,上层的寄存器mode register在调用field_write()时必须对rfu field写入全零,field在field_read()时必须返回field的全部bits为零。

[0232]

3.2基于简单寄存器field类型simple_reg_field,创建简单模式寄存器类型simple_register。即构建模式寄存器模块2-23上各内存颗粒的256个模式寄存器中的任何一个。

[0233]

主要创建模式寄存器的读写、重置等操作,具体方法及示意代码如下:

[0234]

[0235]

具体方法为:

[0236]

(1).声明寄存器simple_register类型的基本属性,包括:

[0237]

当前单个模式寄存器所属的分组名称,也即是属于哪个内存颗粒sdram的模式寄存器,模式寄存器地址ma,模式寄存器值reg_val;

[0238]

(2).实现simple_register的new(),reg_read()、reg_write();

[0239]

实现通过simple_register直接访问field的写reg_field_write()、读reg_field_read()。

[0240]

实现把simple_register值更新到字段field的reg_upd_val_to_fields();把字段field的值同步到simple_register值的reg_upd_fields_to_val()。

[0241]

实现为当前寄存器simple_register添加字段filed的方法reg_field_add()。该方法指定新增filed的名称name,访问类型access_type,截止高位msb,开始低位lsb,值val,然后就为simple_register对象增加一个新字段filed对象。simple_register类型会把字段的name/type/msb/lsb/val等信息整合。

[0242]

对于rfu的字段field,simple_register必须确保对该field写入的为全零,对该field读取的值也必须为全零。

[0243]

(3).实现模式寄存器容量检查。

[0244]

最多256个模式寄存器mode register,其中,部分模式寄存器未定义。比如《jesd79-5》中指明了mr117/119/125/127/135/143/155/159/167/175/183/191/199/207/215/223/231/239/247/255等20个模式寄存器尚未定义。当尝试待验证的内存控制的操作指令尝试访问这些模式寄存器时,仿真模型会报出错误信息,以确保内存控制器不会访问sdram未声明的模式寄存器,以免出现非预期的错误。

[0245]

(4).实现对读写属性access_type的检查和兼容性操作。

[0246]

ddr5 sdram模式寄存器主要有只读r、只写w、可读可写r/w、读置位可写sr/w、保留rfu,其中,

[0247]

只读r:只可读出,不可写入。

[0248]

只读w:只可写入,不可读出。

[0249]

可读可写r/w:可读可写。

[0250]

读置位可写sr/w:读取值后,然后该field的所有bits都要被置位为1,可以写入。

[0251]

保留rfu:保留给将来使用的字段field。内存控制器会忽略这些rfu的bits,为了避免往dram中写入不支持的值,上层的寄存器mode register在写入时必须对rfu field写入全零,而在读取时必确保该field返回的为零。

[0252]

3.3基于简单模式寄存器类型simple_register,创建sdram颗粒模式寄存器模型dram_mode_registers。

[0253]

每颗sdram内存颗粒有256个寄存器。基于单个模式寄存器simple_register类型,为单颗内存颗粒sdram的完整模式寄存器模型示意代码如下:

[0254][0255]

(1).每颗sdram内存颗粒有256个模式寄存器。基于单个模式寄存器mode register类型,为单颗sdram内存颗粒所有的模式寄存器声明空间如下:

[0256]

simple_register mode_regs[reg_num];

[0257]

(2).由于ddr5 sdram模式寄存器的vrefca访问mr11,vrefcs访问mr12,rtt_ck访问mr32,rtt_cs访问mr32,rtt_ca访问mr33时,进行的都是影子寄存器(shadow register)操作,也即操作指令首先把数值写入这些影子模式寄存器shadow registers中,然后等发出mpc_appverfrtt之后,其数值才会从shadow register中正在写入到相应的模式寄存器mr11/mr12/mr32/mr33中,因此,专门声明相应的shadow registers,用于操作的中间缓存。需要说明的是,为了实现影子寄存器相关的操作,在本技术的一些实施例中还可以在内存控制器验证装置上构建一个与模式寄存器模块2-23结构相同的寄存器模块(图中未示出)来作为临时存放数据的影子寄存器。在本技术的另一些实施例中,也可以根据实际需要有针对性的创建多个影子寄存器来实现影子寄存器相关的操作。

[0258]

simple_register mode_regshd[4];

[0259]

为了节约shadow registers的空间,可以对相应的操作指令和原模式寄存器的地址做编码,输出为mode_regshd对应的4个地址。比如:

[0260][0261][0262]

(3).实现dram_mode_registers的初始化功能mode_regs_init()。根据ddr5 sdram协议规范中对模式寄存器的描述,通过调用字段field的添加方法,声明模式寄存器

的字段名称、数值、访问类型。

[0263]

而本技术一些实施例构建字段添加方案,方便快捷的简历mr0模式寄存器的数据模型:

[0264]

mode_regs[0].reg_field_add(“burst_length”,r/w,1,0,2’b0);

[0265]

mode_regs[0].reg_field_add(“cas_latency”,r/w,6,2,5’b0);

[0266]

mode_regs[0].reg_field_add(“rfu”,r/w,7,7,1’b0);

[0267]

类似地,可以通过如下声明建立mr1寄存器的数据模型:

[0268]

mode_regs[1].reg_field_add(“pda_enum_id”,r,3,0,4’hf);

[0269]

mode_regs[1].reg_field_add(“pda_sel_id”,r,7,4,4’hf);

[0270]

同理,逐一声明单颗内存颗粒的全部256个模式寄存器,并一一对应地存储在mode_regs[0:255]中。对于协议中未定义的模式寄存器,可以在相应的mr[]单元中为之声明为rfu类型的8bits宽的单字段field类型、值为8’h0,以提高软件鲁棒性。

[0271]

例如,上述“burst_length”属于字段名字field_name;

[0272]

r/w属于字段读写属性,access_type;

[0273]

1:字段所占bit的高位在寄存器中的位置编码field_msb;

[0274]

0:字段所占bit的低位在寄存器中的位置编码field_lsb;

[0275]2’

b0:属于字段默认值field_val_def。

[0276]

图7中的2-16-1 sdram0 mr[0:255],2-16-2 sdram7 mr[0:255],2-19-1 sdram0 mr[0:255],2-19-2 sdram7 mr[0:255]等示意的都是单颗sdram内存颗粒的模式寄存器模型。

[0277]

3.4基于sdram内存颗粒的模式寄存器模型dram_mode_registers,创建单个dimm模式寄存器的内存通道类型dimm_regs_per_channel。

[0278]

如在背景中所介绍,以内存控制器的一个子内存通道有4个rank、一个rank要由同一内存子通道的多颗内存颗粒组成。

[0279]

本技术的一些实施例为之创建了一个高度参数化的类型dimm_regs_per_channel,为一个rank的sdram颗粒的模式寄存器建模,同时,实现在rank水平上对sdram内存颗粒的直接访问。图7的第一单内存通道模型2-9-1和第二单内存通道模型2-9-2就是验证环境中两个内存子通道的模型,示意代码如下:

[0280]

class dim_regs_per_channel#(int max_ranks_per_channel=4,int max_dram_per_rank=10,int reg_num=256,int max_channels_per_dimm=2);

[0281]

dram_mode_registers#(reg_num)

[0282]

dram_mode_regs[max_ranks_per_channel][max_drams_per_rank];

[0283]

//如果有其他寄存器的通道结构,可以声明在这里,便于拓展

[0284]

//function&task定义和声明;

[0285]

endclass

[0286]

(1).内存子通道类型为每个rank上内存颗粒的模式寄存器做了声明:

[0287]

dram_mode_registers#(reg_num)dram_mode_regs[max_ranks_per_channel][max_drams_per_rank];

[0288]

以本技术一些实施例中的max_ranks_per_channel=4,max_drams_per_rank=5

为例,上述方法声明了子通道a的4个rank所对应的sdram颗粒关系:

[0289]

图7的mode_regs[0][0][0:4]这五个内存颗粒组成第一单内存通道模型2-9-1的虚拟rank0 2-11-1;图7的mode_regs[0][1][0:4]这五个内存颗粒组成第一单内存通道模型2-9-1的虚拟rank 1 2-12-1;图7的mode_regs[0][2][0:4]这五个内存颗粒组成第一单内存通道模型2-9-1的虚拟rank2 2-14-1;图7的mode_regs[0][3][0:4]这五个内存颗粒组成第一单内存通道模型2-9-1的虚拟rank3 2-15-1。

[0290]

需要说明的是图7的mode_regs[0][0][0:4]、mode_regs[0][1][0:4]、mode_regs[0][2][0:4]以及mode_regs[0][3][0:4]是为内存子通道a的第三个rank(也即rank2)的5个内存颗粒的所有模式寄存器所创建的程序空间实例。虚拟rank上的各内存颗粒都通过指针指向这些程序空间,进而避免重复声明内存空间,减小了消耗。

[0291]

这些虚拟rank可直接通过rank的id访问,且对这些虚拟rank的访问与对应构建的rank在dimm上的分布形式无关。需要说明的是,

[0292]

(2).第一子通道寄存器应用模块2-24-1用于实现内存通道模型对模式寄存器的访问方法,有了这些方法,验证环境就可以直接从内存通道去访问内存颗粒,省去了很多中间转换的环节。

[0293]

本技术的一些实施例创建了完善的通道模型访问模式寄存器的方法,实现了把虚拟rank中内存颗粒设置到实际内存条dimm上内存颗粒。设置通道识别信号来区分不同的内存子通道,例如,区分内存子通道是通道a还是通道b。设置dimm类型是x4/x8/x16。设置sdram内存颗粒的序号和pdaid编码之间的映射。实现对单个虚拟rank上单个sdram颗粒的特定模式寄存器的访问,即支持待验证的内存控制器对整个模式寄存器粒度的访问,又支持对各模式寄存器上所有字段field粒度的访问。即支持整rank上所有内存颗粒的统一操作,又支持目标rank上目标内存颗粒对应的模式寄存器的pda操作。这种设计结构,简化了验证环境访问模式寄存器时所需的处理过程,加快了仿真和调试效率。

[0294]

(3).同时,本技术的一些实施例的设计结构可以在内存子通道模型中拓展其他类型的寄存器,同时实现相应的方法,使得内存通道模型一样可以直接访问这些寄存器,比如,可以非常方便地拓展应用到rdimm和lrdimm上。

[0295]

3.5基于sdram内存颗粒的模式寄存器模型dram_mode_registers,为全部内存颗粒的模式寄存器创建实例controller_dram_mode_regs[]集合。

[0296]

(1).声明全部dimm上的所有内存颗粒模式寄存器空间的示意代码如下:

[0297]

dram_mode_registers controller_dram_mode_regs[dimm][channel][side][dram];

[0298]

其中,dimm是单个内存控制器所访问的所有dimm数目。本技术的一些实施例以每个内存控制器访问两条dimm为例,dimm=2,对应于图7的第一内存条dimm0和第二内存条dimm1,side是每条dimm上的rank是否分为前后两面封装,前后两面的内存颗粒属于不同的rank。本技术的一些实施例中以每个dimm条都是前后两面封装为例,side=2。channel_是单个内存控制器的内存子通道数量,也是每个ddr5 dimm条上面的内存子通道数量。本技术的一些实施例中以每个内存控制器有两个内存子通道为例,channel=2;dram是由dimm上颗粒密度决定的每rank的颗粒数量。为了支持实际仿真中随机的使能ecc功能,仿真模型以使能ecc的条件来实例化模型。因此,x4类型的dimm,没rank需要10颗内存颗粒;x8类型的则

需要5颗;x16的由于当前业界暂未做ecc的方案,因此2颗就可以。如图7所示,本技术的一些实施例以x8类型的dimm为例,即dram=5。

[0299]

图7为一个内存子通道中的两个dimm上面总共40颗内存颗粒建立了模式寄存器模型的实例。在本技术一些实施例的建模方案中,只有此处模式寄存器模块2-23声明了全部寄存器模型的实例,其他各处都是类型引用。这样的方法,可以大大节约仿真环境的内存消耗,消除了由于模型数据拷贝、赋值等操作引起的仿真时间消耗,提升了仿真效率。

[0300]

(2).通道模式寄存器实例化之后,要初始化每一颗内存颗粒的所有模式寄存器。

[0301]

(3).同时,为当前的两个内存通道声明通道一致性模型:

[0302]

dimm_regs_per_channel([x,x,x]

[0303]

controller_dimm_regs_per_chan[channel_per_controller];

[0304]

3.6为内存通道dimm_regs_per_channel[]和实际的内存颗粒controller_dram_mode_regs[]建立映射关系。

[0305]

图7的第一实线2-22-1和第二实线2-22-2分别表示把第一内存子通道和第二内存子通道的内存颗粒对应的模式寄存器模型映射到内存子通道对应的虚拟rank上。

[0306]

本技术的一些实施例创建了一种重新映射类型引用的方法,快速完成映射。示意代码如下:

[0307][0308]

图7的第一模式寄存器实例2-17-1的模式寄存器实例被映射到第一单内存通道模型2-9-1的虚拟rank0 2-11-1。

[0309]

图7的第二模式寄存器实例2-18-1的模式寄存器实例被映射到第一单内存通道模型2-9-1虚拟rank1 2-12-1。

[0310]

图7的第三模式寄存器2-20-1的模式寄存器实例被映射到第一单内存通道模型2-9-1的虚拟rank2 2-14-1。

[0311]

图7的第四模式寄存器2-21-1的模式寄存器实例被映射到第一单内存通道模型2-9-1的虚拟rank3 2-15-1。

[0312]

其它rank颗粒的模式寄存器映射原理相同。

[0313]

这样,就完成了通道一致性的建模和连接,便利访问和调试。

[0314]

本技术的一些实施例提供一种验证方法,所述验证方法基于构建的内存控制器验证装置实现对待验证的内存控制器的验证过程,该验证方法包括:针对每个内存子通道,完成在dfi接口的当前指令解码,得到指令解码结果;根据所述指令解码结果确认所述当前指令属于与内存模式寄存器操作相关的内存模式寄存器操作指令;确认所述内存模式寄存器操作指令是针对一个可寻址的目标模式寄存器的,则通过与目标虚拟rank对应的rank访问指针访问目标rank并通过所述目标虚拟rank包括的内存颗粒访问指针访问所述目标模式寄存器,完成对所述目标模式寄存器的操作;其中,所述操作是所述当前指令对应的函数,所述目标模式寄存器位于所述目标rank上,所述目标rank位于模式寄存器模块上,所述目标虚拟rank是构建的用于访问所述目标rank上各模式寄存器的指针组,所述模式寄存器模块包括针对内存中各内存颗粒构建的模式寄存器,所述内存是由待验证内存控制器实际所要访问的存储器。

[0315]

在本技术的一些实施例中,所述验证方法还包括:确认所述内存模式寄存器操作指令是针对一个目标虚拟rank的,则通过与所述目标虚拟rank对应的rank访问指针访问目标rank包括的所有模式寄存器,完成对所述所有模式寄存器的操作。

[0316]

在本技术的一些实施例中,所述验证方法还包括:确认所述内存模式寄存器操作指令是针对影子模式寄存器的操作,则通过调用影子寄存器处理函数完成所述操作。

[0317]

在本技术的一些实施例中,所述验证方法还包括:若确认所述内存模式寄存器操作指令所要访问的虚拟rank不存在或者目标模式寄存器属于禁止访问的,则生成错误提示信息。

[0318]

如图8所示,该图提供了一种构建两个内存条以及两条内存子通道的过程以及基于构建的模型对内存控制器进行验证的过程。

[0319]

如图8所示,本技术的一些实施例的内存控制器验证方法,包括:

[0320]

s201,根据系统配置,声明两个内存跳上所有内存颗粒的模式寄存器空间。

[0321]

s202,把内存条上的实际模式寄存器空间,分别映射到两个独立内存通道的虚拟空间上。

[0322]

s203,针对每个内存通道,完成在dfi接口指令解码。

[0323]

s204,判断是否是针对dram内存模式寄存器的指令,如果是则执行s205,否则执行s213的其它后续验证工作。

[0324]

s205,判断是否针对单个dram颗粒的操作,若果是则执行s206,否则执行s212和s211。

[0325]

s212,调用本方案中针对正常欧式寄存器的统一访问方法,每次操作的目标是制定目标rank内的所有dram内存颗粒。

[0326]

s211,完成正常模式寄存器的访问。

[0327]

s206,判断是否是针对影子模式寄存器的操作,如果是则只向s207;否则执行s210的调用本方案中针对正常模式寄存器的pda访问方法,每次操作的目标是单个dram内存颗粒,之后再执行上述s211。

[0328]

s207,调用本方案中针对影子模式寄存器的pda访问方法,每次操作的目标是单个

dram内存颗粒。

[0329]

s208,判断是否要把影子模式寄存器的值写回影子模式寄存器中,如果是则只向s209,否则返回s206。

[0330]

s209,把所有影子模式寄存器的值,复制到对应的正常模式寄存器中。

[0331]

s213,其他后续验证操作。

[0332]

需要说明的是,本技术一些实施例提供的建模方法适应性高,其基于单颗内存的模式寄存器建模、在dfi协议(或其他控制器向下的接口协议)层面映射到逻辑通道、在通道层面实现颗粒的直接访问等验证思维和实现方法,可方便地应用于其他有交叉化、通道化访问媒介的场景;该模型结构拓展性强大,可用于对其他dimm类型(比如rdimm,lrdimm)上面其他控制器的建模和验证的基础,构成组合专利的一部分;该模型复用性高,使验证环境能容易地支持多种带宽扩充方案,比如多个控制器并联方案;该模型可移植性好,实现了package打包封装,方便验证环境中其他uvc实现访问统一的全局内存颗粒的模式寄存器;该模型非常灵活,除了支持相同类型的dimm之外,还可以无缝支持不同密度的dimm的混插方案,比如一个x4 dimm和一个x8dimm。本技术的一些实施例提供对内存模式寄存器的register和filed两种粒度的访问,即可以对整个寄存器读写,也可以直接读写对应的field,简化了访问方式,优化了验证环境的代码。

[0333]

本技术一些实施例的建模方案中,创建了一种简单轻便的寄存器字段field和寄存器register的建模方案;除此之外,本技术的一些实施例基于单颗内存的模式寄存器建模、在dfi协议(或其他控制器向下的接口协议)层面映射到逻辑通道、在通道层面实现颗粒的直接访问等验证思维和实现方法。因此,本领域技术人员可以定义其他形式为寄存器字段field和寄存器register建模方式。本技术一些实施例提出的建模方案,同样适用于ddr5sdram之外的其他设备。本技术一些实施例提出的建模方案,可以构成是对udimm、rdimm、lrdimm等进行验证的基础方方案。

[0334]

在本技术所提供的几个实施例中,应该理解到,所揭露的装置和方法,也可以通过其它的方式实现。以上所描述的装置实施例仅仅是示意性的,例如,附图中的流程图和框图显示了根据本技术的多个实施例的装置、方法和计算机程序产品的可能实现的体系架构、功能和操作。在这点上,流程图或框图中的每个方框可以代表一个模块、程序段或代码的一部分,所述模块、程序段或代码的一部分包含一个或多个用于实现规定的逻辑功能的可执行指令。也应当注意,在有些作为替换的实现方式中,方框中所标注的功能也可以以不同于附图中所标注的顺序发生。例如,两个连续的方框实际上可以基本并行地执行,它们有时也可以按相反的顺序执行,这依所涉及的功能而定。也要注意的是,框图和/或流程图中的每个方框、以及框图和/或流程图中的方框的组合,可以用执行规定的功能或动作的专用的基于硬件的系统来实现,或者可以用专用硬件与计算机指令的组合来实现。

[0335]

另外,在本技术各个实施例中的各功能模块可以集成在一起形成一个独立的部分,也可以是各个模块单独存在,也可以两个或两个以上模块集成形成一个独立的部分。

[0336]

所述功能如果以软件功能模块的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个

人计算机,服务器,或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

[0337]

以上所述仅为本技术的实施例而已,并不用于限制本技术的保护范围,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步定义和解释。

[0338]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应所述以权利要求的保护范围为准。

[0339]

需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。