1.本发明属于通信技术领域,尤其涉及一种串口多机通信电路和方法。

背景技术:

2.单片机是一种集成电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器cpu、随机存储器ram、只读存储器rom、多种i/o口和中断系统、定时器/计数器等功能集成到一块硅片上构成的一个小而完善的微型计算机系统。

3.单片机在实时数据采集和数据处理方面,有着成本低、能满足一般要求、开发周期短等优点,其在智能家居、计算机网络通信与数据传输、工业控制自动化等方面有着广泛的应用。在各种应用场景中,避免不了信息的交换,所以就有了各种各样的通信方式及协议,串口通信因其使用简单可靠,所以用的非常普遍;在工控和测量设备中一般都是使用串口和上位机通信,而且是一对一通信。连接的设备越多,需要的串口数量就越多,占用的单片机引脚资源就越多。因此,能否使用一个串口实现多机通信的功能就有了实际意义。

4.单片机的多机通信一般采用主从式通信方式,在这种方式中,只有一台主机,可以有多台从机。主机发送的信息可以传到各从机或指定的从机,各从机发送的信息只能被主机接收,从机之间不能进行通信。

5.目前的单片机多机通信一般都是通过从软件上给从机分配地址来实现,单片机串行通信中的sm2位(多机通信控制位)专门用来识别不同的从机,该方法实现的一般过程为:

6.第一步:使所有从机处于地址帧接收状态(sm2=1);

7.第二步:主机先发送一个地址帧,其中前8位数据表示要寻址的从机地址,第9位为1(tb8=1)表示该帧为地址帧;

8.第三步:所有从机接收到地址帧后,把接收到的地址与本机地址相比较;地址相符时将sm2清0,并发回从机地址作为应答信号,由主机进行确认。地址不相符的从机不作任何处理,仍保持sm2=1;

9.第四步:在主机确认地址正确时,向寻址的从机发送相应的数据信息。当确认地址错误时,不发送数据信息;

10.第五步:地址相符的从机(sm2=0),可以接收到主机发来的数据信息。而对于地址不符的从机sm2=1,则不予理睬,这样就实现了主机与地址相符的从机之间的双机通信;

11.第六步:被寻址的从机通信结束后,恢复为多机通信状态(sm2=1)。

12.从上述通信过程可以看到现有方法对主、从机的软件设计要求较高,而且通信过程十分繁琐,如果其中一个从机出现故障,长期占用通信总线,可能导致整个总线上从机通信异常。

技术实现要素:

13.为了解决现有单片机多机通信所采用的方法对主、从机的软件设计要求较高,通信过程繁琐,如果其中一个从机出现故障,长期占用通信总线,可能导致整个总线上从机通

信异常的问题,本发明提供一种通用性强、实现简单、成本低廉且安全可靠的单片机串口多机通信电路和方法。

14.本发明采用的技术方案如下:

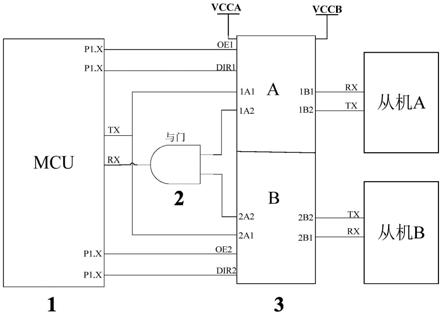

15.本发明提供了一种串口多机通信电路,包括主机、与门逻辑芯片、16位总线收发器以及2个从机;

16.16位总线收发器由两个数据收发器组成;其中,每个数据收发器均设置有控制端口oe和控制端口dir;每个数据收发器中设置有至少一条数据发送通道和至少一条数据接收通道;

17.主机通过其上设置的4个通用端口分别与每个数据收发器中的控制端口oe、控制端口dir连接;

18.主机的发送tx端口分别与每个数据收发器的数据发送通道输入端连接;

19.主机的接收rx端口通过与门逻辑芯片分别与每个数据收发器中数据接收通道的输出端连接;

20.每个数据收发器中数据发送通道的输出端均和与之对应的从机接收rx端口连接;

21.每个数据收发器中数据接收通道的输入端均和与之对应的从机发送tx端口连接。

22.进一步地,上述主机和从机为mcu芯片或者fpga芯片或者dsp芯片。

23.进一步地,上述16位总线收发器为单电压供电或者双电压供电。

24.进一步地,上述16位总线收发器为双电压供电时,一个电压和主机供电电压保持一致,另一个电压和从机供电电压保持一致。

25.进一步地,上述与门逻辑芯片的与门输入端接上拉电阻,确保与门逻辑芯片供电电压与主机供电电压保持一致。

26.上述串口多机通信电路的使用方法具体过程如下:

27.主机向其中一个从机发送数据时:

28.通过主机的通用端口控制其中一个数据收发器的控制端口oe为低电平,控制端口dir为高电平,同时控制另一个数据收发器控制端口oe为高电平;

29.主机接收其中一个从机的数据时:

30.通过主机的通用端口控制其中一个数据收发器的控制端口oe为低电平,控制端口dir为低电平,同时控制另一个数据收发器控制端口oe为高电平。

31.本发明所具有的积极效果:

32.1、本发明原理简单通用,主机只需要设定16位总线收发器的控制信号即可实现与相应从机的串口通信,不需要额外的通信协议设计,大大简化了主、从机的软件设计,降低了开发人员的时间成本。

33.2、本发明安全可靠,主机和某一从机通信时在硬件上是完全独立的通信链路,与其他从机的通信链路则是完全关闭的,有一个从机出现异常,关闭其通信链路即可,不会影响其他从机的通信。从而不会产生现有技术中单片机和所有从机的通信链路都是打开的,如果从机软件设计错误通信异常,则会造成单片机与所有从机通信异常的问题。

34.3、本发明通用性强,从机可以是和主机同电平电源供电,也可以是和主机不同电平电源供电,对主机和从机类型不做限定,包括但不限于单片机、fpga、dsp等等处理器系统,适用范围广,可以推广到任何一种主、从机多机通信系统。

35.4、本发明选用可控的数据收发器来隔离主、从机通信接口,一定程度增强了接口的安全性,同时提高了通信驱动能力,加大了通信传输距离。

36.5、本发明在应用于多机通信时不限定通信接口电平,可以采取包括但不限于rs232、rs422、rs485、lvds等通信接口。

37.6、本发明选用的材料和元器件均为通用器件,每一种均是种类繁多、价格便宜,特别适合于新产品研制开发和批量生产。

附图说明

38.图1为本发明的电路架构原理图。

具体实施方式

39.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合说明书附图对本发明的具体实施方式做详细的说明,显然所描述的实施例是本发明的一部分实施例,而不是全部实施例。基于本发明中的实施例,本领域普通人员在没有做出创造性劳动前提下所获得的所有其他实施例,都应当属于本发明的保护的范围。

40.在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是本发明还可以采用其他不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似推广,因此本发明不受下面公开的具体实施例的限制。

41.本实施例提供了一种串口多机通信电路的具体结构,如图1所示,包括主机1、与门逻辑芯片2、16位总线收发器3、从机a和从机b;

42.主机1上设置有一个发送tx端口、一个接收rx端口以及若干个通用端口p1.x(本实施例的主机为mcu芯片);

43.16位总线收发器由两组数据收发器组成,图1中为数据收发器a和数据收发器b,且数据收发器a、数据收发器b和从机a、从机b一一对应;

44.其中,每个数据收发器均设置有控制端口oe和控制端口dir(如图1所示,数据收发器a具有控制端口oe1和控制端口dir1,数据收发器b具有控制端口oe2和控制端口dir2);

45.每个数据收发器中设置有至少一条数据发送通道和至少一条数据接收通道(即图1所示,数据收发器a中数据发送通道是由端口1a1和1b1之间组成,数据收发器b中数据发送通道是由端口2a1和2b1之间组成;数据收发器a中数据接收通道是由端口1a2和1b2之间组成,数据收发器b中数据发送通道是由端口2a2和2b2之间组成);

46.从机a和从机b结构一致,均设有一个发送tx端口和一个接收rx端口;

47.本实施例的具体电路连接为:

48.主机1的发送tx端口分别与数据收发器a的1a1端口和2a1连接,从机a的发送tx端口和数据收发器a的1b2端口连接,从机a的接收rx端口和数据收发器a的1b1端口连接;从机b的发送tx端口和数据收发器b的2b2端口连接,从机b的接收rx端口和数据收发器b的2b1端口连接;数据收发器a的1a2端口和数据收发器b的2a2端口经过与门逻辑芯片2相与后与主机1的接收rx端口连接,16位总线收发器3的控制端口oe1、dir1、oe2、dir2和主机1的p1.x口连接。

49.还需要说明的是:

50.1、当主机1的通用端口足够多时,可以通过再增加n个与门逻辑芯片2、n个16位总线收发器3,再同时控制2n个从机,即就是说:当一个主机有4n个通用端口时,可以通过设置n个与门逻辑芯片2、n个16位总线收发器3,同时控制2n个从机。

51.2、主机1为通用器件包括但不限于mcu、fpga、dsp等处理器系统,供电电平包括但不限于 5v、 3.3v等,主机1对16位总线收发器的控制端口包括但不限于p1.x、p2.x等通用io口;

52.3、16位总线收发器3为通用器件,包括两组数据收发器,每组数据收发器均由端口oe和dir共同控制,每组数据收发器的控制逻辑为:当oe为低电平,数据收发器打开,当oe为高电平,数据收发器关闭;当dir为高电平,数据从主机传输至从机,当dir为低电平,数据从从机传输至主机。

53.16位总线收发器3可以为单电压供电,也可以为双电压供电,双电压供电时:vcca需与主机1供电电压保持一致,vccb需与从机a和从机b供电电压保持一致。

54.4、与门逻辑芯片2为通用器件,可包括一路或者多路逻辑与门,为提高通信可靠性,可在与门输入端接上拉电阻,与门逻辑芯片2供电电源需与主机1供电电压保持一致。

55.5、从机a和从机b包括但不限于mcu、fpga、dsp等处理器。

56.本实施的电路动态工作情况描述为:

57.当需要主机1向从机a发送数据时:

58.通过主机1的p1.x端口控制数据收发器a控制端口oe1为低电平,控制端口dir1为高电平,同时控制数据收发器b控制端口oe2为高电平;

59.当主机1接收从机a发送的数据时:

60.通过主机1的p1.x端口控制数据收发器a控制端口oe1为低电平,控制端口dir1为低电平,同时控制数据收发器b控制端口oe2为高电平。

61.当需要主机1向从机b发送数据时:

62.通过主机1的p1.x端口控制数据收发器b控制端口oe2为低电平,控制端口dir2为高电平,同时数据收发器a控制端口oe1为高电平;

63.当需要主机1接收从机b发送的数据时:

64.通过主机1的p1.x端口控制数据收发器b控制端口oe2为低电平,控制端口dir2为低电平,同时数据收发器a控制端口oe1为高电平。

65.总而言之,本发明提供的基于16位总线收发器的串口多机通信电路及方法,电路架构简单,软件设计简单,通信安全可靠。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。