接口板卡、用户设备及cpu的测试系统

技术领域

1.本实用新型涉及测试技术领域,尤其涉及一种接口板卡、用户设备及cpu的测试系统。

背景技术:

2.随着cpu(central processing unit,中央处理器)芯片设计的技术发展,cpu的高速接口可以通过软件配置成不同的协议类型,实现不同的接口功能。即同一信号,可以配置成pcie(peripheral component interconnect express,高速外设组件互连),可以配置成网络,也可以配置成sata(serial advanced technology attachment,串行高级技术附件)存储接口等。

3.当前,测试适配芯片采用的是成熟主板,phy(物理层)芯片直接集成在主板上,这种方案的互联链路简单,中间没有引入其他连接器等器件的干扰。但是不够灵活,如果需要更换phy芯片,测试其他型号的phy芯片,就需要重新设计主板,研发成本比较高。

技术实现要素:

4.本实用新型提供的接口板卡、用户设备及cpu的测试系统,能够使得一个接口板卡可以测试验证至少一种phy芯片与cpu的适配性能,节省了研发成本。

5.本实用新型提供一种接口板卡,包括:

6.至少一个phy芯片;

7.与至少一个所述phy芯片连接的至少一个接口,所述接口用于与所述测试设备相连;

8.与至少一个所述phy芯片连接的pcie finger;所述pcie finger用于与cpu主板相连。

9.可选地,当所述phy芯片为至少两个时,所述接口为至少两个;

10.至少两个所述phy芯片为相同类型或者不同类型。

11.可选地,当一个所述phy芯片为至少两路时,所述接口为至少两个。

12.可选地,所述的接口板卡,还包括:

13.第一跳线;

14.所述phy芯片的mdio管脚连接到所述第一跳线的第一端;

15.所述第一跳线的第二端用于与所述pcie finger的定义为mdio信号的rsvd管脚连接。

16.可选地,所述的接口板卡,还包括:

17.第二跳线;

18.所述phy芯片的mdio管脚连接到所述第二跳线的第一端;

19.所述第二跳线的第二端用于与所述接口板卡外部的mdio信号连接。

20.可选地,所述的接口板卡,还包括:mcu;

21.所述phy芯片的mdio管脚连接到所述mcu的mdio管脚。

22.可选地,所述接口为rj45接口。

23.可选地,所述pcie finger与所述cpu主板相连的接口协议为sgmii千兆位介质独立接口或kr。

24.本实用新型还提供一种用户设备,所述用户设备包括上述接口板卡。

25.本实用新型还提供一种cpu的测试系统,包括:

26.cpu主板、测试设备、和接口板卡;

27.所述cpu主板通过所述接口板卡与所述测试设备相连;

28.所述接口板卡包括:至少一个phy芯片;

29.与至少一个所述phy芯片连接的至少一个接口,所述接口用于与所述测试设备相连;

30.与至少一个所述phy芯片连接的pcie finger;所述pcie finger用于与所述cpu主板相连。

31.本实用新型提供的接口板卡、用户设备及cpu的测试系统,所述接口板卡包括至少一个phy芯片;与至少一个所述phy芯片连接的至少一个接口,所述接口用于与所述测试设备相连;与至少一个所述phy芯片连接的pcie finger;所述pcie finger用于与cpu主板相连,可以使得一个接口板卡用于测试至少一种phy芯片与cpu的适配性能,可以集成多款不同品牌,单路,双路的phy芯片在一块板卡上,从而可以节省研发成本;另外,方便cpu产品测试,可以使用现有的主板,只要主板上有可配置成sgmii网络接口的pcie finger,就可以进行rj45相关网络芯片的适配测试。对主板要求不高,通用性强;板卡按照标准pcie卡尺寸设计,方便应用到标准机箱内部。

附图说明

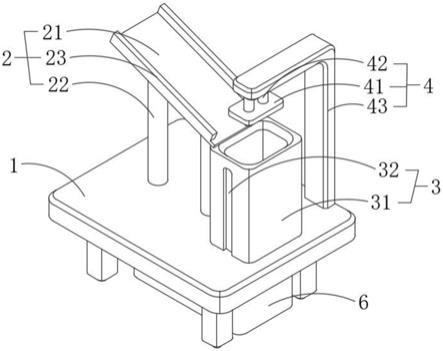

32.图1为本实用新型一实施例cpu的测试系统的结构示意图;

33.图2为本实用新型一实施例所述的板卡的连接示意图;

34.图3为本实用新型另一实施例所述的板卡的结构示意图。

具体实施方式

35.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

36.本实用新型实施例提供一种cpu的测试系统,如图1所述,所述cpu的测试系统,包括:

37.接口板卡1、cpu主板2、测试设备3;

38.所述cpu主板2通过所述接口板卡1与所述测试设备3相连。

39.如图2所示,所述接口板卡1包括:至少一个phy芯片11;

40.与至少一个所述phy芯片11连接的至少一个接口12,所述接口用于与所述测试设

备3相连;

41.与至少一个所述phy芯片11连接的pcie finger(高速外设组件互连金手指)13;所述pcie finger用于与所述cpu主板相连。

42.以上实施例中,可以使得一个接口板卡用于测试至少一种phy芯片与cpu的适配性能,从而节省了研发成本。

43.如图2所示,当所述phy芯片为至少两个时,所述接口为至少两个;至少两个所述phy芯片为相同类型或者不同类型。图2中示出了8个。因此,可以验证双路两个phy芯片与cpu网络接口的适配性能。

44.如图2所示,当一个所述phy芯片为至少两路时,所述接口为至少两个。图2中示出的bcm5482s8为两路。因此,可以验证双路phy芯片与cpu网络接口的适配性能。

45.如图3所示,在一个实施例中;所述的接口板卡,还包括:

46.第一跳线14;

47.所述phy芯片11的mdio(management data input/output,管理数据输入输出)管脚连接到所述第一跳线14的第一端;

48.所述第一跳线15的第二端用于与所述pcie finger 13的定义为mdio信号的rsvd(保留)管脚连接。

49.上述实施例中,可以通过跳线帽选择本实用新型的rj45测试板卡的mdio连接到pcie finger的rsvd上的定义mdio信号,来进行测试。

50.如图3所示,在一个实施例中;所述的接口板卡,还包括:

51.第二跳线15;

52.所述phy芯片11的mdio管脚连接到所述第二跳线15的第一端;

53.所述第二跳线15的第二端用于与所述接口板卡外部的mdio信号连接。

54.上述实施例中,可以通过跳线帽选择本实用新型的rj45测试板卡的mdio连接到外部插针,来进行测试。

55.如图3所示,所述的接口板卡,还包括:mcu(microcontroller unit,微控制单元)16;

56.所述phy芯片11的mdio管脚连接到所述mcu 16的mdio管脚。

57.上述实施例中,可以通过跳线帽选择板载mcu来配置phy芯片,来进行测试。

58.其中,所述接口12可以为rj45接口。

59.其中,所述pcie finger与所述cpu主板相连的接口协议为sgmii(serial gigabit media independent interface,串行千兆位媒质独立接口)或kr。

60.本实用新型实施例还提供一种用户设备,所述用户设备包括如所述的接口板卡。

61.以下描述本实用新型的应用场景:

62.本实用新型主要针对网络接口的适配。在产品主板上,因为产品形态,一般都是硬件上适配具体的网络芯片,对外为固定接口的连接器,软件上配置成对应的接口协议。在cpu研发中,需要测试适配不同厂商,不同型号的网络芯片,测试适配性能,以便给整机厂商推荐合适方案。本实用新型主要测试的协议是sgmii接口,通过phy芯片转换为千兆rj45接口,通过千兆网线与另一块板卡,或交换机互联测试。

63.本实用新型实施例实现了一种集成多种型号的phy芯片的千兆rj45接口板卡,通

过pcie槽与cpu主板相连,这样一块板卡可以测试验证多种型号的phy芯片与cpu的适配性能,节省了研发成本。

64.如图2,本实用新型的rj45接口卡为pcie插卡形态,集成2个pcie finger,为双面pcie金手指卡,尺寸跟标准pcie全高半长卡相同。其中,finger是标准pcie finger形态,phy芯片可以为不同品牌,不同通道数量,比如为4路的phy芯片。

65.图2为双金手指rj45接口卡框图,本实用新型的rj45接口卡包括2个模块。

66.模块一:

67.包括一颗rtl8211fs phy芯片,一颗yt8521sh芯片,一颗88e1512芯片,一颗88e1514芯片。这4颗芯片都为单路phy芯片,分别为不同厂家品牌型号。

68.这4颗芯片分别连接1个千兆rj45接口。并通过pcie finger与cpu主板相连,接口协议为sgmii。

69.这样通过模块一,可以实现验证不同品牌的单路phy芯片与cpu网络接口的适配性能。

70.模块二:

71.包括一颗bcm5482双路phy芯片,一颗bcm54616单路phy芯片,一颗vsc8211单路phy芯片,和相应的4个千兆rj45接口,后面2个phy芯片为同一品牌。这3颗芯片通过pcie finger与cpu主板相连,接口协议为sgmii。

72.这样通过模块二,可以验证双路phy芯片与cpu网络接口的适配性能,并增加验证2家品牌的单路phy芯片。

73.另外,图3为rj45测试板卡mdio连接拓扑示意图。本实用新型的rj45测试板卡上集成了mdio接口,说明如下:

74.2个模块相同设计:

75.pcie finger上还有多个rsvd未定义pin,有的主板上把部分rsvd pin定义为mdio信号。这样本实用新型的rj45测试板卡也把相应的rsvd pin定义为mdio信号,通过跳线帽选择本实用新型的rj45测试板卡的mdio连接到pcie finger的rsvd上的定义mdio信号,还是连接到外部插针。如果主板pcie slot上没有设计mdio接口,可以通过外部插针连接mdio。

76.另外,如图3所示,本实用新型的rj45测试板卡上还设计有mcu,也通过mdio与各个phy相连,这样可以选择cpu通过mdio来配置phy芯片,还是通过板载mcu来配置phy芯片。后者适用于cpu对phy芯片的phy address有特定限制的情况下,即cpu无法配置超出一定范围的phy address phy芯片。

77.本实用新型实施例提供的接口板卡、用户设备及cpu的测试系统具有以下有益效果:

78.1、方便cpu产品测试,可以使用现有的主板,只要主板上有可配置成sgmii网络接口的pcie finger,就可以进行rj45相关网络芯片的适配测试。对主板要求不高,通用性强。

79.2、可以集成多款不同品牌,单路,双路的phy芯片在一块板卡上,节省研发成本。

80.3、板卡按照标准pcie卡尺寸设计,方便应用到标准机箱内部。

81.以上所述,仅为本实用新型的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变

化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。