1.本实用新型涉及频率合成器技术领域,特别涉及一种基于锁相环的频率合成器。

背景技术:

2.目前模拟集成电路设计中有2种基本的频率合成方法:直接频率合成和间接频率合成(又称锁相频率合成)。基于锁相环结构的频率综合器具有高性能的优点,是目前应用最广泛的本振信号产生方式。然而,现有的频率合成器包括压控振荡器、线性低通滤波器、分频器、电荷泵和鉴频鉴相器等,现有的双频频率合成器内部包含两个锁相环,每个锁相环内都有一个压控振荡器。因此,成本较高,所以,如何开发一种低成本、小体积的频率合成器已成为本领域技术人员亟待解决的问题。

技术实现要素:

3.本实用新型解决的技术问题是,提供一种低成本、小体积、便携式及高稳定的基于锁相环的频率合成器。

4.本实用新型提供一种基于锁相环的频率合成器,包括频率设置单元、微处理器单元、锁相环单元、压控振荡单元、电压采集单元及频段选择单元,所述频率设置单元与所述微处理器单元电连接,所述微处理器单元与所述锁相环单元及所述频段选择单元电连接,所述锁相环单元与所述压控振荡单元电连接,所述压控振荡单元与所述电压采集单元电连接,所述电压采集单元与所述微处理器单元电连接,所述频段选择单元与所述压控振荡单元电连接。

5.在一个实施例中,所述锁相环单元包括晶体振荡电路、频率控制芯片及滤波电路,所述晶体振荡电路与所述频率控制芯片电连接,所述频率控制芯片与所述压控振荡单元及所述滤波电路电连接,所述滤波电路与所述压控振荡单元电连接。

6.在一个实施例中,所述滤波电路包括第一电阻、第二电阻、第三电阻、第四电阻、第一电容、第二电容、第一三极管及第二三极管,所述第一电阻的第一端与所述频率控制芯片电连接,所述第一电阻的第二端与所述第二电阻的第一端电连接;所述第二电阻的第一端与所述第一电容的第一端电连接,所述第二电阻的第二与所述第二电容的第一端电连接;

7.所述第二电容的第二端与所述第一电容的第二端及所述压控振荡单元电连接;所述第三电阻的第一端用于与电源电连接,所述第三电阻的第二端与所述第二电容的第二端及所述第一三极管的集电极电连接;所述第一三极管的基极与所述第一电容的第一端电连接,所述第一三极管的发射极与所述第四电阻的第一端及所述第二三极管的基极电连接,所述第四电阻的第二端接地;所述第二三极管的集电极与所述第一三极管的集电极电连接,所述第二三极管的发射极接地。

8.在一个实施例中,所述锁相环单元包括还包括第三电容,所述第三电容的第一端与所述频率控制芯片电连接,所述第三电容的第二端与所述压控振荡单元电连接。

9.在一个实施例中,所述锁相环单元包括还包括第四电容,所述第四电容的第一端

与所述频率控制芯片电连接,所述第四电容的第二端与所述压控振荡单元电连接。

10.在一个实施例中,所述晶体振荡电路包括晶体振荡器、第五电容及第六电容,所述晶体振荡器的第一端与所述第五电容的第一端相连,所述晶体振荡器的第二端与所述第六电容的第一端相连;所述第五电容的第一端与所述频率控制芯片电连接,所述第五电容的第二端接地;所述第六电容的第一端与所述频率控制芯片电连接,所述第六电容的第二端接地。

11.在一个实施例中,所述基于锁相环的频率合成器还包括显示单元,所述显示单元与所述微处理器单元电连接。

12.在一个实施例中,所述频率设置单元包括键盘,所述键盘与所述微处理器单元电连接。

13.本实用新型具有如下有益效果:本实用新型通过所述频率设置单元、微处理器单元、锁相环单元、压控振荡单元、电压采集单元及频段选择单元之间的配合,在频段选择单元的程控下,通过锁相环单元将压控振荡单元输出的频率锁定在所需的频率上。此外,通过电压采集单元对输出的波形的电压峰值进行采集,并通过微处理器单元对锁相环单元的控制,从而可以实现低成本、小体积、便携式及高稳定。

附图说明

14.图1为本实用新型基于锁相环的频率合成器的原理框图。

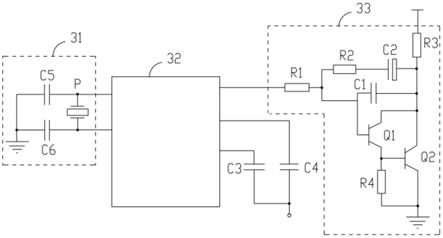

15.图2为本实用新型基于锁相环的频率合成器的锁相环单元的电路图。

具体实施方式

16.下面结合附图和实施例对本实用新型进行详细说明。需要说明的是,如果不冲突,本实用新型实施例以及实施例中的各个特征可以相互结合,均在本实用新型的保护范围之内。

17.请参阅图1及图2,本实用新型提供一种基于锁相环的频率合成器,包括频率设置单元1、微处理器单元2、锁相环单元3、压控振荡单元4、电压采集单元5及频段选择单元6,所述频率设置单元1与所述微处理器单元2电连接。所述微处理器单元2与所述锁相环单元3及所述频段选择单元6电连接,所述锁相环单元3与所述压控振荡单元4电连接,所述压控振荡单元4与所述电压采集单元5电连接。所述电压采集单元5与所述微处理器单元2电连接,所述频段选择单元6与所述压控振荡单元4电连接。

18.其中,在本实施例中,所述频率设置单元1包括键盘,所述键盘与所述微处理器单元2电连接。通过所述键盘,用户在使用过程中,可以增加或者降低该频率合成器输出的信号的频率。可以理解的是,所述微处理器单元2可以包括现场可编程门阵列(field programmable gate array,简称fpga)或者复杂可编程逻辑器件(complex programmable logic device,简称cpld)等,在此不做具体限定。

19.所述锁相环单元3包括晶体振荡电路31、频率控制芯片32及滤波电路33,所述晶体振荡电路31与所述频率控制芯片32电连接,用于为所述频率控制芯片32提供时钟信号。所述频率控制芯片32与所述压控振荡单元4及所述滤波电路33电连接,用于对压控振荡单元4输出的频率信号进行分频并将分频后的频率信号与参考频率相位比较,以输出误差电压。

所述滤波电路33与所述压控振荡单元4电连接,用于对频率控制芯片32输出的电压进行滤波。其中,所述频率控制芯片32可以是北京中科微电子技术有限公司生产的型号为at9257的锁相环芯片。当然,其也可以为其它公司生产的芯片,在此不做具体限定。

20.所述滤波电路33包括第一电阻r1、第二电阻r2、第三电阻r3、第四电阻r4、第一电容c1、第二电容c2、第一三极管q1及第二三极管q2,所述第一电阻r1的第一端与所述频率控制芯片32电连接,所述第一电阻r1的第二端与所述第二电阻r2的第一端电连接。所述第二电阻r2的第一端与所述第一电容c1的第一端电连接,所述第二电阻r2的第二与所述第二电容c2的第一端电连接。

21.所述第二电容c2的第二端与所述第一电容c1的第二端及所述压控振荡单元4电连接。所述第三电阻r3的第一端用于与电源电连接,所述第三电阻r3的第二端与所述第二电容c2的第二端及所述第一三极管q1的集电极电连接。所述第一三极管q1的基极与所述第一电容c1的第一端电连接,所述第一三极管q1的发射极与所述第四电阻r4的第一端及所述第二三极管q2的基极电连接,所述第四电阻r4的第二端接地。所述第二三极管q2的集电极与所述第一三极管q1的集电极电连接,所述第二三极管q2的发射极接地。通过所述锁相环单元3改变所述压控振荡单元4工作频率,一旦进入两个信号频率相同,则相位比较器输出一固定电压,从而振荡器稳定地工作在预置频率上。

22.所述锁相环单元3包括还包括第三电容c3及第四电容c4,所述第三电容c3的第一端与所述频率控制芯片32电连接,所述第三电容c3的第二端与所述压控振荡单元4电连接。所述第四电容c4的第一端与所述频率控制芯片32电连接,所述第四电容c4的第二端与所述压控振荡单元4电连接。其中,所述第三电容c3及第四电容c4均为耦合电容,其选择通过需要的频率,而截止不需要的频率,从而利于信号的传输。

23.所述晶体振荡电路31包括晶体振荡器p、第五电容c5及第六电容c6,所述晶体振荡器p的第一端与所述第五电容c5的第一端相连,所述晶体振荡器p的第二端与所述第六电容c6的第一端相连。所述第五电容c5的第一端与所述频率控制芯片32电连接,所述第五电容c5的第二端接地。所述第六电容c6的第一端与所述频率控制芯片32电连接,所述第六电容c6的第二端接地。

24.所述基于锁相环的频率合成器还包括显示单元7,所述显示单元7与所述微处理器单元2电连接。通过所述显示单元7可以显示电压信号的峰值及频率,便于用户观察。

25.综上所述,本实用新型通过所述频率设置单元1、微处理器单元2、锁相环单元3、压控振荡单元4、电压采集单元5及频段选择单元6之间的配合,在频段选择单元6的程控下,通过锁相环单元3将压控振荡单元4输出的频率锁定在所需的频率上。此外,通过电压采集单元5对输出的波形的电压峰值进行采集,并通过微处理器单元2对锁相环单元3的控制,从而可以实现低成本、小体积、便携式及高稳定。

26.以上对本实用新型所提供的基于锁相环的频率合成器进行了详细介绍,本文中应用了具体个例对本实用新型的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本实用新型的方法及其核心思想;同时,对于本领域的一般技术人员,依据本实用新型的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容仅为本实用新型的实施方式,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,

均同理包括在本实用新型的专利保护范围内,不应理解为对本实用新型的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。