技术特征:

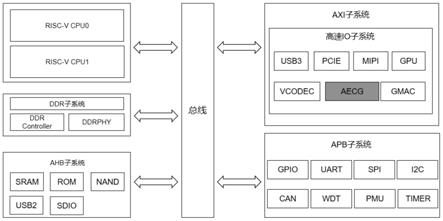

1.一种基于心电算法加速的双核soc架构,其特征在于,包括cpu单元以及与所述cpu单元通过总线连接的ddr子系统、axi子系统、ahb子系统以及apb子系统,所述cpu单元采用基于risc-v的双核处理器,所述ahb子系统、ddr子系统以及axi子系统与所述cpu单元通过与所述总线控制器相连的高速片上总线连接;所述apb子系统与所述cpu通过与所述总线控制器连接的低速片上总线连接;其中,所述axi子系统中链接有心电算法加速单元,所述心电算法加速单元采用灵活可配置的卷积硬件加速器。2.如权利要求1所述的一种基于心电算法加速的双核soc架构,其特征在于,所述cpu单元还通过与所述总线控制器相连的高速片上总线连接有加解密运算单元,用于对采集的心电数据进行加密处理。3.如权利要求1所述的一种基于心电算法加速的双核soc架构,其特征在于,所述心电算法加速单元采用以卷积神经网络和小波变换为核心的加速电路。4.如权利要求1所述的一种基于心电算法加速的双核soc架构,其特征在于,所述心电算法加速单元包括可重配置的卷积运算单元、适应不同卷积核的输入缓存单元以及数据重排单元。5.如权利要求4所述的一种基于心电算法加速的双核soc架构,其特征在于,所述卷积运算单元,其用于执行卷积运算中的基本运算,其中,对于输入的数据采用并行计算的方式,支持若干卷积核尺寸。6.如权利要求4所述的一种基于心电算法加速的双核soc架构,其特征在于,所述输入缓存单元,其用于对输入的特征图进行缓存,并针对不同尺寸的卷积核,生成对应的窗口进行卷积计算。7.如权利要求4所述的一种基于心电算法加速的双核soc架构,其特征在于,所述数据重排单元中的前处理单元用于对输入的数据进行小波变换;或,对输入缓存的数据进行划分和重排处理,实现输入特征图在卷积运算单元上的不同映射关系,其中,所述不同映射关系对应不同的计算模式,所述映射方式由外部配置决定,通过外部配置的设置可实现映射方式的灵活配置。8.如权利要求1所述的一种基于心电算法加速的双核soc架构,其特征在于,所述axi子系统用于连接若干高速外设,包括但不限于usb、pcie、mipi、以及gpu。9.如权利要求1所述的一种基于心电算法加速的双核soc架构,其特征在于,所述apb子系统用于连接若干低速外设,包括但不限于gpio、uart、spi以及i2c。10.一种基于心电算法加速的双核soc架构的工作方法,其特征在于,其利用如权利要求1-9任一项所述的基于心电算法加速的双核soc架构,包括:挂载于axi的高速总线上的心电算法加速单元与cpu单元进行通信;心电算法加速单元对接收到的心电数据进行运算推理分析,并将分析结果通过axi总线系统送回cpu单元;cpu单元将分析结果通过总线系统调度到存储和显示设备。

技术总结

本公开提供了一种基于心电算法加速的双核SoC架构及其工作方法,其特征在于,包括CPU单元以及与所述CPU单元通过总线连接的DDR子系统、AXI子系统、AHB子系统以及APB子系统,所述CPU单元采用基于RISC-V的双核处理器,所述AHB子系统、DDR子系统以及AXI子系统与所述CPU单元通过与所述总线控制器相连的高速片上总线连接;所述APB子系统与所述CPU通过与所述总线控制器连接的低速片上总线连接;其中,所述AXI子系统中链接有心电算法加速单元,所述心电算法加速单元采用灵活可配置的卷积硬件加速器。速器。速器。

技术研发人员:王刚 吴本阳

受保护的技术使用者:山东领能电子科技有限公司

技术研发日:2021.12.20

技术公布日:2022/4/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。