1.本发明涉及分别根据权利要求1和6所述的用于同步串行数据传输的装置和方法。此外,本发明涉及根据权利要求11所述的随动电子设备(folgeelektronik)。该随动电子设备在应用于自动化技术中时是特别有利的,因为这里经由长线路的数据传输经常是必要的。

背景技术:

2.在自动化技术中经常使用提供数字测量值的测量设备。在例如被用于控制机床的数控领域中,这特别适用于用于测量线性或旋转运动的位置测量设备。生成数字(绝对)测量值的位置测量设备被称为绝对位置测量设备。

3.串行数据接口主要用于传输绝对位置值和其他数据,因为这些数据接口利用仅仅少量数据传输线路就能应付并且尽管如此仍具有高的数据传输率。由于数据传输大多经由大的线缆长度进行,所以接口信号例如根据rs-485标准以差分方式传输。为此,在发送器侧,地参考(massebezogen)数字信号借助专用驱动器模块被转换成差分信号并输出,在接收器侧,所传输的信号在接收模块中又被转换回用于进一步处理。传输经由线路对进行,所述线路对的线路彼此绞合。

4.所谓的同步串行接口是特别有利的,所述同步串行接口具有单向或双向运行的数据线路对和时钟线路对。数据包经由数据线路对的传输与时钟线路对上的时钟信号同步地进行。在自动化技术中,大量这样的数字标准接口已得以实现,同步串行接口的流行代表例如是申请人的endat接口,另一种以名称ssi已知。

5.ssi接口在ep 0 171 579 a1中被描述。在此情况下涉及具有单向运行的数据线路对和单向运行的时钟线路对的同步串行数据接口。这里,位置值从位置测量设备的读出与经由时钟线路对传输的时钟信号同步地进行。

6.而ep 0 660 209 a1描述了申请人的endat接口的原理。该endat接口同样是同步串行接口,然而该同步串行接口除了单向运行的时钟线路对之外具有双向运行的数据线路对。由此,数据在(从随动电子设备(例如数控装置)至位置测量设备和从位置测量设备至随动电子设备的)两个方向上的传输是可能的。这里,数据传输也与时钟信号同步地进行。

7.被用于传输的线路对除了欧姆电阻之外不仅具有电容特性而且具有电感特性,所述特性与线路长度相关。在传输技术中,在此上下文中谈及线路的单位长度电容和单位长度电感。在数据传输中由此得到的重新加载过程导致所传输的信号的变形。因此,用于安全传输的最大可实现的线缆长度以恒定数据率为前提由接收器侧的差分接收器的从所接收的信号恢复原始发送的数字信号的能力决定。

技术实现要素:

8.本发明的任务是创建用于在同步串行接口的情况下提高最大线路长度的装置。

9.该任务通过根据权利要求1所述的装置来解决。

10.提出一种用于经由差分数据通道和差分时钟通道的同步串行数据传输的装置,该装置具有接口控制器,以及时钟发送模块和数据接收模块,所述接口控制器具有时钟发生器和数据控制器,其中

‑ꢀ

可以由时钟发生器产生发送时钟信号,所述发送时钟信号在一个数据传输循环期间包括具有周期持续时间的时钟脉冲序列,

‑ꢀ

所述发送时钟信号被输送给时钟发送模块,所述时钟发送模块将发送时钟信号转换成差分时钟信号,用于经由时钟通道输出,

‑ꢀ

经由差分数据通道到达的差分数据信号被输送给数据接收模块,所述数据接收模块将所述差分数据信号转换成数据信号并且输送给数据控制器,以及

‑ꢀ

发送时钟信号被输送给数据控制器,用于数据信号的读入的同步。

11.根据本发明,时钟发生器适当地设计为,在数据传输循环中在动态运行状态中将时钟脉冲序列的第一时钟周期的第一时钟相位的持续时间设定为长于后续时钟周期的第一时钟相位并且短于为了达到最大差分电压所需的持续时间,在所述动态运行状态中差分时钟信号的出现的最大差分电压小于时钟发送模块的最大差分电压。

12.此外,本发明的任务是创建一种用于在同步串行接口的情况下提高最大线路长度的方法。

13.该任务通过根据权利要求6所述的方法来解决。

14.提出一种用于利用装置经由差分数据通道和差分时钟通道进行同步串行数据传输的方法,所述装置具有接口控制器,以及时钟发送模块和数据接收模块,所述接口控制器具有时钟发生器和数据控制器,其中

‑ꢀ

由时钟发生器产生发送时钟信号,所述发送时钟信号在一个数据传输循环期间包括具有周期持续时间的时钟脉冲序列,

‑ꢀ

所述发送时钟信号被输送给时钟发送模块,所述时钟发送模块将发送时钟信号转换成差分时钟信号,用于经由时钟通道输出,

‑ꢀ

经由差分数据通道到达的差分数据信号被输送给数据接收模块,所述数据接收模块将所述差分数据信号转换成数据信号并且输送给数据控制器,以及

‑ꢀ

发送时钟信号被输送给数据控制器,用于数据信号的读入的同步。

15.根据本发明,时钟发生器(44)适当地设计为,在数据传输循环中在动态运行状态(dyn)中将时钟脉冲序列(tp)的第一时钟周期(t1)的第一时钟相位(th1)的持续时间设定为长于后续时钟周期的第一时钟相位(th)并且短于为了达到最大差分电压(udmax)所需的持续时间,在所述动态运行状态中差分时钟信号(c ,c-)的出现的最大差分电压小于时钟发送模块(50)的最大差分电压(udmax)。

16.其他的优点和设计方案由从属权利要求以及由实施例的描述得出。

附图说明

17.图1示出在随动电子设备中的根据本发明的装置的框图,图2示出根据现有技术在大的线路长度l的情况下发送时钟信号的传输的简化信号图,图3示出在大的线路长度l的情况下发送时钟信号clk_s的根据本发明的传输的简

化信号图,图4a示出根据本发明的时钟发生器的第一实施方式的框图,图4b示出根据本发明的时钟发生器的另一实施方式的框图,以及图4c示出根据本发明的时钟发生器的另一实施方式的框图。

具体实施方式

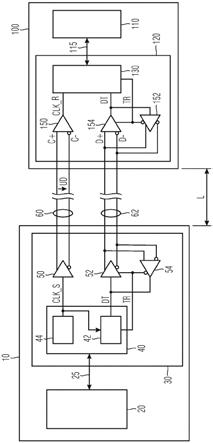

18.图1示出随动电子设备10的框图,该随动电子设备借助接口连接为了数据传输的目的与位置测量设备100连接,该接口连接包括时钟通道60和数据通道62。为了控制数据传输,在随动电子设备10侧设置有主接口30,所述主接口形成根据本发明的装置并且所述主接口与位置测量设备100的从接口120通信。主接口30被实施为同步串行接口,其中信号传输例如根据rs-485标准以差分方式进行。相应地,时钟通道60和数据通道62各具有一个线路对。

19.随动电子设备10是自动化技术的设备、例如机床数控装置、生产机器人的控制装置、位置显示器或其他设备控制装置。所述随动电子设备具有程序控制的中央控制单元20,该中央控制单元被实施为计算机。因此,所述随动电子设备包括至少一个微处理器或微控制器、存储单元,并且可以包括各种其他接口,例如用于连接外围设备(键盘、鼠标、监视器等)。例如用于操控电动机的功率单元可以被分配给控制单元20。除了所示出的主接口30之外,当然还可以设置其他根据本发明的主接口,用于连接其他位置测量设备。

20.位置测量设备100可以实施为旋转编码器、角度测量设备、长度测量设备、测量探头或生成绝对位置值的其他位置测量设备。所述位置测量设备具有位置检测单元110,该位置检测单元适当地设计为通过利用扫描装置扫描测量刻度来生成与位置相关的信号,从这些信号中确定绝对位置值并根据主接口30的请求经由从接口120传输至随动电子设备10。此外,可以在位置测量设备100中设置存储器,在所述存储器中可以存储其他数据。其他数据从随动电子设备10和至随动电子设备10的传输同样可以经由从接口120进行。

21.主接口30包括具有时钟发生器44和数据控制器42的接口控制器40、以及时钟发送模块50、(可选的)数据发送模块52和数据接收模块54。

22.主接口30的接口控制器40通过内部接口25与控制单元20连接。内部接口25允许控制单元20和接口控制器40之间的通信。因此,应由控制单元20发送给位置测量设备100的指令和必要时数据可以传输给接口控制器40。从位置测量设备100到达主接口30处的数据可以从接口控制器40经由内部接口25被转发给控制单元20用于进一步处理。主接口30经由时钟通道60和数据通道62的通信因此由控制单元20经由内部接口25控制。

23.时钟发生器44生成发送时钟信号clk_s,该发送时钟信号一方面被传输至位置测量设备100并且另一方面被输送给数据控制器42。发送时钟信号clk_s在两个数据传输循环之间具有恒定电平,在一个数据传输循环期间,时钟发生器44经由发送时钟信号clk_s输出时钟脉冲序列。

24.数据控制器42一方面适当地设计为将指令和必要时数据传输至位置测量设备100,另一方面设计为接收来自位置测量设备100的数据。双向数据信号dt的输出或读入串行地并且与发送时钟信号clk_s同步地进行。

25.为了经由时钟通道60传输发送时钟信号clk_s,发送时钟信号clk_s被输送给时钟

发送模块50,该时钟发送模块将地参考(单端)信号转换为差分时钟信号,所述差分时钟信号由非反相时钟信号c 和反相时钟信号c-组成。这样的模块也被称为差分驱动器。

26.为了输出(同样地参考)数据信号dt,该数据信号被输送给数据发送模块52,该数据发送模块由此产生差分数据信号,所述差分数据信号包括非反相数据信号d 和反相数据信号d-。为了接收数据,差分数据信号d 、d-被输送给数据接收模块54(差分接收器),该数据接收模块由此又生成地参考数字数据信号dt。为了避免信号冲突,设置有数据方向信号tr,数据控制器42利用该数据方向信号将相应的模块(数据接收模块54或数据发送模块52)切换为有效的或高欧姆的。在接口协议中定义什么时候哪个模块应被切换为有效的。

27.从位置测量设备100侧,差分时钟信号c 、c-被输送给时钟接收模块150,所述时钟接收模块将所述差分时钟信号又转换回地参考信号,该地参考信号作为接收器时钟信号clk_r被输送给与随动电子设备的接口控制器40对应的接口控制器130,用于同步数据输入或输出。差分数据信号d 、d-一方面被输送给数据接收模块154,所述数据接收模块将差分数据信号转换回地参考数据信号dt并且输送给接口控制器130,另一方面设置有数据发送模块152,所述数据发送模块在相反的数据方向上将要输出的数据信号dt转换成差分数据信号d 、d-,用于传输至随动电子设备10。这里,数据方向也通过根据接口协议被切换的数据方向信号tr来设定。

28.随动电子设备10的到达从接口120处的数据请求指令又经由内部接口115被输送给位置检测单元110,该位置检测单元提供所请求的数据并将所述数据转发给从接口120。到达的数据同样经由内部接口120被转发至位置检测单元110并在那里被处理或存储。

29.所示出的位置测量设备100因此适合于执行根据ep 0 660 209 a1的双向数据传输。

30.替代地,位置测量设备100也可以根据ep 0 171 579 a1来实施。在这种情况下,可以省去数据接收模块154(以及随动电子设备的对应的数据发送模块52),使得单向地进行数据传输。

31.时钟通道60在两种情况下都是单向的,即时钟信号clk_s 从主接口30被传输至从接口120。根据同步串行数据传输的基本原理,串行传输的数据位在数据通道62上的同步经由发送时钟信号clk_s进行,所述发送时钟信号经由时钟通道60传输,其中在一个数据传输循环期间经由发送时钟信号clk_s输出的时钟脉冲序列的每个时钟周期传输或读取一个数据位。这对于进一步考虑具有以下结果:仅时钟脉冲序列的频率是随动电子设备10和位置测量设备100之间的可实现的线路长度l的限制因素,因为在数据信号dt中可能出现的最高频率仅仅对应于发送时钟信号clk_s的时钟频率的一半。换言之,只要发送时钟信号clk_s和数据信号dt的传输路径(差分驱动器、线路对、差分接收器)具有很大程度上相同的特性,当在接收器侧(从位置测量设备100侧)可以恢复发送时钟信号clk_s的时钟脉冲序列(作为接收时钟信号clk_r)时,就可以假定安全的数据传输。

32.图2示出根据现有技术在大的线路长度l的情况下发送时钟信号clk_s从随动电子设备10至位置测量设备100的传输的简化信号图。应指出的是,未示出在位置测量设备100中重建的接收时钟信号clk_r的时间延迟,该时间延迟由线路长度l产生。仅示出从位置测量设备100侧的差动传输和重建的影响。

33.在数据传输的持续时间中在常规时钟发生器中产生的发送时钟信号clk_s的时钟

脉冲序列具有由周期持续时间t决定的恒定频率。时钟周期是对称的,即每个周期的高相位th和低相位tl的长度相同,它们的持续时间对应于t/2。

34.在没有进行数据传输的时候,发送时钟信号clk_s具有恒定的逻辑电平,在所示出的示例中具有低电平。作为由此的结果,差分时钟信号c 、c-示出最大差分电压udmax。由此在位置测量设备100中恢复的接收时钟信号clk_r同样具有恒定的逻辑低电平。时钟通道60因此处于静态运行状态stat中。在传输时钟脉冲序列、即进行数据传输的时候,在大的线路长度l的情况下在时钟序列脉冲的信号周期的相位中不再达到最大差分电压udmax,即时钟通道60的线路对的重新加载过程相互交融(gehen ineinander

ꢀü

ber)。只有在数据传输循环之后,当时钟信号clk_s再次占据静态电平时,线路对才再次被加载直至最大差分电压udmax。从为了数据传输输出第一时钟脉冲的时刻起,直至在数据传输之后再次达到静态运行状态stat,时钟通道60处于动态运行状态dyn中。

35.从时钟接收模块150从非反相时钟信号c 和反相时钟信号c-重建的接收时钟信号clk_r中可以获悉,通过在数据传输的时钟序列的第一脉冲(在所示出的示例中第一高相位th1)中必须被重新加载以便实现接收时钟信号clk_r的电平变换的较高差分电压,缩短重建的第一脉冲(第一高相位th1)的脉冲持续时间。通过在第一脉冲结束时由此得到的较小差分电压还产生重建信号的第一低相位tl1的轻微延长,其他脉冲很大程度上对应于发送时钟信号clk_s的时钟脉冲序列。

36.接收时钟信号clk_r的第一高相位th1的缩短导致,时钟信号不再能够正确地被评估,使得在数据传输中出现错误。

37.图3示出在大的线路长度l的情况下根据本发明形成的发送时钟信号clk_s从随动电子设备10至位置测量设备100的传输的简化信号图。数据传输循环在动态运行状态dyn中进行,即未达到差分时钟信号c 、c-的最大差分电压udmax。为了产生发送时钟信号clk_s,时钟发生器44现在根据本发明被设计为大体上延长数据传输循环的时钟脉冲序列tp的第一时钟周期t1的第一时钟相位的持续时间,在所示出的示例中延长第一高相位th1,使得从位置测量设备100侧再次能够评估重建的时钟脉冲序列的第一时钟周期t1的对应的时钟相位(高相位th1)。但是另一方面,第一时钟相位的持续时间(第一高相位th1)也不允许被延长到差分时钟信号c 、c-达到最大差分电压udmax的程度。

38.该解决方案基于以下认识:如果发送时钟信号clk_s的时钟脉冲序列tp的频率保持不变,则在提高线路长度l的情况下只由时钟脉冲序列的第一时钟相位得到错误,而在接收器侧(即从位置测量设备100侧)可以正确地恢复所有其他时钟相位。

39.不仅从随动电子设备10侧而且从位置测量设备100侧的数据信号dt的发送和接收进一步与发送时钟信号clk_s或接收时钟信号clk_r的所分配的时钟边沿同步地进行。因此不需要数据控制器42(以及必要时接口控制器130)的适配。因此在图3中仅勾画了数据信号dt。在所示出的情况下,在接收时钟信号clk_r的下降沿中进行数据信号dt的采样。

40.图4a示出根据本发明的时钟发生器44的第一实施方式的框图。该时钟发生器具有时钟输出单元46以及至少一个寄存器48。

41.时钟输出单元46适当地设计为输出发送时钟信号clk_s。为此,时钟脉冲序列tp的第一时钟相位(第一高相位th1)的持续时间被存储在寄存器48中。在至少一个其他寄存器49中可以存储关于时钟脉冲序列tp的规则时钟脉冲的信息,例如高相位th和低相位tl的持

续时间,或者在对称时钟信号的情况下,周期持续时间t。工作时钟信号clk以及发起时钟脉冲序列tp的输出的启动信号start被输送给时钟输出单元46,所述工作时钟信号用作用于产生时钟脉冲序列tp的时基。

42.为了产生时钟脉冲序列tp,例如可以在时钟输出单元46中设置计数器,该计数器在工作时钟信号clk的时间帧中计数并分别在存储在寄存器48、49中的值的持续时间中输出所需的逻辑电平。

43.有利地,寄存器48的值可以由随动电子设备10的控制单元20写入。以此方式,与不同的线路长度l、线缆规格、发送时钟信号clk_s的频率等的适配是可能的。

44.第一时钟相位的持续时间的确定可以通过计算、测量或逐步逼近(迭代法)进行。

45.图4b示出根据本发明的时钟发生器44的一种替代实施方式的框图。这里,线路长度l被录入寄存器48中,并且时钟输出单元46通过计算或通过从表格中选择来确定第一时钟相位的所需的持续时间,所述表格的值有利地已经在制造商侧被确定并存储。在发送时钟信号clk_s的时钟频率可变的情况下,该时钟频率同样可以被考虑,例如其方式是:高相位th和/或低相位tl的持续时间或周期持续时间t被存储在其他寄存器49中并被输送给时钟输出单元46。

46.图4c示出根据本发明的时钟发生器44的另一替代实施方式的框图。这里,仅常数k被存储在寄存器48中,根据所述常数,时钟输出单元46设定发送时钟信号clk_s的第一时钟相位th1的持续时间。在此情况下,可以涉及乘法器,该乘法器基于规则时钟相位th规定第一时钟相位th1的延长,使得适用:th1=k*th。常数k被选择为使得对于发送时钟信号clk_s的时钟脉冲序列tp的至少一个频率,直至所定义的最大线路长度,实现无错误的传输,其中最大线路长度长于在没有根据本发明的改进的主接口30的情况下可实现的线路长度。为了实现与现有技术相比更大的线路长度l,第一时钟相位的被证明的值是发送时钟信号clk_s的规则时钟相位th的持续时间的两倍。如果第一时钟相位是在图3中所示出的高相位th1,则适用:th1=2*th。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。