1.本发明涉及芯片技术领域,具体地涉及一种横向双扩散金属氧化物半导体场效应管及其制作方法。

背景技术:

2.互补金属氧化物半导体(complementary metal oxide semiconductor)cmos是造大规模集成电路芯片用的一种技术。在28nm及以下的cmos工艺都采用高介电常数电介质金属栅极(high-kmetalgate)工艺,并且以低介电常数电介质(low-k)材料作为后端布线隔离。

3.在高压功率集成电路中,采用横向双扩散金属氧化物半导体场效应管(lateral double-diffused mosfet,ldmosfet)可以满足耐高压、实现功率控制等方面的要求。

4.通常ldmosfet要与cmos工艺集成在一起,形成单片集成工艺(例如,bcd工艺或者cd工艺),ldmosfet还需要有high-kmetalgate工艺。现有的ldmosfet没有high-kmetalgate工艺。

技术实现要素:

5.本发明实施例的目的是提供一种高介电常数电介质金属栅极横向双扩散金属氧化物半导体场效应管,该高介电常数电介质金属栅极横向双扩散金属氧化物半导体场效应管具有high-kmetalgate工艺。

6.为了实现上述目的,本发明实施例提供一种横向双扩散金属氧化物半导体场效应管,包括半导体衬底、源极区、漏极区、栅极区、浅槽隔离区、p型体区以及位于所述半导体衬底上的n型阱区、p型阱区和n型漂移区,所述栅极区为高介电常数电介质金属栅极,所述浅槽隔离区为低介电常数电介质浅槽隔离。

7.可选的,所述低介电常数电介质浅槽隔离的介电常数为2.5~3。

8.可选的,所述高介电常数电介质金属栅极包括金属栅极和高介电常数电介质层,其中,所述金属栅极通过所述高介电常数电介质层与所述p型体区和所述n型漂移区的上方连接。

9.可选的,所述高介电常数电介质层的介电常数为25~30。

10.可选的,所述横向双扩散金属氧化物半导体场效应管还包括n型埋层和p型外延层,其中,所述n型埋层位于所述n型阱区的下方,所述p型外延层位于所述p型阱区的下方。

11.可选的,所述p型阱区包括第一p型阱区和第二p型阱区,所述第一p型阱区和所述第二p型阱区分别位于所述n型阱区的两侧并与所述n型阱区连接。

12.可选的,所述p型体区和所述n型漂移区位于所述n型阱区的上方。

13.可选的,所述n型漂移区包括第一n型漂移区和第二n型漂移区,所述第一n型漂移区和所述第二n型漂移区分别位于所述p型体区的两侧。

14.可选的,所述漏极区位于所述n型漂移区上方,所述源极区位于所述p型体区上方。

15.本发明实施例还提供一种横向双扩散金属氧化物半导体场效应管的制作方法,所述横向双扩散金属氧化物半导体场效应管的制作方法包括:在半导体衬底的选定区域中形成n型阱区和p型阱区;形成低介电常数电介质浅槽隔离区;在所述半导体衬底的选定区域中形成p型体区和n型漂移区;在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区,在所述n型漂移区上方形成漏极区,在所述p型体区上方形成源极区。

16.可选的,所述在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区包括:在所述p型体区和所述n型漂移区的上方通过原子沉积形成高介电常数电介质层;在所述高介电常数电介质层上方通过物理气相沉积形成金属栅极。

17.可选的,在所述在半导体衬底的选定区域中形成n型阱区和p型阱区之前,所述横向双扩散金属氧化物半导体场效应管的制作方法还包括:在所述半导体衬底上形成n型埋层和p型外延层,所述n型埋层位于所述n型阱区的下方,所述p型外延层位于所述p型阱区的下方。

18.本发明实施例还提供一种横向双扩散金属氧化物半导体场效应管,包括半导体衬底、源极区、漏极区、栅极区、浅槽隔离区、p型体区以及位于所述半导体衬底上的n型阱区、p型阱区和n型漂移区,所述横向双扩散金属氧化物半导体场效应管还包括低介电常数电介质层,其中,所述栅极区为高介电常数电介质金属栅极,所述低介电常数电介质层位于所述高介电常数电介质金属栅极和所述n型漂移区之间。

19.可选的,所述低介电常数电介质层的介电常数为2.5~3,所述浅槽隔离区的介电常数为3.9~4。

20.可选的,所述高介电常数电介质金属栅极包括金属栅极和高介电常数电介质层,其中,所述金属栅极通过所述高介电常数电介质层与所述p型体区和所述n型漂移区的上方连接。

21.可选的,所述高介电常数电介质层的介电常数为25~30。

22.可选的,所述横向双扩散金属氧化物半导体场效应管还包括n型埋层和p型外延层,其中,所述n型埋层位于所述n型阱区的下方,所述p型外延层位于所述p型阱区的下方。

23.可选的,所述p型阱区包括第一p型阱区和第二p型阱区,所述第一p型阱区和所述第二p型阱区分别位于所述n型阱区的两侧并与所述n型阱区连接。

24.可选的,所述p型体区和所述n型漂移区位于所述n型阱区的上方。

25.可选的,所述n型漂移区包括第一n型漂移区和第二n型漂移区,所述第一n型漂移区和所述第二n型漂移区分别位于所述p型体区的两侧。

26.可选的,所述漏极区位于所述n型漂移区上方,所述源极区位于所述p型体区上方。

27.本发明实施例还提供一种横向双扩散金属氧化物半导体场效应管的制作方法,所述横向双扩散金属氧化物半导体场效应管的制作方法包括:在半导体衬底的选定区域中形成n型阱区和p型阱区;形成浅槽隔离区;在n型漂移区的上方形成低介电常数电介质层;在所述半导体衬底的选定区域中形成p型体区和n型漂移区;在所述p型体区和所述低介电常数电介质层上方形成高介电常数电介质金属栅极区,在所述n型漂移区上方形成漏极区,在所述p型体区上方形成源极区。

28.可选的,所述在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区包括:在所述p型体区和所述n型漂移区的上方通过原子沉积形成高介电常数电介质

层;在所述高介电常数电介质层上方通过物理气相沉积形成金属栅极。

29.可选的,在所述在半导体衬底的选定区域中形成n型阱区和p型阱区之前,所述横向双扩散金属氧化物半导体场效应管的制作方法还包括:在所述半导体衬底上形成n型埋层和p型外延层,所述n型埋层位于所述n型阱区的下方,所述p型外延层位于所述p型阱区的下方。

30.通过上述技术方案,本发明实施例提供的横向双扩散金属氧化物半导体场效应管ldmosfet,其栅极区为高介电常数电介质金属栅极,所述浅槽隔离区为低介电常数电介质浅槽隔离,具有high-kmetalgate工艺,特别是能与28nm以下的cmos工艺兼容。

31.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

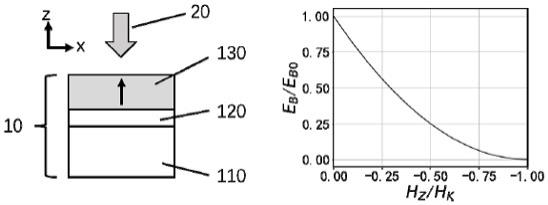

32.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:图1是本发明实施例提供的一种横向双扩散金属氧化物半导体场效应管的结构示意图;图2是本发明实施例提供的一种横向双扩散金属氧化物半导体场效应管的制作方法的流程示意图;图3a-3e为图1所示的ldmosfet各制作环节的结构示意图;图4为本发明实施例提供的另一种横向双扩散金属氧化物半导体场效应管的结构示意图;图5是本发明实施例提供的另一种横向双扩散金属氧化物半导体场效应管的制作方法的流程示意图;图6a-6c为图4所示的ldmosfet各制作环节的结构示意图。

33.附图标记说明100-半导体衬底,101-栅极区,102-源极区,103-漏极区,104

‑ꢀ

p型体区,105a/105b-n型漂移区,106-n型阱区,107a/107b

‑ꢀ

p型阱区,108-n型埋层,109-p型外延层,110-浅槽隔离区,111-低介电常数电介质层。

具体实施方式

34.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

35.图1是本发明实施例提供的一种横向双扩散金属氧化物半导体场效应管的结构示意图,请参考图1,该横向双扩散金属氧化物半导体场效应管ldmosfet可以包括半导体衬底100、源极区102、漏极区103、栅极区101、浅槽隔离区110、p型体区104以及位于所述半导体衬底100上的n型阱区106、p型阱区(107a/107b)和n型漂移区(105a/105b)。

36.其中,所述栅极区101为高介电常数电介质金属栅极,所述浅槽隔离区110为低介电常数电介质浅槽隔离。

37.本发明实施例优选的低介电常数电介质浅槽隔离110(即低k电介质)的介电常数可以为2.5~3。

38.本发明实施例提供的ldmosfet具有high-kmetalgate工艺,特别是能与28nm以下的cmos工艺兼容。

39.本发明实施例优选的高介电常数电介质金属栅极包括金属栅极和高介电常数电介质层,其中,所述金属栅极通过所述高介电常数电介质层与所述p型体区104和所述n型漂移区(105a/105b)的上方连接。

40.其中,高介电常数电介质层(即高k电介质)的介电常数可以为25~30。

41.优选的,所述横向双扩散金属氧化物半导体场效应管ldmosfet还可以包括n型埋层108和p型外延层109,其中,所述n型埋层108位于所述n型阱区106的下方,所述p型外延层109位于所述p型阱区(107a/107b)的下方。

42.本发明实施例优选的p型阱区(107a/107b)可以包括第一p型阱区(例如,107a)和第二p型阱区(例如,107b),所述第一p型阱区107a和所述第二p型阱区107b分别位于所述n型阱区106的两侧并与所述n型阱区106连接。

43.进一步地,所述p型体区104和所述n型漂移区位于所述n型阱区(105a/105b)的上方。所述n型漂移区(105a/105b)可以包括第一n型漂移区(例如,105a)和第二n型漂移区(例如,105b),所述第一n型漂移区105a和所述第二n型漂移区105b分别位于所述p型体区104的两侧。所述漏极区103位于所述n型漂移区(105a/105b)上方,所述源极区102位于所述p型体区104上方。

44.图2是本发明实施例提供的一种横向双扩散金属氧化物半导体场效应管的制作方法的流程示意图。该横向双扩散金属氧化物半导体场效应管的制作方法可以用于制作如图1所示的ldmosfet,图3a-3e为图1所示的ldmosfet各制作环节的结构示意图,结合图2、及图3a-3e,所述制作方法可以包括以下步骤:步骤s110:在半导体衬底的选定区域中形成n型阱区和p型阱区。

45.优选的,在步骤s110之前,所述横向双扩散金属氧化物半导体场效应管的制作方法还包括:在所述半导体衬底上形成n型埋层和p型外延层,所述n型埋层位于所述n型阱区106的下方,所述p型外延层位于所述p型阱区(107a/107b)的下方。

46.以示例说明,请参考图3a,可以在半导体衬底100(例如,p-type silicon 衬底substrate),氧化一层sio2了;经过光刻, n-type离子注入(例如,通过锑或砷重掺杂离子注入),再经过去胶,退火等工艺,形成n型埋层108(n-typeburiedlayer,nbl);后外延生长一层p型外延层(例如,p-typesi)。

47.接着,在半导体衬底100氧化一层sio2;经过hvnw光刻, n-type 离子注入,形成n型阱区106(例如,hvnw区),去胶;再经过hvpw光刻,p-type离子注入,形成p型阱区(107a/107b)(例如,hvpw区),去胶;再进行高温推进,则可以形成如图3b所示的结构。

48.步骤s120:形成低介电常数电介质浅槽隔离区。

49.请参考图3c,承接上述示例,去除sio2氧化层,然后再次氧化一层padsio2;化学气相沉积(cvd)si3n4;在有源区(aa)光刻,再经过干法刻蚀si3n4和sio2,干法刻蚀silicon,形成浅槽隔离区110(shallowtrenchisolation,sti),去胶;再进行stiliner氧化,化学气相沉积(cvd)low-k介质层,即可以形成低介电常数电介质浅槽隔离区,sti高温退火,化学

机械抛光制程(chemical mechanical polishing,cmp)low-k介质层,si3n4湿法去除,湿法去除padsio2层。

50.本发明实施例优选的低介电常数电介质浅槽隔离的介电常数可以选择2.5~3。即图中的low-k介质层,主要成分是sio2,介电常数在2.5左右,而纯sio2的介电常数可以选择3.9。

51.步骤s130:在所述半导体衬底的选定区域中形成p型体区和n型漂移区。

52.承接上述示例,在图3c所示的结构上热氧化一层薄的sio2,光刻p型体区104(例如,p-body区),p-type离子注入后形成p-body区,去胶;接着,光刻n型漂移区(105a/105b)(例如,nrf区),n-type离子注入形成nrf区,去胶;高温退火,湿法去除薄的sio2层,则可以形成如图3d所示的结构。

53.步骤s140:在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区,在所述n型漂移区上方形成漏极区,在所述p型体区上方形成源极区。

54.优选的,所述在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区可以包括:在所述p型体区和所述n型漂移区的上方通过原子沉积形成高介电常数电介质层;在所述高介电常数电介质层上方通过物理气相沉积形成金属栅极。

55.承接上述示例,在图3d所示的结构上热氧化一层薄氧化层,通过原子层沉积(atomic layer deposition,ald)淀积高介电常数电介质层(high-k栅介质层),例如hfox,然后通过物理气相沉积(physical vapor deposition,pvd)形成金属栅极,例如,tantalum等通过栅光刻,金属栅干法刻蚀,high-k介质层刻蚀,形成金属栅极;接着,分别是n 和p 光刻,重掺杂n 和p 离子注入,退火,形成n 和p 源漏区和保护环,最后形成如图3e所示的ldmosfet结构。

56.其中,高介电常数电介质层(high-k)的介电常数可以为25~30。

57.图4为本发明实施例提供的另一种横向双扩散金属氧化物半导体场效应管的结构示意图,请参考图4,该横向双扩散金属氧化物半导体场效应管ldmosfet可以包括半导体衬底100、源极区102、漏极区103、栅极区101、浅槽隔离区110、p型体区104以及位于所述半导体衬底100上的n型阱区106、p型阱区(107a/107b)和n型漂移区(105a/105b),所述横向双扩散金属氧化物半导体场效应管ldmosfet还包括低介电常数电介质层111。

58.其中,所述栅极区101为高介电常数电介质金属栅极,所述低介电常数电介质层111位于所述高介电常数电介质金属栅极和所述n型漂移区(105a/105b)之间。

59.本发明实施例优选的低介电常数电介质层111的介电常数可以为2.5~3;浅槽隔离区110(成分例如为纯sio2)的介电常数可以为3.9~4。

60.请结合图1和图4,相比于图1所示的ldmosfet,图4所述的ldmosfet,场板下的介质层采用low-k材料,可以减少台阶。

61.本发明实施例优选的高介电常数电介质金属栅极包括金属栅极和高介电常数电介质层,其中,所述金属栅极通过所述高介电常数电介质层与所述p型体区104和所述n型漂移区(105a/105b)的上方连接。

62.其中,高介电常数电介质层的介电常数可以为25~30。

63.优选的,所述横向双扩散金属氧化物半导体场效应管ldmosfet还可以包括n型埋层108和p型外延层109,其中,所述n型埋层108位于所述n型阱区106的下方,所述p型外延层

位于所述p型阱区(107a/107b)的下方。

64.本发明实施例优选的p型阱区包括第一p型阱区和第二p型阱区,所述第一p型阱区和所述第二p型阱区分别位于所述n型阱区的两侧并与所述n型阱区连接。

65.本发明实施例优选的p型阱区(107a/107b)可以包括第一p型阱区(例如,107a)和第二p型阱区(例如,107b),所述第一p型阱区107a和所述第二p型阱区107b分别位于所述n型阱区106的两侧并与所述n型阱区106连接。

66.进一步地,所述p型体区104和所述n型漂移区位于所述n型阱区(105a/105b)的上方。所述n型漂移区(105a/105b)可以包括第一n型漂移区(例如,105a)和第二n型漂移区(例如,105b),所述第一n型漂移区105a和所述第二n型漂移区105b分别位于所述p型体区104的两侧并与所述p型体区104连接。所述漏极区103位于所述n型漂移区(105a/105b)上方,所述源极区102位于所述p型体区104上方。

67.图5是本发明实施例提供的另一种横向双扩散金属氧化物半导体场效应管的制作方法的流程示意图。该横向双扩散金属氧化物半导体场效应管的制作方法可以用于制作如图4所示的ldmosfet,图6a-6c为图4所示的ldmosfet各制作环节的结构示意图,结合图5、图3a-3b及图6a-6c,所述制作方法可以包括以下步骤:步骤s210:在半导体衬底的选定区域中形成n型阱区和p型阱区。

68.优选的,在步骤s210之前,所述横向双扩散金属氧化物半导体场效应管的制作方法还包括:在所述半导体衬底上形成n型埋层和p型外延层,所述n型埋层位于所述n型阱区的下方,所述p型外延层位于所述p型阱区的下方。

69.以示例说明,请参考图3a,可以在半导体衬底100(例如,p-type silicon 衬底substrate),氧化一层sio2了;经过光刻, n-type离子注入(例如,通过锑或砷重掺杂离子注入),再经过去胶,退火等工艺,形成n型埋层108(n-typeburiedlayer,nbl);后外延生长一层p型外延层(例如,p-typesi)。

70.接着,在半导体衬底100氧化一层sio2;经过hvnw光刻, n-type 离子注入,形成n型阱区106(例如,hvnw区),去胶;再经过hvpw光刻,p-type离子注入,形成p型阱区(107a/107b)(例如,hvpw区),去胶;再进行高温推进,则可以形成如图3b所示的结构。

71.步骤s220:形成浅槽隔离区。

72.承接上述示例,在图3b所示的结构上去除sio2,然后再次氧化一层padsio2;化学气相沉积(cvd)si3n4;有源区(aa)光刻,再经过干法刻蚀si3n4和sio2,干法刻蚀silicon,形成浅槽隔离区110(shallowtrenchisolation,sti),去胶,再进行stiliner氧化,高等离子体化学气相沉积(highplasmacvd,hdp)sio2 介质层(dielectric),sti高温退火,化学机械抛光制程(chemical mechanical polishing,cmp)sio2 介质层,si3n4湿法去除,湿法去除padsio2层,则可以形成如图6a所示的结构。

73.其中,浅槽隔离区110(例如sio2 介质层)的介电常数可以为3.9~4。

74.步骤s230:在n型漂移区的上方形成低介电常数电介质层。

75.承接上述示例,在图6a所示的结构上热氧化一层薄的sio2, 然后通过化学气相沉积(cvd)制作低介电常数电介质层111,即low-k介质层,其主要成分是sio2。

76.其中,本发明实施例优选的低介电常数电介质层111(即low-k介质层)的介电常数可以为2.5~3。

77.步骤s240:在所述半导体衬底的选定区域中形成p型体区和n型漂移区。

78.承接步骤s230,光刻p型体区104(例如,p-body区),p-type离子注入后形成p-body区,去胶;接着,光刻n型漂移区(105a/105b)(例如,nrf区),n-type离子注入形成nrf区,去胶;高温退火,湿法去除薄的sio2层,则可以形成如图6b所示的结构。

79.步骤s250:在所述p型体区和所述低介电常数电介质层上方形成高介电常数电介质金属栅极区,在所述n型漂移区上方形成漏极区,在所述p型体区上方形成源极区。

80.优选的,所述在所述p型体区和所述n型漂移区的上方形成高介电常数电介质金属栅极区包括:在所述p型体区和所述n型漂移区的上方通过原子沉积形成高介电常数电介质层;在所述高介电常数电介质层上方通过物理气相沉积形成金属栅极。

81.承接上述示例,在图6b所示的结构上热氧化一层薄氧化层,通过原子层沉积(atomic layer deposition,ald)淀积高介电常数电介质层(high-k栅介质层),例如hfox,然后通过物理气相沉积(physical vapor deposition,pvd)形成金属栅极,例如,tantalum等通过栅光刻,金属栅干法刻蚀,high-k介质层刻蚀,形成金属栅极;接着,分别是n 和p 光刻,重掺杂n 和p 离子注入,退火,形成n 和p 源漏区和保护环,最后形成如图6c所示的ldmosfet结构。

82.其中,高介电常数电介质层的介电常数可以为25~30。

83.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

84.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。