1.本发明涉及脉冲整形电路。更具体地,本发明涉及用于具有电子检测器和/或离子检测器等检测器的质谱仪的脉冲整形电路。本发明进一步涉及包括脉冲整形电路的检测器脉冲处理单元,以及包括脉冲整形电路的谱仪,例如质谱仪。

背景技术:

2.在质谱法中,已知各种检测器可检测离子。检测到的离子通常已根据它们的质荷(m/z)比进行滤波和/或分离。在典型的多极质谱仪中,多极(通常但不一定是四极)可以扫描一系列m/z值,用作滤波器。对于每个m/z值(或m/z值的子范围),离子数量是确定的。因此,具有不同m/z值的离子数量是在时间上分离的且是依序确定的。在美国专利us 9,934,954(赛默飞世尔科技)中公开了多极质谱仪的实例,所述美国专利特此以引用的方式并入本文中。

3.扇形场质谱仪能够例如通过施加磁场而在空间中分离离子,所述磁场使离子遵循弯曲轨迹,所述离子的半径取决于它们的m/z值。因此,可以同时确定具有不同m/z值的离子数量。在美国专利us 10,867,780(赛默飞世尔科技和布里斯托大学)中公开了包括离子多集电极的扇形场质谱仪的实例,所述美国专利特此以引用的方式并入本文中。

4.此类质谱仪通常包括:离子源,其用于从样本生成离子束;离子源下游的滤质器,其用以通过离子的质荷比(m/z)从所述束选择离子;滤质器下游的碰撞池,其用以去除干扰离子;碰撞池下游的滤质器;以及滤质器下游的检测器单元。检测器单元可包括用于并行地和/或同时地检测多个不同离子物质的多个离子检测器。

5.已知几种类型的离子检测器,例如法拉第杯、紧凑型离散倍增极(cdd)和二次电子倍增器(sem)。在一些质谱仪中,多个法拉第杯与一种或两种其它类型的离子检测器结合使用,用于大量出现的离子的法拉第杯和用于少量出现的离子的其它类型的离子检测器。

6.冲击法拉第杯的离子可能会使得小电流流过通常具有高电阻的电阻器。电阻器两端的所得电压通常使用电压频率转换器(vfc)转换成表示电压且因此表示离子数量的频率。因此,每个法拉第杯通过其相关联的vfc产生由脉冲组成的输出信号,每秒的脉冲数表示冲击特定法拉第杯的离子数量。

7.其它类型的离子检测器也可能产生脉冲,所述脉冲需要进行计数以确定特定时间段内冲击检测器的离子数量。例如,紧凑型离散倍增极(cdd)和二次电子倍增器(sem)产生表示离子雪崩的脉冲,这些脉冲的数量或频率表示离子数量。

8.为了对由例如二次离子倍增器产生的脉冲数进行计数,必须能够清楚地区分后续脉冲且避免计数假象(artifact),例如所谓的反射脉冲。因此,为了能够可靠地对检测器脉冲进行计数,实际脉冲应具有最小的高度和持续时间,同时应抑制假象。

技术实现要素:

9.本发明旨在提供一种能够从模拟检测器接收检测器脉冲并将已整形脉冲提供到

计数器的电子电路,所述电子电路可靠、简单、经济又有效。

10.因此,本发明提供一种用于对谱仪中的检测器脉冲进行整形的脉冲整形电路,所述脉冲整形电路包括:

[0011]-电路输入端,其用于从模拟离子检测器接收检测器脉冲,

[0012]-触发器,其用于从所述电路输入端接收检测器脉冲并产生输出脉冲,

[0013]-延迟单元,其用于从所述触发器接收输出脉冲并将已延迟输出脉冲馈送到所述触发器的复位输入端,所述延迟单元被配置成用于确定所述输出脉冲的持续时间和所述输出脉冲之间的间隔的最小持续时间,以及

[0014]-电路输出端,其用于将所述输出脉冲或所述已延迟输出脉冲提供到计数器。

[0015]

通过使用触发器和延迟单元,有可能提供具有少量部件的经济又可靠的脉冲整形电路。所述触发器接收检测器脉冲并输出可馈送到计数器的脉冲。所述脉冲整形电路的创造性特征是延迟单元,其被配置成延迟所述触发器的输出脉冲并将所述输出脉冲馈送到所述触发器的复位输入端。因此,所述触发器产生的每个输出脉冲都使所述触发器在一定时间延迟后复位,时间延迟量由延迟单元确定。应理解,触发器的复位会使触发器的输出脉冲结束,即触发器的复位可以使触发器的输出电平从逻辑高电平变为逻辑低电平。因此,触发器的输出脉冲的持续时间由延迟单元确定。

[0016]

复位触发器且因此使触发器的输出电平从高电平(逻辑1)变为低电平(逻辑0)会使得复位输入端的输入电平在一定时间延迟后达到低电平,时间延迟量由延迟单元确定。通常,触发器的输出电平变成高电平与复位输入端处的输入电平变成高电平之间的时间延迟与触发器的输出电平变成低电平与复位输入端处的输入电平变成低电平之间的时间延迟大体相同,尽管可能并非在所有实施例中都是这种情况。

[0017]

通过延迟触发器的复位并随后延迟其设置,对触发器的输出脉冲进行整形。也就是说,输出脉冲既具有持续时间又具有之间的最小间隔,持续时间和最小间隔均由延迟单元确定且因此输出脉冲由本发明的脉冲整形电路整形。

[0018]

上文的讨论是在假设正逻辑的情况下提供的;当使用负逻辑时,本领域的技术人员将能够容易地进行任何必要的调整。

[0019]

在本发明的脉冲整形电路中,延迟单元的输出端可以经由具有两种定义输出状态的组件耦合到触发器的复位输入端。通过使用具有两种定义输出状态的组件,可以保证复位输入端接收稳定的电压,使得触发器的复位不会在不希望的时间点终止。

[0020]

具有两种定义输出状态的组件,例如数字组件,可以包括比较器,即比较两个电压(或电流)并输出指示哪一者更大的数字信号的组件。优选地,具有两种定义输出状态的组件包括施密特触发器。

[0021]

脉冲整形电路输入端可以经由具有两种定义输出状态的组件耦合到触发器。也就是说,具有两种定义输出状态的组件,例如数字组件,可布置在脉冲整形电路的输入端与触发器之间,从而将触发器间接连接到脉冲整形电路的输入端。这样做的优点在于触发器的输入端可以接收更好定义的输入电压。

[0022]

触发器的输出可以经由具有两种定义输出状态的组件耦合到电路输出端。尽管这也有助于更好地对脉冲整形电路输出的脉冲进行整形,但此额外组件的主要目的在于用作触发器与电路输出端以外的任何组件之间的缓冲器。

[0023]

在实施例中,延迟单元的输出可以经由具有两种定义输出状态的组件耦合到电路输出端。具体地说,当在延迟单元中使用电容器时,延迟单元的输出电压可能不会呈现出具有平直边沿的脉冲。在这种情况下,具有两种定义输出状态的组件——例如数字组件,可以产生更好定义的脉冲边沿。

[0024]

例如,具有两种定义输出状态的组件可以包括数字组件,例如或门或者非门的串联布置。在实施例中,具有两种定义输出状态的组件可包括比较器。尽管可使用常规比较器,但优选的是使用施密特触发器,因为此类组件通过抑制小信号波动有效地降低噪声。

[0025]

在脉冲整形电路的实施例中,延迟单元包括电阻器和电容器。通过使用电阻器和电容器,可实现非常简单且经济又有效的延迟单元。优选地,延迟单元包括电阻器和电容器的串联布置。在一些实施例中,延迟单元仅由电阻器和电容器的串联布置组成,电容器的一个端优选地连接到接地。

[0026]

在本发明的脉冲整形电路中,触发器可包括d触发器,在此情况下,触发器的复位输入端是清零端。众所周知,d触发器通常具有标记为d的输入端、标记为q的输出端、标记为清零或r(复位)的复位输入端以及时钟输入端。

[0027]

在实施例中,触发器是d触发器,触发器的d输入端连接到逻辑“1”电平。d触发器是广泛可用的且具有优越的特性。当触发器由d触发器构成时,触发器的时钟输入端可连接到脉冲整形电路输入端。

[0028]

可以替代地使用其它类型的触发器。在实施例中,脉冲整形电路的触发器是sr触发器,并且触发器的复位输入端是r端。众所周知,sr触发器具有置位(s)输入端和复位(r)输入端。

[0029]

在其中触发器是sr触发器的实施例中,脉冲整形电路可进一步包括布置在电路输入端与触发器之间的与门,所述与门被布置成接收触发器的反相已延迟输出脉冲。包括与门的脉冲整形电路可进一步包括布置在延迟单元和与门之间的反相器。这允许将检测器脉冲选择性地馈送到sr触发器,也就是说,如果r输入端处的电压为低,则(正或高)输入脉冲可仅提供到触发器的s输入端,从而避免触发器的任何未定义状态。

[0030]

本发明进一步提供一种检测器脉冲处理单元,其包括如上文所描述的脉冲整形电路。在实施例中,所述检测器脉冲处理单元可包括:

[0031]-任选放大器,其用于放大模拟检测器脉冲,

[0032]-如上文所描述的脉冲整形电路,其用于对可或不可放大的检测器脉冲进行整形,以及

[0033]-计数器,其用于对已整形的检测器脉冲进行计数。

[0034]

本发明另外提供一种谱仪,例如质谱仪,其包括如上文所描述的检测器脉冲处理单元。谱仪可以是电感耦合等离子体(icp)质谱仪。包括如上文所描述的检测器脉冲处理单元的谱仪可以进一步包括离子源、束聚焦单元、扇形磁场单元、多极单元、检测器单元和检测器信号处理单元中的至少一个,其中检测器脉冲处理单元可以是检测器信号处理单元的一部分。

附图说明

[0035]

图1示意性地示出了其中可应用本发明的质谱仪的示例性实施例。

[0036]

图2更详细地示意性地示出了图1的质谱仪的信号处理单元。

[0037]

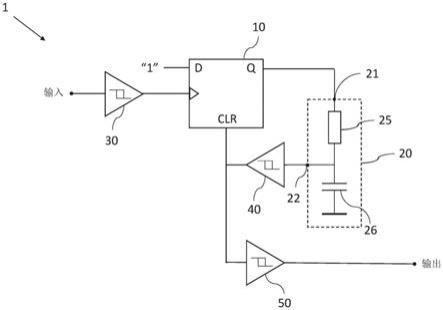

图3示意性地示出了根据本发明的脉冲整形电路的第一实施例。

[0038]

图4示意性地示出了根据本发明的脉冲整形电路的第二实施例。

[0039]

图5示意性地示出了根据本发明的脉冲整形电路的第三实施例。

[0040]

图6示意性地示出了根据本发明的脉冲整形电路的第四实施例。

[0041]

图7示意性地示出了根据本发明的脉冲整形电路的第五实施例。

[0042]

图8示意性地示出了根据本发明的脉冲整形电路的第六实施例。

[0043]

图9示意性地示出了根据本发明的脉冲整形电路的第七实施例。

[0044]

图10示意性地示出了根据本发明的脉冲整形电路的第八实施例。

[0045]

图11示意性地示出了可能出现在根据本发明的脉冲整形电路的实施例中的脉冲。

[0046]

图12也示意性地示出了可能出现在根据本发明的脉冲整形电路的实施例中的脉冲。

具体实施方式

[0047]

本发明提供一种脉冲整形电路,其被设计成抑制由检测器——例如电子检测器或离子检测器——产生的寄生脉冲。本发明的脉冲整形电路进一步被设计成产生具有最小脉冲长度的脉冲,以促进对脉冲进行计数。脉冲整形电路将参考谱仪——例如质谱仪、电子能谱仪或光谱仪——来描述。

[0048]

其中可以应用本发明的质谱仪借助于实例示意性地示出于图1中。质谱仪100示出为包括离子源110、束聚焦单元120、滤质器单元130、检测器单元140和信号处理单元150。离子源110可以是等离子体源,例如电感耦合等离子体(icp)源。离子源110被布置用于产生原始离子束a,所述原始离子束由束聚焦单元120聚焦成聚焦离子束b。束聚焦单元120可以包括本身可能已知的合适的离子光学器件。碰撞/反应池可以选地布置在束聚焦单元120于滤质器单元130之间,和/或布置在滤质器单元130于检测器单元140之间。

[0049]

在滤质器单元130中,包含在离子束b中的离子可以根据其相应质量而分离。如果滤质器单元130包括扇形磁场单元,则进入滤质器单元130的单个聚焦离子束b被分成可以到达检测器单元140的不同检测器的多个离子束c,从而允许单独检测具有不同质量的离子。如果滤质器单元130包括多极单元,例如四极单元或六极单元,则在一定时间段内,仅具有选定范围的质/荷(m/z)值的离子将作为束c离开滤质器单元130并将到达检测器单元140。响应于检测到离子,检测器单元140产生可在信号处理单元150中放大和进一步处理的离子检测信号,从而产生可包含每离子检测器的平均检测频率且因此每离子质量范围的数据信号。

[0050]

图1的质谱仪100的一部分更详细地示出于图2中。具体地说,图2示意性地示出了检测器单元140的一部分和信号处理单元150的一部分。

[0051]

检测器单元140示出为包括二次电子倍增器(sem)141、142和143。检测器单元140可以包括多于三个(或少于三个)二次电子倍增器(sem),以及额外的离子检测器,例如法拉第杯和/或紧凑型离散倍增极(cdd)。

[0052]

众所周知,二次电子倍增器(sem)和类似的离子检测器布置产生脉冲,所述脉冲具有与冲击离子数量成正比的小电压。这些通常介于1mv到10mv范围内的小电压被转换成介

于1v到10v范围内的电压。为此,信号处理单元150包括模拟放大器152。应注意,此处仅示意性地绘出放大器152,且放大器152可以包括具有负反馈环路和其它组件的运算放大器。还应注意,为了图式的简单起见,此处仅示出了单个放大器152,但应理解,检测器单元140的每个检测器141-143可以连接到单独的放大器152。在一些实施例中,两个或更多个检测器可以共享输入电阻器和放大器。

[0053]

放大器152产生具有输出电压v

out

的脉冲,所述输出电压可以明显大于输入电压v

in

,例如大10、100或1000倍。具有此输出电压v

out

的脉冲然后被馈送到脉冲处理单元153,所述脉冲处理单元处理接收到的脉冲以产生具有合适形状和持续时间的脉冲p以供计数器154进行计数。

[0054]

为了确定平均频率,脉冲处理电路可以对某一时间段内的脉冲数进行计数,确定所述时间段的持续时间,并且用脉冲数除以持续时间。

[0055]

如上所述,脉冲处理单元153包括用于对脉冲进行整形,特别是用于消除脉冲之间的伪峰(spurious peak)以及用于提供最小脉冲持续时间以允许对脉冲进行可靠计数的电路。

[0056]

根据本发明的脉冲整形电路的示例性实施例示意性地示出于图3中。可以是图2的脉冲处理单元153的一部分的脉冲整形电路1示出为包括触发器10和延迟单元20。脉冲整形电路1示出为进一步包括脉冲整形电路输入in和脉冲整形电路输出out。延迟单元20示出为包括延迟单元输入21和延迟单元输出22。

[0057]

在所示实例中,延迟单元20包括电阻器25和电容器26的串联布置。电阻器25的第一端连接到延迟单元输入端21,而电阻器25的第二端连接到电容器26的第一端和延迟单元输出端22。在所示实例中,电容器26的第二端连接到接地。延迟单元20的此实施例简单、经济又有效。应理解,可以使用延迟单元的其它实施例,例如,一个或多个电阻器和一个或多个电容器等的其它布置,和/或包含例如延迟线、门和/或触发器等更多数字元件中的一者的布置。

[0058]

在图3的实施例中,触发器10是具有d输入端和q输出端的d触发器(d触发器还可以具有反相q输出端,但本实施例中未使用此端)。触发器10的d输入端连接到表示逻辑“1”电平的电压,通常是相对较高的电压电平,例如正电源电压。因此,逻辑“1”始终存在于d输入端,并将在时钟输入端的每个脉冲处复制到q输出端(在图3中用三角形表示)。

[0059]

触发器10的时钟输入端连接到电路输入in。因此,触发器的状态可在每个接收到的检测器脉冲处改变。如上文参考图2所解释的,此检测器脉冲可以由例如sem检测器141的检测器响应于检测到离子而生成,并且可以由例如放大器152的放大器放大。因此,每个检测器脉冲都会使得d输入端的逻辑“1”出现在q输出端。由于触发器10的q输出端连接到电路输出out,因此这一电路输出out处于表示逻辑“1”的(相对)高电压。

[0060]

触发器10的q输出端还连接到延迟单元输入端21,而延迟单元输出端22连接到清零输入端clr(注意,一些d触发器可以替代地或另外具有反相清零输入端;如果使用此清零输入端,则反相器可以布置在延迟单元输出端22与清零输入端之间)。延迟单元20可以此方式布置,即出现在所述延迟单元的输入端21处的高电压将在预定延迟后出现在其输出端22处。替代地或另外,延迟单元20可以此方式布置,即出现在所述延迟单元的输入端21处的低电压将在预定延迟后出现在其输出端22。

[0061]

在所示实施例中,施加到电阻器25的相对较高的电压(例如正电源电压)将使得电容器26充电。在由电阻器25的电阻和电容器26的电容确定的一定延迟之后,延迟单元20的输出端22且因此触发器的清零输入端clr也将处于此高电压。因此,触发器将清零(即,复位)并且触发器10的输出端q将呈现表示逻辑“0”的低电压(例如接地)。然后,脉冲整形电路输出out也将呈现低电压。

[0062]

当触发器10的输出端q呈现低电压时,在图3所示的实施例中,延迟单元20的输入端21也将呈现低电压。因此,电容器26将开始经由电阻器25放电,从而延迟单元输出端22处的电压且因此触发器10的清零输入端clr处的电压将开始下降。最终,电压将下降到足以使清零输入端clr呈现逻辑“0”电平,从而结束触发器的清零并允许触发器在于时钟输入端接收到的下一脉冲处恢复将d输入端处的逻辑“1”复制到q输出端。

[0063]

因此可以看出,馈送到触发器的时钟输入端的检测器脉冲将在触发器和脉冲整形电路1的输出处产生高电压,且因此产生脉冲。此脉冲将具有由延迟单元20确定的持续时间,如在预定延迟之后触发器将复位,从而产生低电压且因此使得触发器和脉冲整形电路1的输出处不存在脉冲。这种脉冲不存在或脉冲间隔具有也由延迟单元20确定的持续时间。应注意,在此脉冲间隔期间,脉冲整形电路输出端out处可能不会出现脉冲,这是因为触发器10处于清零状态。因此,短的寄生脉冲将被脉冲整形电路1滤波且将不会传输。相反,传输的脉冲具有由延迟单元20确定的最小持续时间,这允许计数器(例如,图2中的计数器154)对这些脉冲可靠地进行计数。

[0064]

应注意,在图3所示的实施例中,脉冲的持续时间将大致等于脉冲间隔的持续时间,但在其它实施例中这些持续时间可能不一定相等。

[0065]

在图3的实施例中,脉冲整形电路输出端out直接连接到触发器10的q输出端。在图4的实施例中,脉冲整形电路输出端out连接到延迟单元输出端22。因此,本实施例可输出的脉冲将被延迟单元延迟。

[0066]

另一实施例示出于图5中。此实施例基本上类似于图3的实施例,并且还包括触发器10和延迟单元20。另外,图5的实施例包括第一施密特触发器30、第二施密特触发器40和第三施密特触发器50。第一施密特触发器30布置在输入端in与触发器10的时钟输入端之间,且用以向时钟输入端提供明确定义的脉冲。第二施密特触发器40布置在延迟单元20的输出端22与触发器10的清零输入端clr之间,且用以更好地定义其中清零输入端接收高(逻辑“1”)电压或低(逻辑“0”)电压的时间点。第三施密特触发器50布置在触发器10的q输出端与脉冲整形电路输出端out之间,特别是布置在延迟单元输入端21与脉冲整形电路输出端out之间,且主要用作脉冲整形电路与例如计数器电路的任何另外的电路之间的缓冲器。

[0067]

尽管所有三个施密特触发器都是任选的,但第二施密特触发器40的存在尤其有利,因为它更好地定义了脉冲持续时间和脉冲间隔持续时间。因此,仅具有第二施密特触发器40的实施例通常优于不具有施密特触发器的实施例,或者优于不具有第二施密特触发器40但具有第一施密特触发器30或第三施密特触发器50的实施例。

[0068]

应注意,每个施密特触发器是具有两种定义输出状态的组件的实例。此组件优选地包括比较器,其将输入电压与参考电压进行比较并且输出两个可能的输出电压中的一者。施密特触发器是比较器的特别有利的实例、是具有滞后作用类型的比较器,所述施密特触发器防止其输出电压随其输入信号改变地过快。然而,在图5的实施例中,可以用两个反

相器的串联布置或例如用另一种类型的比较器来代替施密特触发器中的任一者。

[0069]

图6的实施例类似于图4的实施例,但增加了三个施密特触发器30、40和50。在延迟单元20与脉冲整形电路输出端out之间的信号路径中,第二施密特触发器40和第三施密特触发器50串联布置。此处,第三施密特触发器50主要用作触发器10与输出端out之间的缓冲器,并且可替换为具有两种定义输出状态的另一组件。

[0070]

图7的实施例类似于图6的实施例,不同之处在于使用了反相施密特触发器30、40和50。在此实施例中,延迟单元20的输出端应经由第二施密特触发器40连接到触发器10的反相清零输入端not clr。

[0071]

在上述实施例中,使用了d触发器。然而,本发明不限于d触发器,且可替代地利用其它触发器,例如sr触发器。包括sr触发器的实施例示意性地示出于图8-10中。

[0072]

图8的实施例类似于图3的实施例,并且还包括触发器10和延迟单元20。在图8的实施例中,已用具有输入端s(置位)和r(复位)以及输出端q的sr触发器代替d触发器。如图3所示,触发器输出端q连接到脉冲整形输出端out且连接到延迟单元输入端21。然而,脉冲整形电路输入端in连接到第一触发器输入端s,而延迟单元输出端22连接到第二触发器输入端r。

[0073]

在输入端s处接收到的检测器脉冲将使触发器10置位,从而在输出端q处产生高电压(逻辑“1”)。脉冲整形电路1因此将在其输出端out处产生脉冲。如在图3的实施例中,延迟单元输入端21处的此高电压将在一定延迟之后在延迟单元输出端22处产生高电压,所述延迟单元输出端与触发器的r(复位)输入端耦合。这将复位触发器,因此输出端q将呈现低电压。这将触发延迟单元20中的另一延迟,在所述延迟之后,延迟单元输出端22处的电压且因此r输入端处的电压将再次变低,从而结束复位周期。当复位结束时,触发器能够对其s输入端处的下一脉冲作出响应。

[0074]

尽管图8的实施例可以如此起作用,但其缺点在于可能会出现s输入端和r输入端均携带高电压的情况,因此向s输入端和r输入端提供逻辑“1”,即s=r=“1”。这可能会引起触发器的未定义状态。可以利用额外组件来避免这种情况,如图9所示。图9的实施例与图8的实施例相同,不同之处在于增加了反相器60和与门70。

[0075]

与门70布置在脉冲整形电路输入端in与触发器10的s输入端之间。或非门60与延迟单元输出端22耦合,且因此当复位信号(已延迟输出脉冲)存在时接收所述复位信号。或非门60使复位信号反相并将反相后的复位信号馈送到与门。因此,如果r输入端接收到逻辑“1”(高电压),则反相器60向与门70提供逻辑“0”,从而有效地阻断与门,因此没有逻辑“1”可以馈送到触发器的s输入端。因此消除了s=r=“1”的情况。

[0076]

图10的实施例类似于图9的实施例,不同之处在于增加了三个施密特触发器30、40和50。例如,这些施密特触发器具有与图5中的其对应物基本上相同的功能。应理解,可以从图10的实施例中省略三个施密特触发器30、40和50中的任一者。

[0077]

在图11中,示意性地示出了可能会在本发明的脉冲整形电路的实施例中出现的各种信号。图11所示的信号是:

[0078]

a.脉冲整形电路的输入端处的信号;

[0079]

b.触发器的(反相)清零输入处的信号;

[0080]

c.延迟单元的输出端处的信号;以及

[0081]

d.脉冲整形电路的输出端处的信号。

[0082]

图11所示的信号尤其可能会出现在图7所示的实施例中。

[0083]

可由脉冲整形电路接收且可由放大器(图2中的152)输出的检测器脉冲示出于a处。在所示特定实例中,接收到的检测器脉冲p

in

相对于固定电压为负:在不存在脉冲的情况下,正电压v存在于脉冲整形电路的输入处,而在存在检测器脉冲p

in

的情况下,零(或近零)电压0存在于脉冲整形电路的输入处。在所示实例中,触发器是触发正边沿的触发器且脉冲整形电路在其输入处具有反相元件,例如图7的实施例中的反相施密特触发器30。

[0084]

当第一(反相)检测器脉冲p在时间t1到达触发器的时钟输入时,输出q呈现由高电压表示的值“1”,所述输出q被提供到延迟单元。在图7所示的实施例中,这使得电容器(图6中的26)充电且使得延迟单元的输出端(图7中的22)处的电压升高,如图11中的c所示。延迟单元的此输出信号被提供到触发器的清零输入,任选地经由施密特触发器(图7中的40)。如果此施密特触发器是反相施密特触发器,如图7所示,则可以使用触发器的反相清零输入(not clr)。如果此施密特触发器是非反相施密特触发器,则可以使用触发器的常规(非反相)清零输入(clr)。

[0085]

在时间t2,延迟单元的输出端(图7中的22)处的信号达到使触发器清零(即复位)的值。也就是说,延迟单元的输出端处的上升电压,如c所示,使得耦合到延迟单元的输出端的反相施密特触发器(图7中的40)的输出信号从高电压切换到低电压,如b所示。延迟单元的输出端处的此低电压被提供到触发器的反相清零输入(图7中的not clr),从而使得触发器清零且触发器的(在其输出端q处的)输出信号呈现低电压。从图11中可以看出,触发器的此清零(即复位)发生在由延迟单元确定的延迟δ=(t

2-t1)之后。

[0086]

尽管所使用的特定延迟将取决于应用和所使用的检测器而变化,但典型的延迟可以介于1纳秒到1毫秒的范围内,优选地介于1纳秒到1微秒的范围内,更优选地介于1纳秒到100纳秒的范围内,并且再更优选地介于10纳秒到50纳秒的范围内。本领域的技术人员将认识到,当使用包括电阻器和电容器的串联布置的延迟单元时,时间常量τ可以大致等于延迟δ,其中τ=r.c,其中r是电阻器的电阻且c是电容器的电容。

[0087]

应注意,在图11的实例中,如在图12的实例中,为了图示的清楚起见,忽略由触发器或由任何施密特触发器引起的任何延迟。实际上,这些元素中的每一个都会引起几纳秒(ns)的延迟。因此,总延迟δ将大于由延迟单元引起的且由时间常量τ表示的延迟。在实际实施例中,总延迟δ可以达到例如约30纳秒。

[0088]

由于复位,触发器的输出端q处的低电压被馈送到延迟单元,这会使得延迟单元的输出信号减小,如c所示。在时间t3,延迟单元的输出信号已达到足以使施密特触发器40改变其输出电压的低电压,从而向触发器的反相清零输入提供高电压,如b所示。

[0089]

在图7的实施例中,脉冲整形电路的输出信号基本上是提供到触发器的反相清零输入端的信号的反相(由于图7中的反相施密特触发器50)版本。脉冲整形电路的输出信号如图11中的d所示。可以看出,脉冲整形电路提供了明确定义的输出脉冲p

out

,其具有由延迟单元定义的持续时间。

[0090]

当接收到下一检测器脉冲p

in

时,在时间t4处重复上文所描述的事件。根据本发明的重要方面,脉冲整形电路在每个检测器脉冲p

in

开始之后提供消隐间隔bt。因此,第一消隐间隔在时间t1处开始且在时间t3处结束,而第二消隐间隔在时间t4处开始且在时间t6处结

束。也就是说,从时间t1或t4开始,当检测器脉冲p

in

使触发器的输出端q呈现高电压时,脉冲整形电路对例如反射r的另外的脉冲不敏感。在消隐时间bt的第一部分期间,例如从t4到t5,输出端q已具有对应于逻辑“1”的高电压,因此触发器的时钟输入端处的另外的脉冲将不会改变此状态。在消隐时间bt的第二部分期间,例如从t5到t6,触发器由于b处所示的(反相)清零信号而处于“清零”状态,因此触发器的状态不可改变。

[0091]

因此可以看出,本发明的脉冲整形电路提供了对例如反射和噪声信号的寄生信号不敏感的明确定义的输出信号。

[0092]

图12示出了可能会在本发明的实施例中,例如在图7所示的实施例中出现的信号的另一实例。在图12的实例中,在于时间t1与时间t3之间延伸的第一消隐时间段bt期间出现两个反射r,而在于时间t4与时间t6之间延伸的第二消隐时间段bt期间出现一个反射r。如图11所示,第二消隐时间段的开始由在时间t4处接收到的检测器脉冲p

in

确定。应注意,t4可以在时间t3之后,即在第一消隐时间bt已结束之后的任何时间存在。

[0093]

本领域的技术人员将能够容易地将组件添加到上述实施例或从上述实施例删除组件。例如,可以使用其它类型的触发器或锁存器,例如jk触发器,而不是所示的d触发器和sr触发器。另外,可以使用一个或多个数字元件(例如,所谓的延迟线)或门的串联布置(例如,偶数个串联的非门)以不同方式布置延迟单元或延迟电路。

[0094]

如上所述,具有零个、一个、两个、三个或更多个施密特触发器或等效组件的实施例是可能的。

[0095]

因此,本领域的技术人员将理解,本发明不限于上文所描述的实施例,并且可以在不脱离如所附权利要求所描述的本发明的范围的情况下进行许多增加和修改。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。