一种基于duffing-van der pol忆阻混沌振子的混沌同步电路

技术领域

1.本发明涉及混沌电路领域,尤其涉及一种基于duffing-van der pol忆阻混沌振子的混沌同步电路。

背景技术:

2.忆阻器是一种非线性电路元件,有着天然的非线性和可塑性,对基于忆阻器的duffing-van der pol忆阻混沌振子电路进行同步设计,采用驱动-响应的同步方法,可构建一种基于duffing-van der pol忆阻混沌振子的混沌同步系统。基于duffing-van der pol忆阻混沌振子的混沌同步电路是对混沌系统一种控制方法,该电路具有独特的动力学行为。通过混沌同步控制方法,可以实现两个混沌系统在初始条件不同的情况下输出信号的完全同步,在基于混沌系统的微弱信号检测、保密通信、信号处理等领域中有着重要作用。目前,基于duffing-van der pol忆阻混沌振子的混沌同步控制方法较少,基于混沌振子的混沌同步电路种类有限,通过实现该忆阻混沌系统的同步电路对丰富混沌同步电路库具有很大的现实意义,利用混沌同步系统可以在保密通信、微弱信号检测等领域发挥重要作用。

技术实现要素:

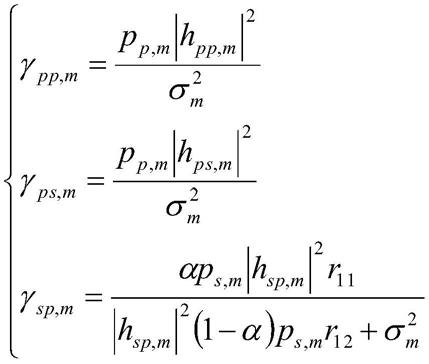

3.为了解决上述问题,本发明提供了一种基于duffing-van der pol忆阻混沌振子的混沌同步电路,该混沌同步电路包括运算放大器u1、运算放大器u2、运算放大器u3、运算放大器u4、运算放大器u5、运算放大器u6、运算放大器u7、运算放大器u8、运算放大器u9、运算放大器u10、运算放大器u11、运算放大器u12、电容c1、电容c2、电容c3、电容c4、电容c5、乘法器a1、乘法器a2、乘法器a3、乘法器a4、乘法器a5、乘法器a6、乘法器a7、乘法器a8、外围电阻以及两个正弦信号源;

4.其中,运算放大器u1的反相输入端分别连接电阻r1的一端、电阻r2的一端、电阻r3的一端、电阻r4的一端、电阻r5的一端和电阻r6的一端,电阻r1的另一端与乘法器a2的输出端相连,电阻r2的另一端与运算放大器u2的输出端相连,电阻r3的另一端与运算放大器u4的输出端相连,电阻r4的另一端与乘法器a3的输出端相连,电阻r5的另一端与正弦信号源v1的正极相连,电阻r6的另一端与运算放大器u1的输出端相连,运算放大器u1的正相输入端接地,运算放大器u1的输出端通过电阻r7与运算放大器u2的反相输入端相连;

5.电阻r10与电容c1并联形成第一并联网络,所述第一并联网络的两端分别连接运算放大器u2的反相输入端和运算放大器u2的输出端;运算放大器u2的正相输入端通过电阻r11接地,运算放大器u2的输出端通过电阻r9与运算放大器u3的反相输入端相连,运算放大器u2的输出端还通过电阻r31与运算放大器u10的正相输入端相连;电阻r8的一端与运算放大器u3的反相输入端相连,电阻r8的另一端与运算放大器u3的输出端相连;运算放大器u3的正相输入端接地,运算放大器u3的输出端通过电阻r12与运算放大器u4的反相输入端相

连;

6.电阻r13与电容c2并联形成第二并联网络,所述第二并联网络的两端分别连接运算放大器u4的反相输入端和运算放大器u4的输出端,运算放大器u4的正相输入端通过电阻r14接地,运算放大器u4的输出端通过电阻r16与运算放大器u5的反相输入端相连;

7.电阻r17的一端与运算放大器u5的反相输入端相连,电阻r17的另一端与运算放大器u5的输出端相连;运算放大器u5的正相输入端接地,运算放大器u5的输出端通过电阻r15与运算放大器u6的反相输入端相连;电阻r19与电容c3组成第三并联网络,所述第三并联网络的两端分别连接运算放大器u6的反相输入端和运算放大器u6的输出端,运算放大器u6的正相输入端通过电阻r18接地,运算放大器u6的输出端与乘法器a4的y端口相连;

8.乘法器a1的x端口和y端口均与运算放大器u5的输出端相连,乘法器a1的输出端口与乘法器a2的y端口相连;乘法器a2的x端口与运算放大器u3的输出端相连;乘法器a4的x端口和y端口均与运算放大器u6的输出端相连,乘法器a4的输出端口与乘法器a3的x端口相连;乘法器a3的y端口与运算放大器u5的输出端相连;

9.运算放大器u7的反相输入端分别连接电阻r20的一端、电阻r21的一端、电阻r22的一端、电阻r23的一端和电阻r24的一端,电阻r20的另一端与乘法器a6的输出端相连,电阻r21的另一端与运算放大器u8的输出端相连,电阻r22的另一端通过电阻r35与运算放大器u11的反相输入端相连,电阻r22的另一端还与电阻r3的另一端连接,电阻r23的另一端与乘法器a7的输出端相连,电阻r24的另一端与正弦信号源v2的正极相连;电阻r25的两端分别与运算放大器u7的反相输入端和运算放大器u7的输出端相连,运算放大器u7的正相输入端接地,运算放大器u7的输出端通过电阻r26与运算放大器u8的反相输入端相连;

10.电阻r28与电容c4并联形成第四并联网络,所述第四并联网络的两端分别连接运算放大器u8的反相输入端和运算放大器u8的输出端,运算放大器u8的正相输入端通过电阻r29接地,运算放大器u8的输出端通过电阻r27与运算放大器u9的反相输入端相连,运算放大器u8的输出端通过电阻r33与运算放大器u10的反相输入端相连;

11.电阻r30的两端分别连接运算放大器u9的反相输入端和运算放大器u9的输出端,运算放大器u9的正相输入端接地,运算放大器u9的输出端与乘法器a6的x端口相连;电阻r36的两端分别连接运算放大器u11的反相输入端和运算放大器u11的输出端,运算放大器u11的正相输入端接地,运算放大器u11的输出端通过电阻r34与运算放大器u12的反相输入端相连;

12.电阻r38与电容c5并联形成第五并联网络,所述第五并联网络的两端连接运算放大器u12的反相输入端和运算放大器u12的输出端,运算放大器u12的正相输入端通过电阻r37接地,运算放大器u12的输出端均与乘法器a8的x端口和y端口相连;

13.乘法器a5的x端口和y端口均与运算放大器u11的输出端相连,乘法器a5的输出端口与乘法器a6的y端口相连;乘法器a8的输出端口与乘法器a7的x端口相连;乘法器a7的y端口与运算放大器u11的输出端相连;运算放大器u10的正相输入端通过电阻r32接地,运算放大器u10的输出端通过电阻r39与运算放大器u10的反相输入端相连。

14.进一步地,所述混沌同步电路的工作原理为:

15.输入正弦信号v1,经过第一求和电路后,得到第一输出信号;所述第一输出信号经过第一积分电路进行积分后,得到第二输出信号;所述第二输出信号经过第一反向电路进

行反向后,得到第三输出信号;所述第三输出信号经过第二积分电路进行积分后,得到第四输出信号;所述第四输出信号经过第二反向电路进行反向后,得到第五输出信号;所述第五输出信号经过第三积分电路进行积分后,得到第六输出信号;其中,所述第一求和电路包括电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6和运算放大器u1;所述第一积分电路包括电阻r7、电阻r10、电阻r11、电容c1和运算放大器u2;所述第一反向电路包括电阻r9、电阻r8和运算放大器u3;所述第二积分电路包括电阻r12、电阻r13、电阻r14、电容c2和运算放大器u4;所述第二反向电路包括电阻r16、电阻r17和运算放大器u5;所述第三积分电路包括电阻r15、电阻r19、电阻r18、电容c3和运算放大器u6;

16.所述第六输出信号经过乘法器a4进行倍乘后,得到第七输出信号;所述第七输出信号经过乘法器a3与所述第五输出信号进行相乘,得到第八输出信号;所述第五输出信号经过乘法器a1进行倍乘后,得到第九输出信号;所述第九输出信号经过乘法器a2与所述第三输出信号进行相乘,得到第十输出信号;

17.所述第二输出信号、所述第四输出信号、所述第八输出信号和所述第十输出信号经过所述第一求和电路与所述正弦信号v1进行反向相加;其中,所述正弦信号v1经过所述第一求和电路与乘法器a2、乘法器a3、运算放大器u2和运算放大器u4分别输出的信号进行反向相加,得到所述第一输出信号。

18.输入正弦信号v2,经过第二求和电路后,得到第十一输出信号;所述第十一输出信号经过第四积分电路进行积分后,得到第十二输出信号;所述第十二输出信号经过第三反向电路进行反向后,得到第十三输出信号;所述第四输出信号经过第四反向电路进行反向后,得到第十四输出信号;所述第十四输出信号经过第五积分电路进行积分后,得到所述第十五输出信号;

19.其中,所述第二求和电路包括电阻r20、电阻r21、电阻r22、电阻r23、电阻r24、电阻r25和运算放大器u7;所述第四积分电路包括电阻r26、电阻r28、电阻r29、电容c4和运算放大器u8;所述第三反向电路包括电阻r27、电阻r30和运算放大器u9;所述第四反向电路包括电阻r35、电阻r36和运算放大器u11;所述第五积分电路包括电阻r34、电阻r38、电阻r37、电容c5和运算放大器u12;

20.所述第十五输出信号经过乘法器a8进行倍乘后,得到第十六输出信号;所述第十六输出信号经过乘法器a7与所述第十四输出信号进行相乘,得到第十七输出信号;所述第十四输出信号经过乘法器a5进行倍乘后,得到第十八输出信号;所述第十八输出信号经过乘法器a6与所述第十三输出信号进行相乘,得到第十九输出信号;所述第四输出信号、所述第十二输出信号、所述第十七输出信号和所述第十九输出信号经过所述第二求和电路与所述正弦信号v2进行反向相加;

21.其中,所述正弦信号v2经过所述第二求和电路与乘法器a6、乘法器a7、运算放大器u8和运算放大器u4分别输出的信号进行反向相加,得到所述第十一输出信号;

22.所述第二输出信号和第十二输出信号经过差分放大电路进行放大后,得到第二十输出信号;其中,所述差分放大电路包括电阻r31、电阻r32、电阻r33、电阻r39和运算放大器u10。

23.进一步地,duffing-van der pol忆阻混沌振子包括第一磁控忆阻器和第二磁控忆阻器,其中,第一磁控忆阻器包括所述第三积分电路、所述乘法器a3和所述乘法器a4,第

二磁控忆阻器包括所述第五积分电路、所述乘法器a7和所述乘法器a8。

24.进一步地,duffing-van der pol忆阻混沌振子的数学模型如公式(1)所示:

[0025][0026]

其中,x表示电压,δ表示非线性阻尼系数,γ表示正弦信号的幅值,ω表示正弦信号的角频率,t表示时间;

[0027]

基于上述duffing-van der pol忆阻混沌振子设计的混沌同步电路存在两个非线性系统,二者之间存在驱动与响应的关系,将整个混沌同步电路分为驱动系统和响应系统两部分,驱动系统自变量的运动轨迹不受响应系统的影响,响应系统的行为受到驱动系统的控制,即使用驱动系统中的某个自变量作为驱动变量来驱动响应系统,从而使驱动系统和响应系统实现同步;

[0028]

驱动系统:将公式(1)表示为如公式(2)所示的微分方程:

[0029][0030]

其中,xd、yd、zd是驱动系统的三个状态变量,xd表示运算放大器u6的输出端电压,yd表示运算放大器u4的输出端电压,zd示运算放大器u2的输出端电压,磁控忆阻器的忆导值由决定,即q表示电荷量,表示磁通量,的值等于磁控忆阻器两端的电压对时间t的积分;

[0031]

响应部分:基于上述驱动系统,减少一个状态变量,并引入上述运算放大器u4的输出端电压yd用以驱动响应系统,表示为如公式(3)所示的微分方程:

[0032][0033]

其中,xr、zr是响应系统的两个状态变量,xr表示运算放大器u11的输出端电压,zr表示运算放大器u8的输出端电压,磁控忆阻器的忆导值由决定,即q表示电荷量,表示磁通量,的值等于磁控忆阻器两端的电压对时间t的积分。

[0034]

本发明提供的技术方案带来的有益效果是:通过对基于忆阻器的duffing-van der pol忆阻混沌振子电路进行同步设计,采用驱动-响应的同步方法,实现了一种具有实时同步特性的混沌同步系统。

附图说明

[0035]

下面将结合附图及实施例对本发明作进一步说明,附图中:

[0036]

图1是本发明实施例中一种基于duffing-van der pol忆阻混沌振子的混沌同步电路的结构示意图;

[0037]

图2是本发明实施例中z

d-zr相图。

具体实施方式

[0038]

为了对本发明的技术特征、目的和效果有更加清楚的理解,现对照附图详细说明本发明的具体实施方式。

[0039]

本发明的实施例提供了一种基于duffing-van der pol忆阻混沌振子的混沌同步电路。

[0040]

请参考图1,图1是本发明实施例中一种基于duffing-van der pol忆阻混沌振子的混沌同步电路的结构示意图,该混沌同步电路包括运算放大器u1、运算放大器u2、运算放大器u3、运算放大器u4、运算放大器u5、运算放大器u6、运算放大器u7、运算放大器u8、运算放大器u9、运算放大器u10、运算放大器u11、运算放大器u12、电容c1、电容c2、电容c3、电容c4、电容c5、乘法器a1、乘法器a2、乘法器a3、乘法器a4、乘法器a5、乘法器a6、乘法器a7、乘法器a8、外围电阻以及两个正弦信号源;

[0041]

其中,电阻r1的一端与运算放大器u1的反相输入端相连,电阻r1的另一端与乘法器a2的输出端相连;电阻r2的一端与运算放大器u1的反相输入端相连,电阻r2的另一端与运算放大器u2的输出端相连;电阻r3的一端与运算放大器u1的反相输入端相连,电阻r3的另一端与运算放大器u4的输出端相连;电阻r4的一端与运算放大器u1的反相输入端相连,电阻r4的另一端与乘法器a3的输出端相连;电阻r5的一端与运算放大器u1的反相输入端相连,电阻r5的另一端与正弦信号源v1的正极相连;电阻r6的一端与运算放大器u1的反相输入端相连,电阻r6的另一端与运算放大器u1的输出端相连;运算放大器u1的正相输入端接地,运算放大器u1的输出端通过电阻r7与运算放大器u2的反相输入端相连;

[0042]

电阻r10与电容c1并联形成第一并联网络,所述第一并联网络的一端与运算放大器u2的反相输入端相连,所述第一并联网络的另一端与运算放大器u2的输出端相连;运算放大器u2的正相输入端通过电阻r11接地,运算放大器u2的输出端通过电阻r9与运算放大器u3的反相输入端相连,运算放大器u2的输出端通过电阻r31与运算放大器u10的正相输入端相连;电阻r8的一端与运算放大器u3的反相输入端相连,电阻r8的另一端与运算放大器u3的输出端相连;运算放大器u3的正相输入端接地,运算放大器u3的输出端通过电阻r12与运算放大器u4的反相输入端相连;

[0043]

电阻r13与电容c2并联形成第二并联网络,所述第二并联网络的一端与运算放大器u4的反相输入端相连,所述第二并联网络的另一端与运算放大器u4的输出端相连;运算放大器u4的正相输入端通过电阻r14接地,运算放大器u4的输出端通过电阻r16与运算放大器u5的反相输入端相连;

[0044]

电阻r17的一端与运算放大器u5的反相输入端相连,电阻r17的另一端与运算放大器u5的输出端相连;运算放大器u5的正相输入端接地,运算放大器u5的输出端通过电阻r15与运算放大器u6的反相输入端相连;电阻r19与电容c3组成第三并联网络,所述第三并联网络的一端与运算放大器u6的反相输入端相连,所述第三并联网络的另一端与运算放大器u6的输出端相连;运算放大器u6的正相输入端通过电阻r18接地,运算放大器u6的输出端与乘法器a4的y端口相连;

[0045]

乘法器a1的y端口与运算放大器u5的输出端相连,乘法器a1的x端口与运算放大器u5的输出端相连,乘法器a1的输出端口与乘法器a2的y端口相连;乘法器a2的x端口与运算放大器u3的输出端相连;乘法器a4的x端口与运算放大器u6的输出端相连,乘法器a4的输出

端口与乘法器a3的x端口相连;乘法器a3的y端口与运算放大器u5的输出端相连;

[0046]

电阻r20的一端与运算放大器u7的反相输入端相连,电阻r20的另一端与乘法器a6的输出端相连;电阻r21的一端与运算放大器u7的反相输入端相连,电阻r21的另一端与运算放大器u8的输出端相连;电阻r22的一端与运算放大器u7的反相输入端相连,电阻r22的另一端通过电阻r35与运算放大器u11的反相输入端相连;电阻r23的一端与运算放大器u7的反相输入端相连,电阻r23的另一端与乘法器a7的输出端相连;电阻r24的一端与运算放大器u7的反相输入端相连,电阻r24的另一端与正弦信号源v2的正极相连;电阻r25的一端与运算放大器u7的反相输入端相连,电阻r25的另一端与运算放大器u7的输出端相连;运算放大器u7的正相输入端接地,运算放大器u7的输出端通过电阻r26与运算放大器u8的反相输入端相连;

[0047]

电阻r28与电容c4并联形成第四并联网络,所述第四并联网络的一端与运算放大器u8的反相输入端相连,所述第四并联网络的另一端与运算放大器u8的输出端相连;运算放大器u8的正相输入端通过电阻r29接地,运算放大器u8的输出端通过电阻r27与运算放大器u9的反相输入端相连,运算放大器u8的输出端通过电阻r33与运算放大器u10的反相输入端相连;

[0048]

电阻r30的一端与运算放大器u9的反相输入端相连,电阻r30的另一端与运算放大器u9的输出端相连;运算放大器u9的正相输入端接地,运算放大器u9的输出端与乘法器a6的x端口相连;电阻r36的一端与运算放大器u11的反相输入端相连,电阻r36的另一端与运算放大器u11的输出端相连;运算放大器u11的正相输入端接地,运算放大器u11的输出端通过电阻r34与运算放大器u12的反相输入端相连;

[0049]

电阻r38与电容c5并联形成第五并联网络,所述第五并联网络的一端与运算放大器u12的反相输入端相连,所述第五并联网络的另一端与运算放大器u12的输出端相连;运算放大器u12的正相输入端通过电阻r37接地,运算放大器u12的输出端与乘法器a8的y端口相连;

[0050]

乘法器a5的y端口与运算放大器u11的输出端相连,乘法器a5的x端口与运算放大器u11的输出端相连,乘法器a5的输出端口与乘法器a6的y端口相连;乘法器a8的x端口与运算放大器u12的输出端相连,乘法器a8的输出端口与乘法器a7的x端口相连;乘法器a7的y端口与运算放大器u11的输出端相连;运算放大器u10的正相输入端通过电阻r32接地,运算放大器u10的输出端通过电阻r39与运算放大器u10的反相输入端相连。

[0051]

所述混沌同步电路的工作原理为:

[0052]

输入正弦信号v1,经过第一求和电路后,得到第一输出信号;所述第一输出信号经过第一积分电路进行积分后,得到第二输出信号;所述第二输出信号经过第一反向电路进行反向后,得到第三输出信号;所述第三输出信号经过第二积分电路进行积分后,得到第四输出信号;所述第四输出信号经过第二反向电路进行反向后,得到第五输出信号;所述第五输出信号经过第三积分电路进行积分后,得到第六输出信号;其中,所述第一求和电路包括电阻r1、电阻r2、电阻r3、电阻r4、电阻r5、电阻r6和运算放大器u1;所述第一积分电路包括电阻r7、电阻r10、电阻r11、电容c1和运算放大器u2;所述第一反向电路包括电阻r9、电阻r8和运算放大器u3;所述第二积分电路包括电阻r12、电阻r13、电阻r14、电容c2和运算放大器u4;所述第二反向电路包括电阻r16、电阻r17和运算放大器u5;所述第三积分电路包括电阻

r15、电阻r19、电阻r18、电容c3和运算放大器u6;

[0053]

所述第六输出信号经过乘法器a4进行倍乘后,得到第七输出信号;所述第七输出信号经过乘法器a3与所述第五输出信号进行相乘,得到第八输出信号;所述第五输出信号经过乘法器a1进行倍乘后,得到第九输出信号;所述第九输出信号经过乘法器a2与所述第三输出信号进行相乘,得到第十输出信号;

[0054]

所述第二输出信号、所述第四输出信号、所述第八输出信号和所述第十输出信号经过所述第一求和电路与所述正弦信号v1进行反向相加;其中,所述正弦信号v1经过所述第一求和电路与乘法器a2、乘法器a3、运算放大器u2和运算放大器u4分别输出的信号进行反向相加,得到所述第一输出信号。

[0055]

输入正弦信号v2,经过第二求和电路后,得到第十一输出信号;所述第十一输出信号经过第四积分电路进行积分后,得到第十二输出信号;所述第十二输出信号经过第三反向电路进行反向后,得到第十三输出信号;所述第四输出信号经过第四反向电路进行反向后,得到第十四输出信号;所述第十四输出信号经过第五积分电路进行积分后,得到所述第十五输出信号;

[0056]

其中,所述第二求和电路包括电阻r20、电阻r21、电阻r22、电阻r23、电阻r24、电阻r25和运算放大器u7;所述第四积分电路包括电阻r26、电阻r28、电阻r29、电容c4和运算放大器u8;所述第三反向电路包括电阻r27、电阻r30和运算放大器u9;所述第四反向电路包括电阻r35、电阻r36和运算放大器u11;所述第五积分电路包括电阻r34、电阻r38、电阻r37、电容c5和运算放大器u12;

[0057]

所述第十五输出信号经过乘法器a8进行倍乘后,得到第十六输出信号;所述第十六输出信号经过乘法器a7与所述第十四输出信号进行相乘,得到第十七输出信号;所述第十四输出信号经过乘法器a5进行倍乘后,得到第十八输出信号;所述第十八输出信号经过乘法器a6与所述第十三输出信号进行相乘,得到第十九输出信号;所述第四输出信号、所述第十二输出信号、所述第十七输出信号和所述第十九输出信号经过所述第二求和电路与所述正弦信号v2进行反向相加;

[0058]

其中,所述正弦信号v2经过所述第二求和电路与乘法器a6、乘法器a7、运算放大器u8和运算放大器u4分别输出的信号进行反向相加,得到所述第十一输出信号;

[0059]

所述第二输出信号和第十二输出信号经过差分放大电路进行放大后,得到第二十输出信号;其中,所述差分放大电路包括电阻r31、电阻r32、电阻r33、电阻r39和运算放大器u10。

[0060]

所述第三积分电路、所述乘法器a3和所述乘法器a4组成第一个duffing-van der pol忆阻混沌振子的磁控忆阻器,所述第五积分电路、所述乘法器a7和所述乘法器a8组成第二个duffing-van der pol忆阻混沌振子的磁控忆阻器。

[0061]

duffing-van der pol忆阻混沌振子,其数学模型可表示为如公式(1):

[0062][0063]

其中,x表示电压,δ表示非线性阻尼系数,γ表示正弦信号的幅值,ω表示正弦信号的角频率,t表示时间。

[0064]

基于上述duffing-van der pol忆阻混沌振子,本专利设计的混沌同步电路存在两个非线性系统,二者之间存在驱动与响应的关系,将整个同步电路分为驱动系统和响应

系统两部分,驱动系统自变量的运动轨迹不受响应系统的影响,响应系统的行为受到驱动系统的控制,即使用驱动系统中的某个自变量作为驱动变量来驱动响应系统,从而使驱动系统和响应系统实现同步。

[0065]

驱动系统:将公式(1)表示为如下微分方程如公式(2):

[0066][0067]

其中,xd、yd、zd是驱动系统的三个状态变量,xd表示运算放大器u6的输出端电压,yd表示运算放大器u4的输出端电压,zd示运算放大器u2的输出端电压,磁控忆阻器的忆导值由决定,即q表示电荷量,表示磁通量,的值等于磁控忆阻器两端的电压对时间t的积分;

[0068]

响应部分:基于上述驱动系统,减少一个状态变量,并引入上述运算放大器u4的输出端电压yd用以驱动响应系统,表示为如公式(3)所示的微分方程:

[0069][0070]

其中,xr、zr是响应系统的两个状态变量,xr表示运算放大器u11的输出端电压,zr示运算放大器u8的输出端电压,磁控忆阻器的忆导值由决定,即q表示电荷量,表示磁通量,的值等于磁控忆阻器两端的电压对时间t的积分。

[0071]

请参考图2,图2是本发明实施例中z

d-zr相图的示意图,本发明中运算放大器u1、运算放大器u2、运算放大器u3、运算放大器u4、运算放大器u5、运算放大器u6、运算放大器u7、运算放大器u8、运算放大器u9、运算放大器u10、运算放大器u11和运算放大器u12均选用运算放大器tl082,乘法器a1、乘法器a2、乘法器a3、乘法器a4、乘法器a5、乘法器a6、乘法器a7和乘法器a8均选用四象限乘法器ad633,电容c1=100uf、电容c2=100uf、电容c3=100uf、电容c4=100uf、电容c5=100uf,电阻r1=20kω、电阻r2=20kω、电阻r3=10kω、电阻r4=10kω、电阻r5=10kω、电阻r6=10kω、电阻r7=10kω、电阻r8=10kω、电阻r9=10kω、电阻r10=220kω、电阻r11=9.5kω、电阻r12=10kω、电阻r13=220kω、电阻r14=9.5kω、电阻r15=10kω、电阻r16=10kω,r17=10kω,r18=9.5kω,r19=220kω,电阻r20=20kω、电阻r21=20kω、电阻r22=10kω、电阻r23=10kω、电阻r24=10kω、电阻r25=10kω、电阻r26=10kω、电阻r27=10kω、电阻r28=220kω、电阻r29=9.5kω、电阻r30=10kω、电阻r31=10kω、电阻r32=10kω、电阻r33=10kω、电阻r34=10kω、电阻r35=10kω,r36=10kω,r37=9.5kω,r38=220kω,r39=10kω,各参数取值为:γ=0.5v,ω=1rad/s,a=1,由图2可以看出,本发明一种基于duffing-van der pol忆阻混沌振子的混沌同步电路具有较好的同步特性,能够实现驱动系统和响应系统的同步。

[0072]

本发明的有益效果是:通过对基于忆阻器的duffing-van der pol忆阻混沌振子

电路进行同步设计,采用驱动-响应的同步方法,实现了一种具有实时同步特性的混沌同步系统。

[0073]

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。