一种应用于p_flash型fpga的配置控制电路

技术领域

1.本发明涉及可编程逻辑器件技术领域,特别涉及一种应用于p_flash型fpga的配置控制电路。

背景技术:

2.fpga(field programmable gate array,现场可编程门阵列),根据内部可编程配置单元来区分;当前主流fpga电路主要有sram型、反熔丝型和flash型fpga三种类型。

3.flash型fpga内部可配置单元为flash开关,基于flash架构的fpga可实现多次擦除、编程和校验等操作,且电路掉电后配置信息具有非易失性,系统上电时不需要外部配置存储器进行配置数据加载,具有上电启动速度快、保密安全性高等特点,广泛应用于航天军工、工业控制等众多领域。

4.根据p型flash单元操作机理对fpga中flash存储单元进行配置操作,需要设计相对应的配置控制电路。

技术实现要素:

5.本发明的目的在于提供一种应用于p_flash型fpga的配置控制电路,以实现对fpga中flash存储配置单元进行配置操作。

6.为解决上述技术问题,本发明提供了一种应用于p_flash型fpga的配置控制电路,用于对由p_flash配置单元组成的p_flash存储阵列进行擦除、编程、数据读取校验和过擦除,其特征在于,所述配置控制电路包括字线电路、位线电路、数据读取电路和数据对比校验电路;其中,所述字线电路中每根字线栅端水平连接所述p_flash存储阵列中对应的每一行p_flash配置单元的栅端;所述位线电路中每根位线漏端连接对应的每一列p_flash配置单元的漏端,每根位线源端连接对应的每一列flash配置单元的源端;所述数据读取电路包括指定个数的数据读取通道,每一个数据读取通道对应相应位的位线通道,能够将配置数据从p_flash配置单元的漏端读取出来;所述数据对比校验电路将编程数据和从p_flash配置单元上读取的配置数据进行异或对比校验。

7.可选的,所述字线电路包括89个水平字线通道,每个字线通道中有32根字线,每一根字线对应的字线电路是相同的结构;所述字线电路包括nmos管n0~n9、pmos管p0~p10;nmos管n0的漏端、nmos管n2的漏端、nmos管n8的漏端均连接字线栅端wl;nmos管n5的源端、nmos管n7的源端、nmos管n9的源端均连接lv1信号;nmos管n0的源端连接nmos管n1的漏端;nmos管n1的源端连接地gnd;nmos管n2的源端连接nmos管n3的漏端;nmos管n3的源端连接nmos管n4的漏端;nmos管n4的源端连接nmos管n5的漏端;nmos管n8的源端连接nmos管n6的漏端、nmos管n9漏端;nmos管n6的源

端连接nmos管n7的漏端;pmos管p0、pmos管p2、pmos管p6、pmos管p9的源端均连接vs_wl信号;pmos管p1的漏端、pmos管p5的漏端都连接字线栅端wl;pmos管p0的漏端连接pmos管p1的源端;pmos管p2的漏端连接p3管的源端;pmos管p3的漏端连接pmos管p4的源端;pmos管p4的漏端连接pmos管p5的源端;pmos管p6的漏端连接pmos管p7的源端;pmos管p7的漏端连接pmos管p8的源端;pmos管p9的漏端连接pmos管p10的源端;pmos管p8的漏端、pmos管p10的漏端连接pmos管p5的源端;nmos管n0的栅端连接a1信号,nmos管n1的栅端连接a2信号,nmos管n2的栅端连接a2n信号,nmos管n3的栅端连接a1信号,nmos管n4的栅端连接oen信号,nmos管n5的栅端连接a3信号,nmos管n6的栅端连接a3n信号,nmos管n7的栅端连接a2n信号,nmos管n8的栅端连接a1n信号,nmos管n9的栅端连接oep信号;pmos管p0的栅端连接a2n信号,pmos管p1的栅端连接a1信号,pmos管p2的删端连接oep信号,pmos管p3的栅端连接a3n信号,pmos管p4的栅端连接a1n信号,pmos管p5的栅端连接a2信号,pmos管p6的栅端连接a1n信号,pmos管p7的栅端连接a3n信号,pmos管p8的栅端连接oen信号,pmos管p9的栅端连接a1n信号,pmos管p10的栅端连接a3信号。

8.可选的,所述位线电路包括10个竖直的位线通道,每个位线通道中有83根位线,每一根位线对应的位线电路是相同的结构;所述位线电路包括nmos管n10~n19、pmos管p11~p14;nmos管n10的源端、nmos管n13的源端均连接地gnd;nmos管n10的漏端、nmos管n12的漏端连接nmos管n11的源端;nmos管n12的源端连接lv2信号;nmos管n11的漏端、nmos管n13的漏端连接位线漏端bl;pmos管p11的源端连接vs_bl信号,漏端连接位线漏端bl;nmos管n10的栅端连接a4信号;nmos管n11的栅端连接prg信号;nmos管n12的栅端连接a4n信号;nmos管n13的栅端连接a5信号;pmos管p11的栅端连接era信号;nmos管n14的栅端连接a7n信号;nmos管n15的栅端连接a6信号;nmos管n16的栅端连接prg信号;nmos管n17的栅端连接a4信号;nmos管n18的栅端连接a4n信号;nmos管n19的栅端连接a8信号;pmos管p12的栅端连接a6信号;pmos管p13的栅端连接a7信号;pmos管p14的栅端连接era信号。

9.可选的,所述数据读取电路包括83个数据读取通道,每一个数据读取电路的结构是相同的;所述数据读取电路包括nmos管n20~n25、pmos管p15~p17和三个反相器电路;nmos管n24的源端连接地gnd,漏端连接nmos管n23的源端;nmos管n23的漏端连接nmos管n22的源端;nmos管n22的漏端连接nmos管n21的源端;nmos管n21的漏端连接nmos管n20的源端;nmos管n20的漏端连接pmos管p15的漏端;pmos管p15的源端、pmos管p16的源端和pmos管p17的源端均连接电源vcca,pmos管p15的栅端和pmos管p16的栅端相连并连接到nmos管n20的漏端;pmos管p16的漏端和pmos管p17的漏端均连接nmos管n25的漏端,并连接第一个反相器输入端;nmos管n24的栅端和nmos管n22的栅端均连接vs_bl信号;nmos管n23的栅端连接read_en信号;nmos管n21的栅端连接电源vcca;nmos管n20的栅端和nmos管n25的栅端均连接read_ctrl信号;nmos管n25的源端连接位线源端sl;pmos管p17的栅端连接program_en信号。

10.可选的,所述数据对比校验电路包括nmos管n26和n27、pmos管p18和三个传输门电路;nmos管n27的源端接qn信号,漏端连接pmos管p18的漏端和nmos管n26的栅端;pmos管p18的源端连接q信号;nmos管n26的源端连接地gnd,漏端连接verify_d信号。

11.可选的,所述flash配置单元的栅端连接所述字线栅端wl;漏端连接所述位线漏端bl,源端连接所述位线源端sl。

12.可选的,在擦除操作阶段,所述字线电路通过字线栅端向p_flash配置单元的栅端施加-9.5v电压;所述位线电路通过位线漏端向p_flash配置单元的漏端施加7.8v电压,通过位线源端向p_flash配置单元的源端提供7.8v电压。

13.可选的,在编程操作阶段,在配置控制电路的控制下对选中的p_flash配置单元进行编程操作,所述字线电路通过字线栅端向选中的p_flash配置单元的栅端施加8.8v电压,通过字线栅端施加-2.5v电压到对未选中的p_flash配置单元的栅端上;所述位线电路对选中p_flash配置单元的漏端施加-7v电压,对选中的p_flash配置单元的源端施加-0.9v电压;对未选中的p_flash配置单元的漏端和源端均施加0v电压。

14.可选的,在数据读取校验阶段,所述字线电路通过字线栅端向选中的p_flash配置单元的栅端施加0v电压,向其他未选中的p_flash配置单元的栅端施加8.8v电压;位线通道逐个被选中,各个p_flash配置单元的源端通过所连接的位线源端所属的位线通道连接到相对应的数据读取电路,所述位线电路向选中的p_flash配置单元的漏端施加0v电压,源端施加2.5v电压;所述数据读取电路对p_flash配置单元的源端信号电流进行采集处理,然后经过所述数据对比校验电路进行校验。

15.在本发明提供的应用于p_flash型fpga的配置控制电路中,对p_flash配置单元进行擦除、编程、数据读取校验和过擦除,所述配置控制电路包括字线电路、位线电路、数据读取电路和数据对比校验电路;字线电路中每根字线栅端水平连接所述p_flash存储阵列中对应的每一行p_flash配置单元的栅端;位线电路中每根位线漏端连接对应的每一列p_flash配置单元的漏端,每根位线源端连接对应的每一列flash配置单元的源端;数据读取电路包括指定个数的数据读取通道,每一个数据读取通道对应相应位的位线通道,能够将配置数据从p_flash配置单元的漏端读取出来;数据对比校验电路将编程数据和从p_flash配置单元上读取的配置数据进行异或对比校验。本发明的配置控制电路可以实现p_flash存储阵列单元进行擦除、编程、校验等功能,在相应的各配置指令集和操作电压下控制下,可以实现对p_flash型fpga各配置阶段操作。

附图说明

16.图1是由p_flash配置单元组成的p_flash存储阵列结构示意图;图2是本发明提供的配置控制电路中字线电路的结构示意图;图3是本发明提供的配置控制电路中位线电路的结构示意图;图4是本发明提供的配置控制电路中数据读取电路的结构示意图;图5是本发明提供的配置控制电路中数据对比校验电路的结构示意图。

具体实施方式

17.以下结合附图和具体实施例对本发明提出的一种应用于p_flash型fpga的配置控制电路作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

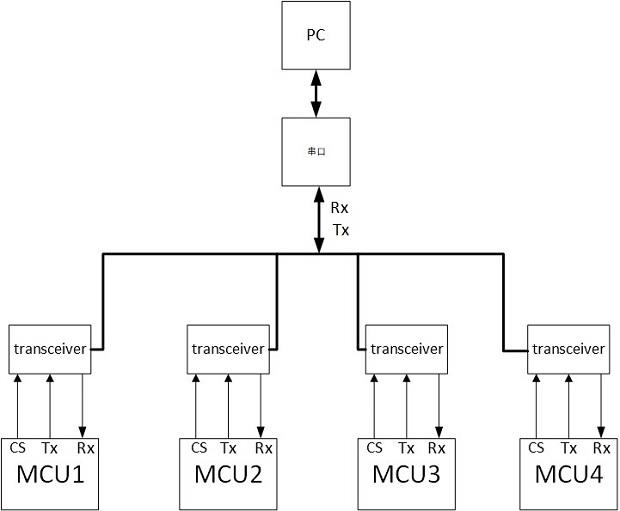

18.本发明提供了一种应用于p_flash型fpga的配置控制电路,如图1所示是由p_flash配置单元组成的p_flash存储阵列。水平信号为字线,竖直信号为bl和sl。所述配置控制电路包括字线电路、位线电路、数据读取电路和数据对比校验电路。字线电路的字线栅端wl输出连接到p_flash配置单元的栅端,位线电路的位线漏端bl输出连接到p_flash配置单元的漏端,位线电路的位线源端sl输出连接到p_flash配置单元的源端,通过数据读取电路中nmos管n25电流信号输入。

19.所述字线电路包括89个水平字线通道,每个字线通道中有32根字线,每根字线信号栅端信号wl水平连接到所述flash存储阵列的中对应的每一行的p_flash配置单元的栅端,每一根字线对应的字线电路是相同的结构。

20.如图2所示,所述字线电路包括nmos管n0~n9、pmos管p0~p10;nmos管n0的漏端、nmos管n2的漏端、nmos管n8的漏端均连接字线栅端wl;nmos管n5的源端、nmos管n7的源端、nmos管n9的源端均连接lv1信号;nmos管n0的源端连接nmos管n1的漏端;nmos管n1的源端连接地gnd;nmos管n2的源端连接nmos管n3的漏端;nmos管n3的源端连接nmos管n4的漏端;nmos管n4的源端连接nmos管n5的漏端;nmos管n8的源端连接nmos管n6的漏端、nmos管n9漏端;nmos管n6的源端连接nmos管n7的漏端;pmos管p0、pmos管p2、pmos管p6、pmos管p9的源端均连接vs_wl信号;pmos管p1的漏端、pmos管p5的漏端都连接字线栅端wl;pmos管p0的漏端连接pmos管p1的源端;pmos管p2的漏端连接p3管的源端;pmos管p3的漏端连接pmos管p4的源端;pmos管p4的漏端连接pmos管p5的源端;pmos管p6的漏端连接pmos管p7的源端;pmos管p7的漏端连接pmos管p8的源端;pmos管p9的漏端连接pmos管p10的源端;pmos管p8的漏端、pmos管p10的漏端连接pmos管p5的源端;nmos管n0的栅端连接a1信号,nmos管n1的栅端连接a2信号,nmos管n2的栅端连接a2n信号,nmos管n3的栅端连接a1信号,nmos管n4的栅端连接oen信号,nmos管n5的栅端连接a3信号,nmos管n6的栅端连接a3n信号,nmos管n7的栅端连接a2n信号,nmos管n8的栅端连接a1n信号,nmos管n9的栅端连接oep信号;pmos管p0的栅端连接a2n信号,pmos管p1的栅端连接a1信号,pmos管p2的删端连接oep信号,pmos管p3的栅端连接a3n信号,pmos管p4的栅端连接a1n信号,pmos管p5的栅端连接a2信号,pmos管p6的栅端连接a1n信号,pmos管p7的栅端连接a3n信号,pmos管p8的栅端连接oen信号,pmos管p9的栅端连接a1n信号,pmos管p10的栅端连接a3信号。

21.所述位线电路包括10个竖直位线通道,每个位线通道中有83根位线,每根位线漏端信号bl连接到对应的每一列p_flash配置单元的漏端,每根位线源端信号sl连接到相应的每一列p_flash配置单元的源端,每一根位线对应的位线电路是相同的结构。

22.如图3所示,所述位线电路包括nmos管n10~n19、pmos管p11~p14;nmos管n10的源端、nmos管n13的源端均连接地gnd;nmos管n10的漏端、nmos管n12的漏端连接nmos管n11的

源端;nmos管n12的源端连接lv2信号;nmos管n11的漏端、nmos管n13的漏端连接位线漏端bl;pmos管p11的源端连接vs_bl信号,漏端连接位线漏端bl;nmos管n10的栅端连接a4信号;nmos管n11的栅端连接prg信号;nmos管n12的栅端连接a4n信号;nmos管n13的栅端连接a5信号;pmos管p11的栅端连接era信号;nmos管n14的栅端连接a7n信号;nmos管n15的栅端连接a6信号;nmos管n16的栅端连接prg信号;nmos管n17的栅端连接a4信号;nmos管n18的栅端连接a4n信号;nmos管n19的栅端连接a8信号;pmos管p12的栅端连接a6信号;pmos管p13的栅端连接a7信号;pmos管p14的栅端连接era信号。

23.所述数据读取电路包括特定个数的数据读取通道,具体个数为p_flash型fpga中83位bits码流位数,每一个数据读取通道对应相应的几位位线通道,数据读取电路可以将配置数据从p_flash配置单元的漏端读取出来。每一个数据读取电路的结构是相同的。

24.如图4所示,所述数据读取电路包括nmos管n20~n25、pmos管p15~p17和三个反相器电路;nmos管n24的源端连接地gnd,漏端连接nmos管n23的源端;nmos管n23的漏端连接nmos管n22的源端;nmos管n22的漏端连接nmos管n21的源端;nmos管n21的漏端连接nmos管n20的源端;nmos管n20的漏端连接pmos管p15的漏端;pmos管p15的源端、pmos管p16的源端和pmos管p17的源端均连接电源vcca,pmos管p15的栅端和pmos管p16的栅端相连并连接到nmos管n20的漏端;pmos管p16的漏端和pmos管p17的漏端均连接nmos管n25的漏端,并连接第一个反相器输入端;nmos管n24的栅端和nmos管n22的栅端均连接vs_bl信号;nmos管n23的栅端连接read_en信号;nmos管n21的栅端连接电源vcca;nmos管n20的栅端和nmos管n25的栅端均连接read_ctrl信号;nmos管n25的源端连接位线源端sl;pmos管p17的栅端连接program_en信号。

25.如图5所示,所述数据对比校验电路包括nmos管n26和n27、pmos管p18和三个传输门电路;nmos管n27的源端接qn信号,漏端连接pmos管p18的漏端和nmos管n26的栅端;pmos管p18的源端连接q信号;nmos管n26的源端连接地gnd,漏端连接verify_d信号。

26.联合图2~图5,所述flash配置单元的栅端连接所述字线栅端wl;漏端连接所述位线漏端bl,源端连接所述位线源端sl。

27.本发明提供的配置控制电路可以实现p_flash存储阵列单元进行擦除、编程、读取校验和过擦除等功能,在相应的各配置指令集和操作电压下控制下,可以实现对p_flash型fpga各配置阶段操作,具体操作阶段如下文所述。

28.根据图2~图5配置控制电路中各信号状态,对不同操作阶段进行详细表述。首先对以下电路中各信号状态和对应的mos管状态进行说明,比如a1=0,表示a1信号为低电平,a3=1,表示a3信号为高电平,以下各表述过程均为使用此种表述方式,对于cmos集成电路而言,pmos管当其栅端信号为“0”时,表示pmos管开启,栅端信号为“1”时,表示pmos管关断。同样地对于nmos管,当其栅端信号为“0”时,表示nmos管关断,栅端信号为“1”时,表示nmos管开启。

29.一、在擦除操作过程:p_flash型fpga采用全片选中擦除方式,即通过配置控制电路对fpga中所有的p_flash配置单元阵列进行全片擦除操作。字线通道的全部字线信号栅端wl向p_flash存储单元栅端施加-9.5v电压,位线电路的全部的位线通道中全部的位线漏端bl向p_flash存储单

元漏端施加7.8v电压,全部的位线源端sl向p_flash存储单元源端施加7.8v电压。

30.字线电路中,lv1=-9.5v,a1n=oep=1,nmos管n8、n9导通,该2个nmos管形成的通路导通,其他的通路均关闭,字线输出为lv1=-9.5v;在位线电路中,era=0,pmos管p11、p14导通,位线bl和位线sl端口输出为vs_bl=7.8v电压。

31.二、编程操作过程:在配置电路控制下对选中到的p_flash配置单元进行编程操作。通过相对应指令操作,首先选中某个字线通道,再选中该字线通道中的某根字线,所述字线电路通过栅端信号wl向选中的p_flash配置单元的栅端施加8.8v电压,对未选中的字线信号栅端施加-2.5v电压;对于位线信号,相类似地,首先选中某个具体的位线通道,再向选中的位线通道中通过灌入编程bits数据流,所述位线电路对选中p_flash配置单元的位线漏端信号施加-7v电压,位线源端施加-0.9v电压,对未选中的p_flash配置单元位线的漏端和位线源端施加0v电压。

32.在对p_flash配置单元编程操作阶段,具体分为选中和未选中两种状态,各信号状态如下:1、对于选中的p_flash配置单元:(1)在字线电路中,信号状态为vs_wl=8.8v,lv1=-2.5v,a1=a2=oep=a3n=0,pmos管p2、p3、p4、p5导通,该4个pmos管形成的通路导通,字线栅端信号输出为vs_wl=8.8v;(2)在位线电路中,信号状态为lv2=-7v,lv3=-0.9v,prg=a4n=1,nmos管n11、n12、n16、n18开启,nmos管n11和n12形成的通路导通,位线bl输出lv2=-7v电压;nmos管n16和n18形成的通路导通,位线sl信号为lv3=-0.9v电压。

33.2、对于未选中的p_flash配置单元,包括字线未选中和位线未选中,具体分为以下三种情形:(1)对于字线通道被选中,但字线通道中未被选中的字线,vs_wl=8.8v,lv1=-2.5v,a1n=oep=1,nmos管n8、n8导通,该2个nmos管形成的通路导通,别的通路均关闭,字线输出为lv1=-2.5v。

34.(2)对于字线通道未选中字线通道中未选中的字线,lv1=-2.5v,a2n=a3n=1,nmos管n6、n7导通,该2个nmos管形成的通路导通,别的通路均关闭,字线输出为lv1=-2.5v。

35.(3)p_flash配置单元字线被选中,但位线bl和位线sl端未被选中。此时,a4=prg=1,nmos管n10、n11、n16和n17导通,该4个nmos管形成的通道导通,位线bl和sl端输出都为gnd=0v电压。

36.三、校验操作过程:在配置电路控制下对flash型fpga中p_flash配置单元进行校验操作。在校验操作阶段,电路中字线通道和字线被逐一遍历到。位线通道依次被选中,每个p_flash配置单元的源端通过所连接的源端信号端所属的位线通道连接到相对应的数据读取电路,数据读取电路对p_flash配置单元漏电信号进行采集处理,然后经过数据对比校验电路进行校验。

37.在校验模式下,字线电路通过栅端信号向选中到的p_flash配置单元的栅端施加0v电压,位线bl施加0v电压,sl端施加2.5v电压。字线电路向其他未被选中到的p_flash配置单元的栅端施加8.8v电压,位线bl和sl端施加0v电压。

38.1、对于选中的p_flash配置单元:

在字线电路中,此时lv1=0v,a1=a2n=a3=oen=1,nmos管n2~n5导通,该4个nmos管形成的通路导通,别的通路均关闭,字线输出为lv1=0v。

39.在位线电路中,此时a5=1,a6=a7=0,nmos管n13开启,pmos管p12和p13开启。位线bl输出gnd=0v电压,即此时p_flash配置单元的漏端信号为0v,位线sl输出vcca=2.5v电压。

40.在读取电路中,通过电流源电路,将sl读取到的电流信息读入,输出结果信号read_out。数据对比校验电路将输入信号read_out同此时输入的编程码流数据q进行异或对比校验,对比校验后,通过nmos管n26的开启与关闭,输出对比校验结果verify_d给flash相关控制电路,以此来判断相关的p_flash配置单元是否擦除和编程正确。

41.2、对于未选中的p_flash配置单元:在字线电路中,此时vs_wl=8.8v,a1n=oen=a3n=0,pmos管p6~p8导通,该3个pmos管形成的通路导通,别的通路均关闭,字线输出为vs_wl=8.8v。

42.在位线电路中,a5=a6=a7n=1,nmos管n13~n15开启,位线bl和sl输出为gnd=0v。

43.综上所述,本发明所提出的一种应用于p_flash型fpga的配置控制电路,经过设计、仿真验证后的一种可靠、灵活的计方法,为后期设计更大规模的p_flash型fpga电路提供保障依据。

44.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。