1.本公开涉及一种成像装置、电子设备和制造方法,并且涉及例如适合应用于包括多个芯片的成像装置的成像装置、电子设备和制造方法。

背景技术:

2.成像装置具有高清、4k

×

2k超高清和进一步的超慢动作功能形式的高画质,从而导致像素数的增多、高帧速率和高灰度。

3.由于传输速率是像素数

×

帧速率

×

灰度,例如在4k

×

2k=8m像素、帧速率240f/s、14位灰度的情况下,获得8m

×

240f/s

×

14位=26gbps。在成像元件的后段进行信号处理后,由于颜色坐标中的rgb输出,需要26g

×

3=78gbps的更高速传输。

4.当用少量连接端子进行高速传输时,每个连接端子的信号速率增加,实现高速传输路径的阻抗匹配的难易度增加,时钟频率增加,损耗也增加,导致功耗增加。

5.为了避免这种情况,优选的是增加连接端子的数量并分割传输以降低信号速率。然而,当连接端子的数量增加时,由于将成像元件与后段的信号处理电路、存储电路等连接所需的端子的配置,各电路的封装变大。

6.此外,后段的信号处理电路和存储电路所需的电气配线的基板也要求在层叠配线中更微细的配线密度,配线路径长度变长,因此功耗增加。

7.当各电路的封装变大时,将要安装的基板本身也变大,并且最终安装有成像元件的成像装置的构成本身变大。

8.因此,作为用于减小成像装置的构成的尺寸的技术,已经提出了一种如下的技术,其中成像元件通过在晶圆状态下执行电路接合的晶圆上晶圆(wow,wafer on wafer)而与诸如信号处理电路和存储电路等电路层叠(参见专利文献1)。

9.通过使用wow的层叠技术,可以通过许多微细配线连接半导体,从而使每个半导体的传输速度变低并且可以抑制功耗。

10.引用文献列表

11.专利文献

12.专利文献1:日本专利申请特开no.2014-099582

技术实现要素:

13.发明要解决的问题

14.然而,在wow的情况下,只要将要层叠的晶圆的芯片具有相同的尺寸就没有问题,但是当制成晶圆的各个芯片的尺寸不同时,必须将尺寸调整为最大的芯片尺寸,存在着各电路的制造效率劣化和成本增加的可能性。

15.此外,对于各晶圆的良率而言,将要层叠的各晶圆的芯片缺陷也会导致层叠的其他晶圆的芯片被视为缺陷。由于整个层叠的晶圆的良率是各晶圆的良率的乘积(乘法),因此存在着良率劣化和成本增加的可能性。

16.此外,还提出了通过形成小凸块来连接具有不同芯片尺寸的芯片的技术。在这种情况下,由于被选为良品的不同尺寸的芯片经由凸块连接,因此对各晶圆的制造效率和各芯片的良率的影响很小。

17.然而,由于难以形成小凸块且连接间距受到限制,因此存在着连接端子的数量不能大于wow的数量的可能性。此外,由于连接是在安装工艺中进行的,因此当连接端子的数量增加时,存在着由于连接造成的良率降低而导致成本增加的可能性。此外,由于安装工艺中的连接也是单独接合,因此连接所需的时间变长,并且存在着工艺成本增加的可能性。

18.本公开是鉴于这种情况而提出的,其目的在于降低成像装置的制造成本。

19.问题的解决方案

20.根据本技术一个方面的第一成像装置包括:第一半导体元件,其包括被构造为生成像素信号的成像元件;和第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路,其中第一信号处理电路具有比第二信号处理电路多至少一层的结构。

21.根据本技术一个方面的第一电子设备包括第一成像装置。

22.根据本技术一个方面的第二成像装置包括:第一半导体元件,其包括被构造为生成像素信号的成像元件;第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和连接第一信号处理电路和第二信号处理电路的配线,其中所述配线连接设置在第一信号处理电路的最下层的配线层中的端子和设置在第二信号处理电路的最下层的配线层中的端子。

23.根据本技术一个方面的第二电子设备包括第二成像装置。

24.根据本技术一个方面的制造方法是一种用于制造成像装置的制造方法,所述成像装置包括:第一半导体元件,其包括被构造为以像素为单位生成像素信号的成像元件;第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和连接第一信号处理电路和第二信号处理电路的配线,所述制造方法包括:将第一信号处理电路和第二信号处理电路转移到第一半导体元件上的步骤;在第一信号处理电路和第二信号处理电路上形成第一膜的步骤;将设置在第一信号处理电路的最下层的配线层中的第一端子的一部分和设置在第二信号处理电路的最下层的配线层中的第二端子的一部分露出的步骤;和形成连接第一端子和第二端子的配线的步骤。

25.在根据本技术一个方面的第一成像装置和第一电子设备中,设置有:第一半导体元件,其包括被构造为生成像素信号的成像元件;和第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路,其中第一信号处理电路具有比第二信号处理电路多至少一层的结构。

26.在根据本技术一个方面的第二成像装置和第二电子设备中,设置有:第一半导体元件,其包括被构造为生成像素信号的成像元件;第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和连接第一信号处理电路和第二信号处理电路的配线,其中所述配线连接设置在第一信号处理电路的最下层的配线层中的端子和设置在第二信号处理电路的最下层的配线层中的端子。

27.在根据本技术一个方面的制造方法中,制造的成像装置包括:第一半导体元件,其包括被构造为以像素为单位生成像素信号的成像元件;第二半导体元件,在其中通过埋入

构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和连接第一信号处理电路和第二信号处理电路的配线,所述制造方法包括:将第一信号处理电路和第二信号处理电路转移到第一半导体元件上的步骤;在第一信号处理电路和第二信号处理电路上形成第一膜的步骤;将设置在第一信号处理电路的最下层的配线层中的第一端子的一部分和设置在第二信号处理电路的最下层的配线层中的第二端子的一部分露出的步骤;和形成连接第一端子和第二端子的配线的步骤。

28.注意,成像装置和电子设备可以是独立的装置,或者可以是形成一个装置的内部块。

附图说明

29.图1是用于说明良率的图。

30.图2是用于说明制造效率降低的图。

31.图3是用于说明使用凸块的连接的图。

32.图4是用于说明成像装置的制造方法的概要的图。

33.图5是用于说明成像装置的构成例的图。

34.图6是用于说明成像装置的制造方法的图。

35.图7是用于说明成像装置的制造方法的图。

36.图8是用于说明成像装置的制造方法的图。

37.图9是用于说明成像装置的制造方法的图。

38.图10是用于说明成像装置的制造方法的图。

39.图11是用于说明成像装置的制造方法的图。

40.图12是用于说明再配线的容易性的图。

41.图13是用于说明成像装置的另一构成例的图。

42.图14是用于说明成像装置的另一构成例的图。

43.图15是用于说明成像装置的制造方法的概要的图。

44.图16是用于说明成像装置的制造方法的图。

45.图17是用于说明成像装置的制造方法的图。

46.图18是用于说明成像装置的制造方法的图。

47.图19是用于说明配线的制造的图。

48.图20是示出电子设备的示例的图。

49.图21是示出内窥镜手术系统的示意性构成的示例的图。

50.图22是示出摄像头和ccu的功能构成的示例的框图。

51.图23是示出车辆控制系统的示意性构成的示例的框图。

52.图24是示出车外信息检测单元和成像单元的安装位置的示例的说明图。

具体实施方式

53.在下文中,将说明用于实现本技术的形态(在下文中,称为实施方案)。

54.这里,在说明本公开时,将说明专利文献1中公开的晶圆上晶圆(wow)。

55.例如,如图1所示,wow是将成像装置与包括ic的电路(例如信号处理电路和存储电

路)在晶圆状态下接合和层叠的技术。

56.图1示意性地表示wow,其中形成有多个成像元件11的晶圆w1、形成有多个存储电路12的晶圆w2和形成有多个逻辑电路13的晶圆w3以微细对齐的状态被接合并层叠。

57.通过将以此方式层叠的构造切割成单片,例如,形成如图2所示的成像装置。

58.图2的成像装置1通过从上部依次层叠片上透镜、片上滤色器10、成像元件11、存储电路12、逻辑电路13和支撑基板14而构成。

59.这里,通过应用wow技术,可以以微细间距连接将成像元件11和存储电路12电气连接的配线21-1以及将存储电路12和逻辑电路13电气连接的配线21-2。

60.结果,由于可以增加配线的数量,所以可以降低各信号线中的传输速度,并且可以实现省电。

61.然而,由于将要层叠的成像元件11、存储电路12和逻辑电路13各自所需的面积不同,所以在面积比最大的成像元件11小的存储电路12的图中的左右产生既没有形成电路也没有形成配线的空间z1。此外,在面积比存储电路12小的逻辑电路的图中的左右产生既没有形成电路也没有形成配线的空间z2。

62.即,空间z1、z2是由于成像元件11、存储电路12、逻辑电路13各自所需的面积彼此不同而产生的,并且在图2中,是由与作为基准的要求最大面积的成像元件11层叠的结果而发生的。

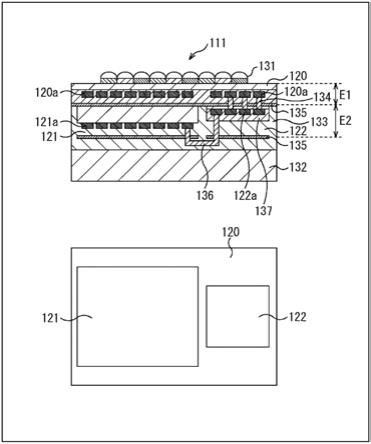

63.这种构成降低了成像装置1的制造效率,结果,制造成本增加。

64.此外,在图1中,在各自晶圆w1~w3中形成的成像元件11、存储电路12和逻辑电路13之中,有缺陷的构成由填充的方块表示。即,图1示出在各晶圆w1~w3中出现两个缺陷。

65.如图1所示,在各自晶圆w1~w3中形成的成像元件11、存储电路12和逻辑电路13中出现的缺陷不一定出现在同一位置。因此,如图1所示,在通过层叠形成的成像装置1中,在成像元件11的晶圆w1上出现带有十字标记的六个缺陷。

66.结果,在六个缺陷的成像装置1中,成像元件11、存储电路12和逻辑电路13均被视为具有六个缺陷,尽管在成像元件11、存储电路12和逻辑电路13的三个部件之中的至少两个部件没有缺陷。因此,通过整合晶圆的数量而获得的良率数均为6个,而原本各部件的良率数可能是2个。

67.结果,成像装置1的良率降低,并且制造成本增加。

68.此外,如图3所示,可以设想将具有不同芯片尺寸的成像元件11、存储电路12和逻辑电路13切割成单片,选择性地仅配置良品,并且通过形成小的凸块来连接。

69.在图3的成像装置1中,片上透镜、片上滤色器10和成像元件11从上部层叠,在其下存储电路12和逻辑电路13层叠在同一层中,并且支撑基板14设置在其下方并层叠。此外,成像元件11与配置在同一层中的存储电路12和逻辑电路13经由小凸块31电气连接。

70.在图3的成像装置1中,被选作良品的不同尺寸的芯片经由凸块31连接,并且降低了各晶圆的制造效率差异和各芯片的良率的影响。

71.然而,难以形成小凸块31,并且减小如图3所示的连接间距d2是有限度的,使得连接间距d2不能小于在使用wow的情况下的图2的连接间距d1。

72.为此,使用凸块层叠的图3的成像装置1不能具有比通过wow层叠的图2的成像装置1更大的连接端子数量。此外,在如同图3的成像装置1中那样使用凸块进行连接的情况下,

当连接端子的数量增加时,由于在安装工艺中进行接合,因此会出现与接合相关的良率降低,并且成本增加。此外,由于在安装工艺中凸块的连接也是单独的操作,因此各工艺的时间长,并且工艺成本也增加。

73.如上所述,本公开的成像元件从制造效率、安装成本和工艺成本的观点来看降低了与制造相关的成本。

74.《关于晶圆的层叠》

75.图4是用于说明其中通过在制造本公开的成像装置时应用的wow技术来层叠多个晶圆的结构的图。

76.在制造本公开的成像装置时,在配线精确对准的状态下层叠两个晶圆,而两个晶圆包括:晶圆101,其上形成有多个成像元件(互补金属氧化物半导体(cmos)图像传感器)或电荷耦合器件(ccd))120;以及其上再配置有存储电路122和逻辑电路121的支撑基板102。

77.在晶圆101中,通过半导体工艺形成多个成像元件120。

78.在支撑基板102上,再配置多个存储电路122,其通过半导体工艺形成在晶圆103上,切割成单片,然后单独地进行电气检查,并确认为良品芯片。

79.在支撑基板102上,再配置多个逻辑电路121,其通过半导体工艺形成在晶圆104上,切割成单片,然后单独地进行电气检查,并确认为良品芯片。

80.《成像装置的构成例》

81.图4是用于说明其中通过在制造本公开的成像装置时应用的晶圆上芯片(cow,chip on wafter)技术和wow技术的组合来层叠多个晶圆的结构的图。通过如图4所示的cow技术和wow技术来层叠多个晶圆,然后切割成单片,形成本公开的成像装置111(图5)。

82.本公开的成像装置具有例如图5所示的构成。注意,在图5中,上部是侧面断面图,下部是示出当从上表面观察时成像元件120与逻辑电路121和存储电路122的水平方向的配置关系的图。

83.在图5的上部的成像装置111中,从图中的上部开始,片上透镜、片上滤色器131和成像元件120层叠,在其下逻辑电路121和存储电路122在同一层的左右侧配置和层叠,并且在其下形成支撑基板132。即,如图5的上部所示,图5的成像装置111包括:半导体元件层e1,其包括由晶圆101形成的成像元件120;和半导体元件层e2,其包括形成在支撑基板102上的逻辑电路121和存储电路122。

84.在成像元件120的端子120a之中,存储电路122上的端子120a通过由cucu连接而连接的配线134电气连接到存储电路122的端子121a。

85.尽管图5中未示出,但是可以采用这样的构成,其中在成像元件120的端子120a之中的逻辑电路121上的端子120a可以被构造为通过cucu连接而连接到逻辑电路121的端子122a。

86.在图5的上部所示的示例中,示出了如下的示例,其中成像元件120和逻辑电路121不直接连接,而是通过构造成使得逻辑电路121和存储电路122通过配线136连接并且存储电路122和成像元件120连接而间接连接逻辑电路121和成像元件120。

87.在其中形成逻辑电路121和存储电路122的半导体元件层e2中,逻辑电路121和存储电路122周围的空间处于被氧化膜133填充的状态。结果,在半导体元件层e2中,逻辑电路121和存储电路122处于埋在氧化膜133中的状态。

88.此外,在其上形成有成像元件120的半导体元件层e1与其上形成有逻辑电路121和存储电路122的半导体元件层e2之间的边界处,通过氧化膜接合而形成氧化膜接合层135并接合。此外,通过氧化膜接合形成氧化膜接合层135而将逻辑电路121和存储电路122的半导体元件层e2与支撑基板132接合。

89.逻辑电路121的端子121a处于埋在氧化膜133中的状态。存储电路122的端子122a埋在增厚层(bulking layer)137中。尽管后面将说明增厚层137,但是由于设置有增厚层137,因此存储电路122的端子122a被构造为位于靠近作为连接目的地的成像元件120的端子120a的位置处。

90.在将逻辑电路121和存储电路122进行比较的情况下,存储电路122比逻辑电路121多至少一层。这里,举例说明了其中增厚层137被设置为多的至少一层的情况。与增厚层137对应的层可以是多层。

91.增厚层137也可以设置为氧化膜。在增厚层137设置为氧化膜的情况下,其可以包含与层叠在增厚层137上的氧化膜133相同的材料。在这种情况下,增厚层137和氧化膜133可以被视为是一层。在这种实施方案的情况下,这一层被构造为厚的。“被构造为厚的”是指厚度大于没有增厚层137的电路(例如,逻辑电路121)的氧化膜133的厚度。

92.换句话说,当将逻辑电路121的预定层a与对应于逻辑电路121的预定层a的存储电路122的层b进行比较时,层b被构造为比层a厚。层b包括增厚层137,并且通过包括增厚层137,层b被构造为比层a厚。

93.此外,如图5的下部所示,当从上表面观察时,逻辑电路121和存储电路122被配置为包含在最上层的成像元件120所存在的范围内。通过这样的配置,在逻辑电路121和存储电路122的层中,减少了逻辑电路121和存储电路122以外的空闲空间,这使得可以提高制造效率。

94.在图4的支撑基板102上,当各个成像装置111被切割成单片时,逻辑电路121和存储电路122被精确地调整和再配置,使得在从各自上表面观察时配置在成像元件120的范围内。

95.《图5中的成像装置的制造方法》

96.接下来,将参照图6~11说明图5的成像装置111的制造方法。

97.在图6的步骤s11~s14中,制造逻辑电路121。在步骤s11中,准备其上形成有逻辑电路121的晶圆103。在晶圆103的各逻辑电路121中,在逻辑电路121上形成端子121a,以覆盖端子121a的方式形成氧化膜133,进而形成氧化膜接合层135。

98.在步骤s12中,将切割带151贴附到晶圆103。此外,将贴附有切割带151的晶圆103固定到环形框架152(也称为切割框架等)。

99.在步骤s13中,晶圆103被切割以切出逻辑电路121。在步骤s14中,通过拉伸晶圆103在切出的逻辑电路121之间形成间隙。从这种状态,从切割带151剥离各个逻辑电路121并转移到支撑基板102上(步骤s15)。

100.注意,如图6所示,具有不同尺寸的逻辑电路121可以形成在一个晶圆103上并且被切割成单片。

101.在图7的步骤s21~s24中,制造存储电路122。在步骤s21中,准备其上形成有存储电路122的晶圆104。在晶圆104的各存储电路122中,在存储电路122上形成端子122a,并且

以覆盖端子122a的方式形成增厚层137。此外,在增厚层137上形成氧化膜133,进而形成氧化膜接合层135。

102.与逻辑电路121相比,存储电路122具有其中添加有一层增厚层137的构成。设置增厚层137以促进将电路的再配线进行再配线。增厚层137可以包含氧化膜。

103.在将图6的步骤s11所示的逻辑电路121(的晶圆103)与图7的步骤s21所示的存储电路122(的晶圆104)进行比较的情况下,其不同之处在于,存储电路122形成有增厚层137,逻辑电路121未形成增厚层137。

104.在图7的步骤s22中,将切割带153贴附到晶圆104。此外,将贴附有切割带153的晶圆104固定到环形框架154。

105.在步骤s23中,晶圆104被切割以切出存储电路122。在步骤s24中,通过拉伸晶圆104在切出的存储电路122之间形成间隙。从这种状态,从切割带153剥离各个存储电路122并转移到支撑基板102上(步骤s15)。

106.如上所述,在步骤s15中,单独制造的逻辑电路121和存储电路122被转移到支撑基板102上。

107.注意,如图7所示,具有不同尺寸的存储电路122可以形成在一个晶圆103上并且被切割成单片。

108.当制造进行到在步骤s15(图6或图7)中将逻辑电路121和存储电路122放置在支撑基板102上的状态时,在步骤s31(图8)中进行减薄。

109.减薄前的逻辑电路121和存储电路122具有如步骤s15所示的不同的高度。换句话说,存储电路122形成得比逻辑电路121高出与增厚层137的形成相对应的量。

110.在步骤s31中,将逻辑电路121和存储电路122的图中的上面部分的硅层(晶圆103和104,以下适宜地称为硅层103和104)减薄到不影响器件特性的高度。

111.在步骤s32中,进行背面侧的再配线。这里,以对存储电路122进行再配线而未对逻辑电路121进行再配线的情况为例进行说明。再配线是通过对期望在存储电路122的硅层104上形成配线134的部分进行开口并且用诸如铜等导电材料填充该部分。

112.在步骤s33(图9)中,进行对准,使得来自支撑基板102中的存储电路122的端子122a的配线134和来自晶圆101中的成像元件120的端子120a的配线134处于适宜地彼此面对的位置。

113.然后,晶圆101和支撑基板102通过wow接合,使得来自支撑基板102中的存储电路122的端子122a的配线134通过cucu接合连接到来自晶圆101中的成像元件120的端子120a的配线134。该处理导致支撑基板102的各存储电路122电气连接到晶圆101的各成像元件120的状态。

114.在步骤s34中,剥离支撑基板102。例如,支撑基板102通过脱接合或蚀刻被去除。

115.在步骤s35中,执行埋入。如步骤s35所示,形成用作绝缘膜的氧化膜133。此时,氧化膜133的表面在对应于逻辑电路121和存储电路122的高度处被平坦化。

116.在步骤s36(图10)中,形成硅通孔(tsv)161。tsv 161形成在用于形成连接逻辑电路121和存储电路122的配线136的部分中。

117.在步骤s37中,通过在tsv 161中和连接tsv 161的水平方向的再配线部分中填充例如铜(cu)、钨(w)、多晶硅等来形成配线136。

118.在步骤s38中,形成用作绝缘膜的氧化膜133,从而也覆盖配线136,并且将包括配置的存储电路122和逻辑电路121的芯片埋入。此时,氧化膜133的表面在对应于逻辑电路121和存储电路122的高度处被平坦化。

119.在步骤s39(图11)中,将支撑基板162贴附到在步骤s38中形成的氧化膜133上。在步骤s40中,对作为成像元件120的图中上层的硅层(对应于晶圆101的层)进行减薄。

120.在步骤s41中,在成像元件120上设置片上透镜和片上滤色器131,并且进行切割成单片以完成成像装置111。

121.利用这样的构成,由于成像元件120和存储电路122的电路之间的连接可以是通过类似于wow的半导体光刻技术以微细配线的配线密度形成端子的连接,因此可以增加连接端子的数量,并且可以降低各配线中的信号处理速度,从而能够降低功耗。

122.此外,在成像元件120和逻辑电路121的电路被形成为彼此连接的情况下,由于可以通过以微细配线的配线密度形成端子来进行连接,因此可以增加连接端子的数量,并且可以降低各配线中的信号处理速度,从而能够降低功耗。

123.此外,由于在逻辑电路121和存储电路122中仅仅连接良品芯片,因此作为wow的缺点的各晶圆的缺陷减少,因此可以减少良率损失的发生。

124.此外,如图5的下部所示,与wow不同,由于与成像元件120的芯片尺寸无关地通过使尺寸尽可能小而可以以独立的岛形状配置将要连接的存储电路122和逻辑电路中的每一个,因此可以提高将要连接的逻辑电路121和存储电路122的制造效率。

125.结果,由于成像元件120要求最低限的像素尺寸以对光起反应,因此成像元件120的制造工艺不必须要求微细配线工艺,从而可以降低工艺成本。此外,在逻辑电路121的制造工艺中,通过使用最先进的微细配线工艺可以降低功耗。此外,可以提高逻辑电路121和存储电路122的制造效率。结果,可以降低与成像装置111的制造相关的成本。

126.此外,由于芯片可以在晶圆中再对齐并接合的结构,因此即使在不同类型工艺(其中在同一晶圆内难以制作诸如电源ic和时钟等模拟电路、逻辑电路121以及由完全不同的工艺制成的构成)的情况下或者甚至当晶圆尺寸存在差异时,也可以在一个芯片中进行层叠。

127.此外,上面已经说明了逻辑电路121和存储电路122用作连接到成像元件120的电路的示例。然而,可以使用逻辑电路121和存储电路122以外的电路,只要其是成像元件120的操作所需的信号处理电路,例如与成像元件120的控制相关的电路或者与捕获的像素信号的处理相关的电路。成像元件120的操作所需的信号处理电路例如可以是电源电路、图像信号压缩电路、时钟电路、光通信转换电路等。

128.《关于增厚层》

129.在上述的示例中,已经示出了其中存储电路122设置有增厚层137并且逻辑电路121未设置增厚层137的示例。将再次参照图5的上部所示的成像装置111的构成。存储电路122的端子122a和成像元件120的端子120a通过配线134连接。逻辑电路121的端子121a和成像元件120的端子120a未连接。

130.存储电路122的端子122a设置在比逻辑电路121的端子121a更靠近端子120a的一侧。即,连接到端子120a的端子122a设置在比未连接的端子122a更靠近端子120a的一侧。通过为存储电路122设置增厚层137,可以将存储电路122的端子122a设置在靠近成像元件120

的端子120a的位置处。

131.换句话说,通过为存储电路122设置增厚层137,可以将存储电路122的硅层104的厚度形成为较薄,并且可以将存储电路122的端子122a设置在靠近成像元件120的端子120a的位置。

132.这将参照图12进行说明。图12的a是用于说明未设置增厚层137的情况(换句话说,在常规制造步骤中制造成像装置111的情况)的图。图12的b是用于说明设置有增厚层137的情况(换句话说,在上述制造步骤中制造成像装置111的情况)的图。

133.如图12的a的左图所示,逻辑电路121和存储电路122'具有其中氧化膜接合层135、氧化膜133和硅层103(硅层104')层叠在支撑基板102上的构成。注意,为了与本技术适用的存储电路122区别,未设置增厚层137的存储电路122通过添加撇号被记述为存储电路122'。

134.如图12的a的右图所示,从图12的a的左图所示的状态进一步层叠成像元件120。此外,成像元件120的端子120a和存储电路122'的端子122a'通过配线134'连接。配线134'的长度定义为长度l1。

135.在设置增厚层137的情况下,如图12的b的左图所示,逻辑电路121具有其中氧化膜接合层135、氧化膜133和硅层103层叠在支撑基板102上的构成。此外,存储电路122具有氧化膜接合层135、氧化膜133、增厚层137和硅层103层叠在支撑基板102上的构成。

136.如图12的b的右图所示,从图12的b的左图所示的状态进一步层叠成像元件120。此外,成像元件120的端子120a和存储电路122的端子122a通过配线134连接。配线134的长度定义为长度l2。

137.如图12的b的左图所示,硅层103和硅层104的厚度不同,并且硅层104形成为比硅层103薄了增厚层137的厚度。

138.长度l1和长度l2是配线134(134')的长度,但是该长度取决于硅层104的厚度。因此,当硅层104的厚度很薄时,配线134的长度变短。即,在图12所示的示例的情况下,显然满足长度l1》长度l2。

139.一般地,形成短配线比形成长配线容易。例如,在形成过孔以形成配线134的情况下,与形成更深过孔的情况相比,可以在更短的时间内更容易地形成更浅的过孔。

140.根据本技术,由于存储电路122的硅层104的厚度可以形成为较薄,因此在步骤s32(图8)中,容易在存储电路122的端子122a上形成配线134。

141.如上所述,可以采用其中需要再配线的电路(芯片)设置有增厚层137以促进再配线的构成。

142.在上述示例中,已经说明了逻辑电路121和存储电路122用作连接到成像元件120的电路的示例。然而,可以使用逻辑电路121和存储电路122以外的电路,只要其是成像元件120的操作所需的信号处理电路,例如与成像元件120的控制相关的电路或者与捕获的像素信号的处理相关的电路。

143.此外,在上述示例中,已经将存储电路122设置有增厚层137的情况作为示例进行说明,但是逻辑电路121设置有增厚层137的构成也是可能的。此外,还可以具有在逻辑电路121和存储电路122两者中都设置增厚层137的构成。此外,在逻辑电路121和存储电路122两者都设置有增厚层137的构成的情况下,增厚层137的厚度可以相同或不同。

144.本技术还可以适用于具有多个电路(芯片)安装在一个芯片上的构成的器件。即,

多个芯片可以形成为设置有增厚层的芯片或者未设置增厚层的芯片,并且可以安装在一个芯片上。此外,在设置有增厚层的多个芯片安装在一个芯片上的情况下,对于每个芯片可以使增厚层的厚度不同。

145.《关于将电路彼此连接的配线》

146.例如,在图5的上部所示的成像装置111中,逻辑电路121和存储电路122通过配线136连接。如图5的上部所示,配线136设置为将逻辑电路121内的端子121a和存储电路122的端子122a连接。配线136可以具有如图13所示的形状。

147.在图13所示的成像装置111中,逻辑电路121的端子121b和存储电路122的端子122b通过配线201连接。端子121b是逻辑电路121的端子121a之中的更靠近存储电路122一侧的端子。端子122b是存储电路122的端子122a之中的更靠近逻辑电路121一侧的端子。

148.端子121b和端子122b被设置为与配线201连接的端子。注意,这里,已经举例说明了其中设于逻辑电路121中的端子121a之中的靠近存储电路122侧的端子121b是连接到配线201的端子的情况,但是将要连接到配线201的端子121b可以是新设置的。类似地,这里,已经举例说明了其中设于存储电路122中的端子122a之中的靠近逻辑电路121侧的端子122b是连接到配线201的端子的情况,但是将要连接到配线201的端子122b可以是新设置的。

149.配线201沿着逻辑电路121的硅层103的侧面、设置在成像元件120侧的氧化膜接合层135以及存储电路122的硅层104的侧面形成,并且形成为将端子121b和端子122b连接。

150.这种配线也可以适用于具有如图14所示的构成的成像装置211。将图14所示的成像装置211与图5的上部所示的成像装置111进行比较,其构成上的不同之处在于,成像装置211的存储电路222未设置增厚层137。此外,在构成上,成像装置211的逻辑电路221和存储电路222分别设有端子221b和端子222b,逻辑电路221和存储电路222通过由配线242连接的端子221b和端子222b而连接。

151.注意,在图14所示的成像装置211中,已经示出了逻辑电路221和成像元件220通过配线234连接的示例。然而,类似于图5所示的成像装置111,可以采用其中逻辑电路221和成像元件220未通过配线234连接的构成。即,本技术可以适用而不管逻辑电路221和成像元件220是否直接连接。

152.将进一步说明图14所示的成像装置211的构成。在图14中的成像装置211中,从图中的上部开始,片上透镜、片上滤色器231和成像元件220层叠,在其下存储电路222和逻辑电路221在同一层中的左右两侧配置和层叠,并且在其下形成支撑基板232。即,如图14所示,图14的成像装置211包括:半导体元件层e1,其包括由晶圆101形成的成像元件220;和半导体元件层e2,其包括形成在支撑基板102上的存储电路222和逻辑电路221。

153.在成像元件220的端子220a之中,逻辑电路221上的端子220a通过由cucu连接而连接的配线234电气连接到逻辑电路221的端子211a。

154.此外,在成像元件220的端子220a之中,存储电路222上的端子220a通过由cucu连接而连接的配线234电气连接到存储电路222的端子222a。

155.在其中形成有逻辑电路221和存储电路222的半导体元件层e2中,存储电路222和逻辑电路221周围的空间处于被氧化膜233填充的状态。结果,在半导体元件层e2中,存储电路222和逻辑电路221处于埋在氧化膜233中的状态。

156.此外,在其上形成有成像元件220的半导体元件层e1与其上形成有存储电路222和逻辑电路221的半导体元件层e2之间的边界处,通过氧化膜接合而形成氧化膜接合层235并接合。此外,通过氧化膜接合形成氧化膜接合层235而将存储电路222和逻辑电路221的半导体元件层e2与支撑基板232接合。

157.此外,逻辑电路221和存储电路222通过配线242连接。配线242设置为将逻辑电路221的端子221b和存储电路222的端子222b连接。为了进行如后所述的制造,在配线242的一部分上设置保护膜241。

158.端子221b和端子222b分别与端子221a和端子222a分开设置,并且被设置为将逻辑电路221和存储电路222连接的端子。

159.配线242从端子221b沿着逻辑电路221的侧面、氧化膜接合层235和存储电路222的侧面设置,并且与端子222b连接。此外,保护膜241设置在配线242与逻辑电路221、氧化膜接合层235和存储电路222的侧面之间。

160.《关于成像装置211的制造》

161.图15是用于说明在晶圆101上的成像元件220中直接形成已经被切割成单片并被确认为良品芯片的逻辑电路221和存储电路222的成像装置的制造方法的图。

162.在晶圆101中,通过半导体工艺形成多个成像元件220。此外,在晶圆101上形成的成像元件220上,选择并再配置:多个逻辑电路221,其通过半导体工艺形成在晶圆103上,切割成单片,然后单独地进行电气检查,并确认为良品芯片;和多个存储电路222,其通过半导体工艺形成在晶圆104上,切割成单片,然后单独地进行电气检查,并确认为良品芯片。

163.即,由于被确认为良品芯片的逻辑电路221和存储电路222被再配置在成像元件220上,所以这里,逻辑电路221和存储电路222二者被构造为小于成像元件220。

164.《成像装置211的制造方法》

165.接下来,将参照图16~18说明作为图14的成像装置211的制造方法的如图15所示地将逻辑电路221和存储电路222直接转移到成像元件220上的情况。

166.在步骤s51中,将经过电气检查并确认为良品的逻辑电路221和存储电路222转移到晶圆101上的成像元件220上,并在端子220a、221a和222a处形成配线234。

167.此外,对于来自逻辑电路221的端子221a和存储电路222的端子222a的配线234适宜地面对来自晶圆101中的成像元件220的端子220a的配线234的位置,进行对准,通过cucu接合进行连接,并且通过氧化膜接合形成氧化膜接合层235而接合面对的层。

168.当逻辑电路221和存储电路222被转移到成像元件220时,逻辑电路221的端子221b和存储电路222的端子222b被放置为彼此面对。

169.当制造逻辑电路221时,端子221b与端子221a一起形成。此外,当制造存储电路222时,端子222b与端子222a一起形成。例如,在形成逻辑电路221和存储电路222的下层配线时的同时形成端子221b和222b。因此,可以在不增加用于形成端子221b和222b的多个步骤的情况下进行制造。

170.在步骤s52中,形成用于保护逻辑电路221和存储电路222的保护膜241。保护膜241形成在逻辑电路221的不与成像元件220接触的三边上。此外,保护膜241形成在存储电路222的不与成像元件220接触的三边上。保护膜241可以包含例如sin或sio2。此外,保护膜241可以具有多层(层叠膜)结构而不是单层。

171.在步骤s53中,减薄逻辑电路221的硅层103和存储电路222的硅层104。保护膜241形成在逻辑电路221的硅层103和存储电路222的硅层104上,并且在减薄时一起研磨。在硅减薄后去除污染物或灰尘时,保护膜241的一部分被剥离,并且可以清洁表面。

172.在步骤s54(图17)中,通过使用图案化工艺,执行露出用于连接逻辑电路221和存储电路222的专用端子(即,在这种情况下,端子221b和222b)的加工。在步骤s54中,为了便于图案化,可以在逻辑电路221和存储电路222之间的间隙部分中埋入预定材料,并且在保证表面平坦性后进行露出处理。

173.在步骤s55中,形成连接端子221b和端子222b的配线242。配线242包含诸如铜(cu)、钨(w)或铝(al)等金属。使用抗蚀剂图案化和加工工艺形成配线242。可选择地,如图19所示,配线252也可以通过使用以下方法形成:仅在连接端子221b和端子222b的部分处打开抗蚀剂301,曝光而形成金属溅射膜,并且剥离抗蚀剂301。

174.在步骤s56中,将逻辑电路221和存储电路222的图中的上面部分的硅层减薄到不影响器件特性的高度,形成用作绝缘膜的氧化膜233,并且埋入包括再配置的逻辑电路221和存储电路222的芯片。

175.在步骤s57(图18)中,将支撑基板232接合到逻辑电路221和存储电路222上。此时,通过氧化膜接合形成氧化膜接合层235而接合支撑基板232的面对逻辑电路221和存储电路222的层。

176.在步骤s58中,执行上下反转使得成像元件220在上侧,并且对作为成像元件220的图中上层的硅层进行减薄。

177.在步骤s59中,在成像元件220上设置片上透镜和片上滤色器231,并且进行切割成单片以完成成像装置211。

178.如上所述,可以获得其中逻辑电路221和存储电路222通过配线242连接的结构。配线242连接到专用于连接配线242的端子221b和端子222b。端子221b和端子222b可以在制造逻辑电路221和存储电路222时与最下层的配线层同时形成。即,可以在不增加用于形成端子221b和端子222b的步骤数量的情况下形成端子221b和端子222b。

179.此外,形成连接端子221b和222b的配线242的步骤不包括贯通基板或者将基板雕刻到较深位置的处理,从而可以容易地形成配线242。

180.形成配线242的步骤是上述说明中的步骤s52~s55。在这些步骤中,没有在硅层中形成深沟槽的工艺,在通过防反射(ar)涂层而具有防反射结构的成像装置的情况下没有在ar涂层中打孔并埋入金属的工艺,没有金属的化学机械抛光(cmp)工艺等。由于可以通过不需要这些工艺的制造步骤形成配线242,因此可以容易地形成配线242。

181.此外,通过形成保护膜241,可以在构成中保持芯片之间的绝缘。

182.本技术不仅适用于具有上述构成的成像装置,而且还适用于具有其他构成的成像装置。

183.本技术还可以适用于具有多个电路(芯片)安装在一个芯片上的构成的器件。即,多个芯片可以形成为设置有增厚层的芯片或者未设置增厚层的芯片,并且可以安装在一个芯片上。此外,在设置有增厚层的多个芯片安装在预定芯片上的情况下,对于每个芯片可以使增厚层的厚度不同。

184.此外,通过将连接芯片的配线构造为上述配线242,可以获得诸如易于制造等优

点。

185.《电子设备的适用例》

186.上述成像元件可以适用于各种电子设备,例如诸如数码相机和数码摄像机等成像装置、具有成像功能的移动电话或具有成像功能的其他设备。

187.图20是示出作为本技术适用的电子设备的成像装置的构成例的框图。

188.图20所示的成像装置501包括光学系统502、快门装置503、成像元件504、驱动电路505、信号处理电路506、监视器507和存储器508,并且可以捕捉静止图像和动态图像。

189.光学系统502具有一个或多个透镜,并且将来自被摄体的光(入射光)引导到成像元件504并在成像元件504的光接收面上形成图像。

190.快门装置503设置在光学系统502和成像元件504之间,并且根据驱动电路505的控制来控制对成像元件504的光照射期间和遮光期间。

191.成像元件504包括包含上述成像元件的封装。成像元件504根据经由光学系统502和快门装置503在光接收面上形成为图像的光而累积一定期间的信号电荷。累积在成像元件504中的信号电荷根据从驱动电路505供给的驱动信号(定时信号)而传输。

192.驱动电路505输出用于控制成像元件504的传输操作和快门装置503的快门操作的驱动信号,以驱动成像元件504和快门装置503。

193.信号处理电路506对从成像元件504输出的信号电荷进行各种信号处理。通过信号处理电路506进行信号处理获得的图像(图像数据)被供给到监视器507以进行显示,或者供给到存储器508以进行存储(记录)。

194.同样地,在上述构成的成像装置501中,通过将上述成像装置111(成像装置211)适用于光学系统502和成像元件204,可以提高良率并降低制造成本。

195.《成像元件的使用例》

196.例如,使用上述成像元件可以用于如下所述的对诸如可见光、红外光、紫外光和x射线等光进行感测的各种情况。

[0197]-拍摄图像以用于鉴赏的装置,例如,数码相机或具有相机功能的便携式装置。

[0198]-交通用装置,例如,拍摄车辆的前方、后方、周围、内部等的图像以用于诸如自动停车等安全驾驶、识别驾驶员的状况等的车载传感器、监视行驶车辆和道路的监视相机以及测量车辆间距离等的测距传感器。

[0199]-家用电器用装置,例如,电视机、冰箱和空调,以拍摄使用者的姿态的图像并根据该姿态来进行装置操作。

[0200]-医疗或保健用装置,例如,内窥镜或通过接收红外光进行血管造影的装置。

[0201]-安保用装置,例如,用于预防犯罪的监视相机或用于个人身份认证的相机。

[0202]-美容护理用装置,例如,用于拍摄皮肤的图像的皮肤测量仪和用于拍摄头皮的图像的显微镜。

[0203]-运动用装置,例如,用于运动用途等的运动相机或可穿戴式相机。

[0204]-农业用装置,例如,用于监视田地和农作物的状况的相机。

[0205]

《内窥镜手术系统的应用例》

[0206]

根据本公开的技术可以适用于各种产品。例如,根据本公开的技术可以应用于内窥镜手术系统。

[0207]

图21是示出了根据本公开的技术(本技术)可以适用的内窥镜手术系统的示意性构成的示例的图。

[0208]

图21示出了手术者(医生)11131正在使用内窥镜手术系统11000对病床11133上的患者11132进行手术的状态。如图所示,内窥镜手术系统11000包括内窥镜11100、诸如气腹管11111和能量处置器械11112等其他手术器械11110、支撑内窥镜11100的支撑臂装置11120以及其上安装有用于内窥镜手术的各种装置的推车11200。

[0209]

内窥镜11100包括其中距远端预定长度的区域被插入患者11132的体腔内的透镜筒11101和摄像头11102,该摄像头与透镜筒11101的近端连接。在所示的示例中,示出了构造为具有硬性透镜筒11101的所谓硬镜的内窥镜11100,但是内窥镜11100可以构造为具有软性透镜筒的所谓的软镜。

[0210]

在透镜筒11101的远端处设有物镜装配到其中的开口部。光源装置11203与内窥镜11100连接,并且将由光源装置11203生成的光通过延伸到透镜筒11101内部的光导引导到透镜筒的远端,并经由物镜将光朝向在患者11132的体腔内的观察对象发射。注意,内窥镜11100可以是直视镜、斜视镜或侧视镜。

[0211]

在摄像头11102的内部设有光学系统和成像元件,并且来自观察对象的反射光(观察光)通过光学系统会聚在成像元件上。观察光由成像元件执行光电转换,并且生成与观察光相对应的电气信号,即,与观察图像相对应的图像信号。图像信号作为raw数据被传输到相机控制单元(ccu)11201。

[0212]

ccu 11201包括中央处理单元(cpu)、图形处理单元(gpu)等,并且综合控制内窥镜11100和显示装置11202的操作。此外,ccu 11201接收来自摄像头11102的图像信号,并且执行诸如对图像信号的显像处理(去马赛克处理)等各种类型的图像处理以基于该图像信号显示图像。

[0213]

显示装置11202在ccu 11201的控制下显示基于已经由ccu 11201对其进行了图像处理的图像信号的图像。

[0214]

例如,光源装置11203包括诸如发光二极管(led)等光源,并且将用于拍摄手术部位等的图像的照射光供给到内窥镜11100。

[0215]

输入装置11204是用于内窥镜手术系统11000的输入接口。使用者可以经由输入装置11204向内窥镜手术系统11000输入各种类型的信息和指令。例如,使用者输入用于改变内窥镜11100的成像条件(照射光的类型、放大率、焦距等)的指令等。

[0216]

处置器械控制装置11205控制能量处置器械11112的驱动,用于组织的烧灼和切开、血管的密封等。气腹装置11206经由气腹管11111向患者11132的体腔内注入气体以使体腔膨胀,以确保内窥镜11100的视野并确保手术者的工作空间。记录器11207是能够记录与手术有关的各种类型的信息的装置。打印机11208是能够以诸如文本、图像或图形等各种形式打印与手术有关的各种类型的信息的装置。

[0217]

注意,将对手术部位进行成像时的照射光供给到内窥镜11100的光源装置11203可以包括例如led、激光光源或包括它们组合的白色光源。在白色光源包括rgb激光光源的组合的情况下,由于可以高精度地控制各种颜色(各种波长)的输出强度和输出定时,所以可以在光源装置11203中进行所拍摄的图像的白平衡的调整。此外,在这种情况下,通过将来自各个rgb激光光源的激光按时间分割地发射到观察对象上并且与发射定时同步地控制摄

像头11102的成像元件的驱动,也能够按时间分割地拍摄对应于各个rgb的图像。根据该方法,在成像元件中未设置滤色器的情况下,可以获得彩色图像。

[0218]

此外,可以控制光源装置11203的驱动,使得每隔预定时间改变要输出的光的强度。通过与光强度的改变的定时同步地控制摄像头11102的成像元件的驱动以按时间分割地获取图像并合成图像,能够生成没有所谓的遮挡阴影和曝光过度的高亮的高动态范围的图像。

[0219]

此外,光源装置11203可以构造成能够供给与特殊光观察相对应的预定波长带的光。在特殊光观察中,例如,使用身体组织中的光吸收的波长依赖性,通过发射与普通观察时的照射光(即,白光)相比具有窄带域的光,进行以高对比度对诸如粘膜表层的血管等预定组织进行成像的所谓的窄带域成像。可选择地,在特殊光观察中,可以进行通过发射激发光产生的荧光获得图像的荧光观察。在荧光观察中,例如,能够向身体组织照射激发光来观察来自身体组织的荧光(自体荧光成像),或者能够将诸如吲哚菁绿(icg)等试剂局部注射到身体组织中并发射与试剂的荧光波长相对应的激发光来获得荧光图像。光源装置11203可以构造成能够供给与这种特殊光观察相对应的窄带域光和/或激发光。

[0220]

图22是示出了图21所示的摄像头11102和ccu 11201的功能构成的示例的框图。

[0221]

摄像头11102包括透镜单元11401、成像单元11402、驱动单元11403、通信单元11404和摄像头控制单元11405。ccu 11201包括通信单元11411、图像处理单元11412和控制单元11413。摄像头11102和ccu11201通过传输线缆11400彼此通信连接。

[0222]

透镜单元11401是设置在与透镜筒11101的连接部分处的光学系统。从透镜筒11101的远端接收的观察光被引导到摄像头11102并入射到透镜单元11401上。透镜单元11401通过组合包括变焦透镜和焦点透镜的多个透镜来构造。

[0223]

成像单元11402包括成像元件。构成成像单元11402的成像元件的数量可以是一个(所谓的单板型)或者多个(所谓的多板型)。在成像单元11402构造成多板型的情况下,例如,可以通过各个成像元件生成与rgb相对应的图像信号,并且可以通过对图像信号进行合成来获得彩色图像。可选择地,成像单元11402可以包括一对成像元件,用于获取与三维(3d)显示相对应的右眼和左眼用的图像信号。通过进行3d显示,手术者11131可以更加准确地把握手术部位中的活体组织的深度。注意,在成像单元11402构造成多板型的情况下,可以设置与各个成像元件相对应的多个透镜单元11401。

[0224]

此外,成像单元11402不必须设置在摄像头11102中。例如,成像单元11402可以设置在透镜筒11101内部的物镜的正后方。

[0225]

驱动单元11403包括致动器,并且在摄像头控制单元11405的控制下使透镜单元11401的变焦透镜和聚焦透镜沿着光轴移动预定距离。结果,可以适宜地调整由成像单元11402拍摄的图像的放大率和焦点。

[0226]

通信单元11404包括用于向/从ccu 11201传输/接收各种类型的信息的通信装置。通信单元11404将从成像单元11402获取的图像信号作为raw数据经由传输线缆11400传输到ccu 11201。

[0227]

此外,通信单元11404从ccu 11201接收用于控制摄像头11102的驱动的控制信号,并将该控制信号供给到摄像头控制单元11405。例如,控制信号包括与成像条件有关的信息,如指定所拍摄的图像的帧速率的信息、指定在成像时的曝光值的信息和/或指定所拍摄

的图像的放大率和焦点的信息等。

[0228]

注意,诸如帧速率、曝光值、放大率和焦点等成像条件可以由使用者适宜地指定,或者可以由ccu 11201的控制单元11413基于获取的图像信号来自动设定。在后一种情况下,所谓的自动曝光(ae)功能、自动对焦(af)功能和自动白平衡(awb)功能设置在内窥镜11100中。

[0229]

摄像头控制单元11405基于经由通信单元11404接收的来自ccu 11201的控制信号来控制摄像头11102的驱动。

[0230]

通信单元11411包括用于向/从摄像头11102传输/接收各种类型的信息的通信装置。通信单元11411经由传输线缆11400接收从摄像头11102传输的图像信号。

[0231]

此外,通信单元11411将用于控制摄像头11102的驱动的控制信号传输到摄像头11102。图像信号和控制信号可以通过电气通信、光通信等来传输。

[0232]

图像处理单元11412对作为从摄像头11102传输的raw数据的图像信号进行各种类型的图像处理。

[0233]

控制单元11413进行与通过内窥镜11100进行的手术部位等的成像以及通过对手术部位等的成像获得的所拍摄的图像的显示有关的各种类型的控制。例如,控制单元11413生成用于控制摄像头11102的驱动的控制信号。

[0234]

此外,控制单元11413基于已经由图像处理单元11412进行了图像处理的图像信号来使显示装置11202显示手术部位等的所拍摄的图像。此时,控制单元11413可以使用各种图像识别技术来识别所拍摄的图像内的各种物体。例如,控制单元11413可以通过检测包含在所拍摄的图像中的物体的边缘形状、颜色等来识别诸如钳子等手术器械、特定活体部位、出血、当使用能量处置器械11112时的雾等等。当使显示装置11202显示所拍摄的图像时,通过使用识别结果,控制单元11413可以将各种类型的手术支持信息重叠显示在手术部位的图像上。由于手术支持信息被叠加显示并呈现给手术者11131,所以可以减轻手术者11131的负担,并且手术者11131可以可靠地进行手术。

[0235]

将摄像头11102和ccu 11201连接在一起的传输线缆11400是兼容电气信号的通信的电气信号线缆、兼容光通信的光纤或其复合线缆。

[0236]

这里,在所示的示例中,通过使用传输线缆11400来执行有线通信,但是可以在摄像头11102和ccu 11201之间执行无线通信。

[0237]

《移动体的应用例》

[0238]

根据本公开的技术可以适用于各种产品。例如,根据本公开的技术被实现为安装在诸如汽车、电动汽车、混合电动汽车、摩托车、自行车、个人移动装置、飞机、无人飞行器、船舶和机器人等任何类型的移动体上的装置。

[0239]

图23是作为根据本公开的技术可以适用的移动体控制系统的示例的车辆控制系统的示意构成例的框图。

[0240]

车辆控制系统12000包括经由通信网络12001连接的多个电子控制单元。在图23所示的示例中,车辆控制系统12000包括驱动系统控制单元12010、主体系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040和综合控制单元12050。此外,作为综合控制单元12050的功能构成,示出了微型计算机12051、声音图像输出单元12052和车载网络接口(i/f)12053。

[0241]

驱动系统控制单元12010根据各种程序来控制与车辆的驱动系统有关的装置的操作。例如,驱动系统控制单元12010是产生如内燃机或驱动电机等车辆的驱动力的驱动力产生装置、向车轮传递驱动力的驱动力传递机构、调整车辆的转向角的转向机构、产生车辆的制动力的诸如制动装置等的控制装置。

[0242]

主体系统控制单元12020根据各种程序来控制安装到车体的各种装置的操作。例如,主体系统控制单元12020用作无钥匙进入系统、智能钥匙系统、电动窗装置或诸如头灯、尾灯、刹车灯、汽车用闪光灯或雾灯等各种灯的控制装置。在这种情况下,代替按键的从便携式装置传递的无线电波或各种开关的信号可以输入到主体系统控制单元12020。主体系统控制单元12020接收无线电波或信号的输入并控制车辆的门锁装置、电动窗装置、灯等。

[0243]

车外信息检测单元12030检测配备有车辆控制系统12000的车辆的外部的信息。例如,成像单元12031与车外信息检测单元12030连接。车外信息检测单元12030使成像单元12031拍摄车辆外部的图像并接收所拍摄的图像。车外信息检测单元12030可以基于接收到的图像进行诸如人、汽车、障碍物、标志、道路上的文字等物体检测处理或距离检测处理。

[0244]

成像单元12031是接收光并输出对应于该光的受光量的电气信号的光学传感器。成像单元12031可以输出电气信号作为图像或作为测距信息。另外,由成像单元12031接收的光可以是可见光或诸如红外线等不可见光。

[0245]

车内信息检测单元12040检测车内的信息。例如,车内信息检测单元12040与检测驾驶员的状态的驾驶员状态检测单元12041连接。例如,驾驶员状态检测单元12041包括拍摄驾驶员的相机,并且基于从驾驶员状态检测单元12041输入的检测信息,车内信息检测单元12040可以计算驾驶员的疲劳度或集中度,或者可以判断驾驶员是否入睡。

[0246]

微型计算机12051可以基于由车外信息检测单元12030或车内信息检测单元12040获得的车辆内部和外部的信息来计算驱动力产生装置、转向机构或制动装置的控制目标值,并且可以向驱动系统控制单元12010输出控制指令。例如,微型计算机12051可以进行协调控制,以实现包括车辆的碰撞避免或碰撞缓和、基于车辆之间的距离的追踪行驶、车辆速度保持行驶、车辆碰撞警告、车辆的车道偏离警告等的高级驾驶员辅助系统(adas)的功能。

[0247]

此外,微型计算机12051可以通过基于由车外信息检测单元12030或车内信息检测单元12040获得的关于车辆周围的信息来控制驱动力产生装置、转向机构、制动装置等来进行协调控制,以实现自主行驶而不依赖于驾驶员的操作的自动驾驶等。

[0248]

此外,微型计算机12051可以基于由车外信息检测单元12030获得的车辆外部的信息将控制指令输出到主体系统控制单元12030。例如,微型计算机12051根据由车外信息检测单元12030检测到的前方车辆或对向车辆的位置来控制头灯,进行协调控制,以实现诸如将远光灯切换为近光灯等防止眩光。

[0249]

声音图像输出单元12052将声音和图像中的至少一种的输出信号传递到能够在视觉上或听觉上通知车辆乘员或车辆外部的信息的输出装置。在图23的示例中,作为输出装置,例示了音频扬声器12061、显示单元12062和仪表板12063。例如,显示单元12062可以包括车载显示器和平视显示器中的至少一种。

[0250]

图24是示出了成像单元12031的安装位置的示例的图。

[0251]

在图24中,车辆12100具有成像单元12101,12102,12103,12104和12105作为成像单元12031。

[0252]

例如,成像单元12101,12102,12103,12104和12105设置在例如车辆12100的车头、侧视镜、后保险杠和后门以及车内的挡风玻璃的上侧等位置。设置在车头上的成像单元12101和设置在车内的挡风玻璃上侧的成像单元12105主要获得车辆12100的前方的图像。设置在侧视镜上的成像单元12102和12103主要获得车辆12100的侧方的图像。设置在后保险杠或后门上的成像单元12104主要获得车辆12100的后方的图像。成像单元12101和12105所获取的前方图像主要用于检测前方车辆、行人、障碍物、交通信号灯、交通标志、车道等。

[0253]

此外,图24示出了成像单元12101~12104的成像范围的示例。成像范围12111表示设置在车头上的成像单元12101的成像范围,成像范围12112和12113分别表示设置在侧视镜上的成像单元12102和12103的成像范围,成像范围12114表示设置在后保险杠或后门上的成像单元12104的成像范围。例如,通过叠加由成像单元12101~12104拍摄的图像数据,可以获得车辆12100的从上方看到的鸟瞰图像。

[0254]

成像单元12101~12104中的至少一个可以具有获取距离信息的功能。例如,成像单元12101~12104中的至少一个可以是包括多个成像元件的立体相机,或者可以是具有相位差检测用的像素的成像元件。

[0255]

例如,基于从成像单元12101~12104获得的距离信息,微型计算机12051通过获得距成像范围12111~12114内的各立体物的距离和距离的时间变化(相对于车辆12100的相对速度),可以提取位于车辆12100的行驶路线上的特别是最靠近的立体物,即,在与车辆12100的大致相同的方向上以预定速度(例如,0km/h以上)行驶的立体物作为前方车辆。此外,微型计算机12051可以设定在前方车辆的前方预先确保的车辆之间的距离,并且可以进行自动制动控制(包括追踪行驶停止控制)、自动加速控制(包括追踪行驶开始控制)等。以这种方式,能够进行用于实现自主行驶而不依赖于驾驶员的操作的自动驾驶等的协调控制。

[0256]

例如,基于从成像单元12101~12104获得的距离信息,微型计算机12051可以将关于立体物的立体物数据分类为两轮车辆、普通车辆、大型车辆、行人和诸如电线杆等其他立体物并提取,从而可以用于自动避开障碍物。例如,微型计算机12051将车辆12100周围的障碍物识别为车辆12100的驾驶员可以看到的障碍物和难以看到的障碍物。然后,微型计算机12051判断指示与各障碍物碰撞的危险度的碰撞风险,并且当存在碰撞风险超过设定值的碰撞的可能性时,微型计算机12051经由音频扬声器12061或显示单元12062向驾驶者输出警告或者通过驱动系统控制单元12010进行强制减速或回避转向,从而进行碰撞避免的驾驶辅助。

[0257]

成像单元12101~12104中的至少一个可以是用于检测红外线的红外相机。例如,微型计算机12051可以通过判断行人是否存在于成像单元12101~12104的成像图像中来识别行人。例如,通过提取作为红外相机的成像单元12101~12104的成像图像中的特征点的过程以及通过对指示物体的轮廓的一系列特征点进行图案匹配处理以判断该物体是否为行人的过程来进行行人的识别。当微型计算机12051判断行人存在于成像单元12101~12104的成像图像中并且识别出行人时,声音图像输出单元12052控制显示单元12062,使得识别出的行人被矩形轮廓线覆盖以用于强调。此外,声音图像输出单元12052可以使显示单元12062在期望的位置显示指示行人的图标等。

[0258]

此外,在本说明书中,系统表示包括多个装置的整个装置。

[0259]

注意,本说明书记载的效果仅是示例而非限制,并且还可以存在其他效果。

[0260]

注意,本技术的实施方案不限于上述实施方案,并且可以在不脱离本技术范围的情况下进行各种修改。

[0261]

注意,本技术还可以具有以下构成。

[0262]

(1)一种成像装置,包括:

[0263]

第一半导体元件,其包括被构造为生成像素信号的成像元件;和

[0264]

第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路,其中

[0265]

第一信号处理电路具有比第二信号处理电路多至少一层的结构。

[0266]

(2)根据上述(1)所述的成像装置,还包括:

[0267]

连接第一半导体元件和第一信号处理电路的第一配线。

[0268]

(3)根据上述(2)所述的成像装置,还包括:

[0269]

连接第一信号处理电路和第二信号处理电路的第二配线。

[0270]

(4)根据上述(3)所述的成像装置,其中

[0271]

第一配线连接第一半导体元件的端子和第一信号处理电路的第一端子,和

[0272]

第二配线连接第一信号处理电路的与第一端子不同的第二端子和第二信号处理电路的第三端子。

[0273]

(5)根据上述(1)~(4)中任一项所述的成像装置,其中

[0274]

所述层是氧化膜。

[0275]

(6)根据上述(1)~(5)中任一项所述的成像装置,其中

[0276]

第一半导体元件的端子与第一信号处理电路的端子之间的距离比第一半导体元件的端子与第二信号处理电路的端子之间的距离短。

[0277]

(7)根据上述(1)~(6)中任一项所述的成像装置,其中

[0278]

第一信号处理电路为存储电路,第二信号处理电路为逻辑电路。

[0279]

(8)一种包括成像装置的电子设备,所述成像装置包括:

[0280]

第一半导体元件,其包括被构造为生成像素信号的成像元件;和

[0281]

第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路,其中

[0282]

第一信号处理电路具有比第二信号处理电路多至少一层的结构。

[0283]

(9)一种成像装置,包括:

[0284]

第一半导体元件,其包括被构造为生成像素信号的成像元件;

[0285]

第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和

[0286]

连接第一信号处理电路和第二信号处理电路的配线,其中

[0287]

所述配线连接设置在第一信号处理电路的最下层的配线层中的端子和设置在第二信号处理电路的最下层的配线层中的端子。

[0288]

(10)根据上述(9)所述的成像装置,其中

[0289]

所述配线沿着第一信号处理电路的侧面和第二信号处理电路的侧面设置。

[0290]

(11)根据上述(10)所述的成像装置,其中

[0291]

所述配线的一部分沿着形成在第一半导体元件和第二半导体元件之间的接合面上的层设置。

[0292]

(12)根据上述(9)或(11)所述的成像装置,其中

[0293]

在所述配线和第一信号处理电路之间以及在所述配线和第二信号处理电路之间设置有至少一层或多层。

[0294]

(13)根据上述(12)所述的成像装置,其中

[0295]

所述的一层或多层是绝缘膜。

[0296]

(14)一种包括成像装置的电子设备,所述成像装置包括:

[0297]

第一半导体元件,其包括被构造为生成像素信号的成像元件;

[0298]

第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和

[0299]

连接第一信号处理电路和第二信号处理电路的配线,其中

[0300]

所述配线连接设置在第一信号处理电路的最下层的配线层中的端子和设置在第二信号处理电路的最下层的配线层中的端子。

[0301]

(15)一种成像装置的制造方法,所述成像装置包括:

[0302]

第一半导体元件,其包括被构造为以像素为单位生成像素信号的成像元件;

[0303]

第二半导体元件,在其中通过埋入构件埋入被构造为处理所述像素信号的第一信号处电路和第二信号处理电路;和

[0304]

连接第一信号处理电路和第二信号处理电路的配线,

[0305]

所述制造方法包括:

[0306]

将第一信号处理电路和第二信号处理电路转移到第一半导体元件上的步骤;

[0307]

在第一信号处理电路和第二信号处理电路上形成第一膜的步骤;

[0308]

将设置在第一信号处理电路的最下层的配线层中的第一端子的一部分和设置在第二信号处理电路的最下层的配线层中的第二端子的一部分露出的步骤;和

[0309]

形成连接第一端子和第二端子的配线的步骤。

[0310]

(16)根据上述(15)所述的制造方法,还包括:

[0311]

在形成第一膜之后,减薄第一信号处理电路和第二信号处理电路的步骤。

[0312]

附图标记列表

[0313]

101晶圆

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

102支撑基板

[0314]

103晶圆

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

104晶圆

[0315]

111成像装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

120成像元件

[0316]

121逻辑电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

122存储电路

[0317]

131片上滤色器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

132支撑基板

[0318]

133氧化膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

134配线

[0319]

135氧化膜接合层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

136配线

[0320]

137增厚层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

151切割带

[0321]

152环形框架

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

153切割带

[0322]

154环形框架

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

162支撑基板

[0323]

201配线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

204成像元件

[0324]

211成像装置

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

220成像元件

[0325]

221逻辑电路

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

222存储电路

[0326]

231片上滤色器

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

232支撑基板

[0327]

233氧化膜

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

234配线

[0328]

235氧化膜接合层

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

241保护膜

[0329]

242配线

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

252配线

[0330]

301抗蚀剂

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。