1.本发明属于静电防护技术领域,特别涉及一种应用于接口静电防护的装置、接口和设备。

背景技术:

2.静电放电在近年颇受重视,尤其是电子产品已进入纳米制程,体积越来越小,工作电压越来越低,以及体积重量越来越来轻薄。物质是由分子组成,分子是由原子组成,原子是构成一切化学元素的最小微粒,由带正电的原子核和带负电的围绕原子核旋转的电子组成。在正常状况下,原子所带的正负电荷相等,所以对外表现出电中性。但是在某种条件下,当物质原子中的这种电平衡状态被打破,丢失或获得电子,物质即由电中性状态改变为带电状态。丢失电子,则表现为带正电;获得电子,则表现为带负电。这种物体表面所带过剩或不足的相对静止不动电荷,称之为静电。静电放电(electrostatic discharge,esd)指为两个不同材质因表面接触时发生转移时,它们之间电荷会产生重新排序,此时会发生电子交换。静电放电防护电路是在集成电路中专门用来当静电放电防护之用,此静电放电防护电路提供了静电放电电流路径,以免静电放电时,静电电流流入集成电路的内部电路而造成损伤。为避免集成电路遭受静电放电的威胁与破坏,所有集成电路与外界接触的焊垫皆须搭配静电放电防护设计。在输出焊垫,其输出级大尺寸的晶体管本身便可当作静电放电防护组件来用,但是其布局必须遵守设计规则中有关静电放电布局方面的规定。在输入焊垫,因集成电路的输入端一般都是连接到晶体管的闸极,且由于闸极氧化层很容易被静电放电所打穿,因此在输入焊垫的下方或旁边会设计一组静电放电防护电路,以保护输入级的组件。在电源端与接地端的焊垫也要做静电放电防护设计,因为电源端与接地端的接脚也可能遭受静电放电的轰击。

3.在现有技术中,全芯片的静电防护电路连接如下图1所示。现在技术中采用通过增加金属平面加强静电能量宣泄路径,此做法只能针对gnd较少或gnd破碎不完整进行改善,无法对电源或信号受静电干扰进行改善。针对射频模块的静电放电保护组件造成射频模块效能将低,而提出一个小寄生电容保护组件,此建议只适用于射频模块,无法适用保护于差分信号。针对ic提出静电防护的设计考量,此设计考量针对ic组件受静电干扰时受损,在ic端提供更快保护,此做法在应用上可行,但无法取代保护于系统端实际应用上。所以针对传统式的静电防护设计电路以加大金属导体平面作屏蔽防护,利用接地平面的加大来做为静电能量的宣泄与隔绝敏感信号受静电干扰,此设计缺点有a.)无法保护电源线受静电放电干扰b.)无法保护信号线受静电放电干扰,由于电子产品的轻、薄、体积小,其静电放电之防护困难性与日俱增,尤其在常用之usb传输接口常发生与计算机连接时造成静电放电问题,而使计算机重新启动或宕机。

技术实现要素:

4.为了解决上述技术问题,本发明提出了一种应用于接口静电防护的装置、接口和

设备。用于实现usb接口的静电防护。

5.为实现上述目的,本发明采用以下技术方案:

6.一种应用于接口静电防护的装置,包括usb控制器、后端接口和静电防护模块;

7.所述静电防护模块位于所述usb控制器与所述后端接口之间,所述静电防护模块的一端与所述usb控制器连接、另一端与所述后端接口连接;

8.所述静电防护模块采用瞬时电压抑制阵列或者瞬时电压抑制二极管;所述瞬时电压抑制阵列由二极管与稳压二极管阵列排列为双向性组件,对正向和反向的电压均抑制,用于对所述usb控制器接口传输的静电电流进行泄放。

9.进一步的,所述瞬时电压抑制阵列包括两组二极管阵列和稳压二极管

10.所述二极管阵列由两路并联的支路组成,每个支路包括两个串联的二极管,且从每个支路两个串联二极管的中间引出瞬时电压抑制阵列的输入输出接口;所述稳压二极管的的阳极接地;阴极连接电源。

11.进一步的,所述瞬时电压抑制阵列的第一输入输出接口一路经过电阻连接至usb控制器的第四输出端,第二路连接至第二后端接口的电压负极引脚;

12.所述瞬时电压抑制阵列的第三输入输出接口一路经过电阻连接至usb控制器的第三输出端,第二路连接至第二后端接口的电压正极引脚;

13.所述瞬时电压抑制阵列的第四输入输出接口一路经过电阻连接至usb控制器的第二输出端,第二路连接至第一后端接口的电压负极引脚;

14.所述瞬时电压抑制阵列的第六输入输出接口一路经过电阻连接至usb控制器的第一输出端,第二路连接至第一后端接口的电压正极引脚;

15.且第一输出端和第四输出端之间连接两个极性电容;第二输出端和第三输出端之间连接两个极性电容。

16.进一步的,瞬时电压抑制阵列的电源接口还连接至usb控制器的v

bus

,且usb控制器v

bus

还与后端接口的v

bus

连接。

17.进一步的,第一输出端通过第一极性电容之后,一路接地,另外一路通过第二极性电容连接第四输出端;第二输出端通过第三极性电容之后,一路接地,另外一路通过第四极性电容连接第三输出端。

18.进一步的,所述极性电容的结构包括第一金属导体、第二金属导体和介电材料;

19.所述介电材料由介电材料薄片叠放组成,且介电材料薄片偶数层导体电极连接至第一金属导体;介电材料薄片奇数层导体电极连接至第二金属导体。

20.进一步的,所述电阻采用压敏电阻;

21.在所述压敏电阻两端的电压小于压敏电阻的崩溃电压时,压敏电阻为高阻抗低电流;在所述压敏电阻两端的电压大于压敏电阻的崩溃电压时,压敏电阻转变成低阻抗以抑制瞬时电压或者突变电压。

22.进一步的,所述瞬时电压抑制二极管由两个稳压二极管背对背连接组成双向性组件;

23.所述瞬时电压抑制二极管的一端连接usb控制器,另外一端连接后端接口。

24.本发明还提出了一种usb接口,所述usb接口包含一种应用于接口静电防护的装置。

25.本发明还提出了一种usb设备,所述usb设备包含一种usb接口。

26.发明内容中提供的效果仅仅是实施例的效果,而不是发明所有的全部效果,上述技术方案中的一个技术方案具有如下优点或有益效果:

27.本发明提出了一种应用于接口静电防护的装置、接口和设备,该装置包括usb控制器、后端接口和静电防护模块;静电防护模块位于usb控制器与所述后端接口之间,静电防护模块的一端与所述usb控制器连接、另一端与所述后端接口连接;静电防护模块采用瞬时电压抑制阵列或者瞬时电压抑制二极管;瞬时电压抑制阵列由二极管与稳压二极管阵列排列为双向性组件,对正向和反向的电压均抑制,用于对usb控制器接口传输的静电电流进行泄放。基于一种应用于接口静电防护的装置,本发明还提出了一种usb接口和一种usb设备。本发明采用瞬时电压抑制阵列或者瞬时电压抑制二极管对usb接口进行静电防护。透过主板南桥芯片观察静电放电干扰,分别在usb电源、信号线d 、信号线d-、gnd以及shield pin受静电放电干扰时,南桥芯片所记录静电放电量测结果,本发明提出一种应用于接口静电防护的装置能抑制与原始状态40%瞬时电压干扰。本发明适用于所有usb传输接口以及设置usb接口的设备,具有很好的通用性。

附图说明

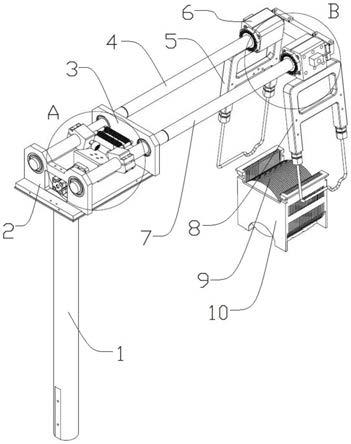

28.如图1为本发明实施例1一种应用于接口静电防护的装置连接示意图;

29.如图2为本发明实施例1中瞬时电压抑制阵列电路连接示意图;

30.如图3为本发明实施例1中瞬时电压抑制二极管的等效电路图;

31.如图4为采用本发明实施例1一种应用于接口静电防护的装置usb电源pin的防护波形图;

32.如图5为采用本发明实施例1一种应用于接口静电防护的装置usb_d pin的防护波形图;

33.如图6为采用本发明实施例1一种应用于接口静电防护的装置usb_d-pin的防护波形图;

34.如图7为采用本发明实施例1一种应用于接口静电防护的装置gnd pin的防护波形图;

35.如图8为采用本发明实施例1一种应用于接口静电防护的装置shield pin的防护波形图。

具体实施方式

36.为能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本发明进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本发明的不同结构。为了简化本发明的公开,下文中对特定例子的部件和设置进行描述。此外,本发明可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本发明省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本发明。

37.实施例1

38.本发明实施例1提出了一种应用于接口静电防护的装置,用于usb接口的静电防

护,如图1给出了本发明实施例1一种应用于接口静电防护的装置连接示意图,该装置包括usb控制器、后端接口和静电防护模块;

39.静电防护模块位于usb控制器与所述后端接口之间,静电防护模块的一端与所述usb控制器连接、另一端与所述后端接口连接;

40.静电防护模块采用瞬时电压抑制阵列或者瞬时电压抑制二极管;瞬时电压抑制阵列由二极管与稳压二极管阵列排列为双向性组件,对正向和反向的电压均抑制,用于对所述usb控制器接口传输的静电电流进行泄放。

41.如图2为本发明实施例1中瞬时电压抑制阵列电路连接示意图;瞬时电压抑制阵列(transient voltage suppression array,tvs array)之电电路图,其设计电路是将以二极管与稳压二极管作阵列阵列,可作为多组i/o接口共同使用。其组件寄生电容因稳压二极管共同串联而变小,更好的适用于高频、高速的电路。由图可知此种为双向性之半导体制程组件,对于正向以及反向之瞬时电压皆有抑制效果。

42.瞬时电压抑制阵列包括两组二极管阵列和稳压二极管。

43.二极管阵列由两路并联的支路组成,每个支路包括两个串联的二极管,且从每个支路两个串联二极管的中间引出瞬时电压抑制阵列的输入输出接口;所述稳压二极管的的阳极接地;阴极连接电源。

44.瞬时电压抑制阵列的第一输入输出接口一路经过电阻连接至usb控制器的第四输出端,第二路连接至第二后端接口的电压负极d-引脚;

45.瞬时电压抑制阵列的第三输入输出接口一路经过电阻连接至usb控制器的第三输出端,第二路连接至第二后端接口的电压正极d 引脚;

46.瞬时电压抑制阵列的第四输入输出接口一路经过电阻连接至usb控制器的第二输出端,第二路连接至第一后端接口的电压负极d-引脚;

47.瞬时电压抑制阵列的第六输入输出接口一路经过电阻连接至usb控制器的第一输出端,第二路连接至第一后端接口的电压正极d 引脚;

48.且第一输出端和第四输出端之间连接两个极性电容;第二输出端和第三输出端之间连接两个极性电容。

49.瞬时电压抑制阵列的电源接口还连接至usb控制器的v

bus

,且usb控制器v

bus

还与后端接口的v

bus

连接。

50.第一输出端通过第一极性电容之后,一路接地,另外一路通过第二极性电容连接第四输出端;第二输出端通过第三极性电容之后,一路接地,另外一路通过第四极性电容连接第三输出端。

51.本发明实施例1中给出的示意图中瞬时电压抑制阵列可同时保护两组i/o接口。本发明保护的范围不局限于实施例1中列举出的结构。

52.本发明中,极性电容的结构包括第一金属导体、第二金属导体和介电材料;介电材料由介电材料薄片叠放组成,且介电材料薄片偶数层导体电极连接至第一金属导体;介电材料薄片奇数层导体电极连接至第二金属导体。因此可将其视为由好几个小电容并联成一个大电容,这种smt之电容,轻、薄、短、小,为具有双向性之组件。

53.电阻采用压敏电阻,在压敏电阻两端的电压小于压敏电阻的崩溃电压时,压敏电阻为高阻抗低电流;在所述压敏电阻两端的电压大于压敏电阻的崩溃电压时,压敏电阻转

变成低阻抗以抑制瞬时电压或者突变电压。

54.压敏电阻其结构累死电容,一般在两导体间夹着zno氧化锌为主之材料。在压敏电阻两端电压低于工作电压规格时,组件为off状态,呈现高阻抗且漏电流的状态,此时呈现与一般电容器组件相同之性质,如图。当压敏电阻两端电压高于组件崩溃电压(breakdown voltage)时,组件进入on的动作状态,转变成以低阻抗来抑制瞬时或突波电压,并吸收大部分异常电流,呈现与一般低电阻值电阻器组件相同性质。

55.本发明中静电防护模块还可以采用瞬时电压抑制二极管,如图3为本发明实施例1中瞬时电压抑制二极管的等效电路图;其中瞬时电压抑制二极管(transient voltage suppression diode,tvs diode)的等效电路图,其设计为半导体制程,主要是将两个稳压二极管背对背相接,所以为双向性组件。tvs diode工作类似于稳压二极管,利用半导体硅si、锗ge浓度加大半导体中pn接合的面积,而使tvs具有更强的高压承受能力,同时也降低了电压截止率,因而对于保护低工作电压设备具有更好效果。tvs具有极快的响应时间(ns)可用于保护设备或电路免受静电、电感性负载切换时产生的瞬时电压。

56.如图4为采用本发明实施例1一种应用于接口静电防护的装置usb电源pin的防护波形图;如图5为采用本发明实施例1一种应用于接口静电防护的装置usb_d pin的防护波形图;如图6为采用本发明实施例1一种应用于接口静电防护的装置usb_d-pin的防护波形图;如图7为采用本发明实施例1一种应用于接口静电防护的装置gnd pin的防护波形图;如图8为采用本发明实施例1一种应用于接口静电防护的装置shield pin的防护波形图,透过主板南桥芯片观察静电放电干扰,分别在usb电源、信号线d 、信号线d-、gnd以及shield pin受静电放电干扰时,南桥芯片所记录静电放电量测结果,本发明提出一种应用于接口静电防护的装置能抑制与原始状态40%瞬时电压干扰。

57.实施例2

58.基于本发明实施例1提出的一种应用于接口静电防护的装置,本发明还提出了一种usb接口,usb接口包含一种应用于接口静电防护的装置。

59.基于本发明实施例1提出的一种应用于接口静电防护的装置,本发明还提出了一种usb设备,usb设备包含一种usb接口。

60.同样具有一种应用于接口静电防护的装置的作用。

61.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。另外,本技术实施例提供的上述技术方案中与现有技术中对应技术方案实现原理一致的部分并未详细说明,以免过多赘述。

62.上述虽然结合附图对本发明的具体实施方式进行了描述,但并非对本发明保护范围的限制。对于所属领域的技术人员来说,在上述说明的基础上还可以做出其它不同形式的修改或变形。这里无需也无法对所有的实施方式予以穷举。在本发明的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本发明的保护范围以内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。