一种基于dsp-fpga的多通道ad采集系统

技术领域

1.本发明涉及通用扩展接口控制系统技术领域,具体涉及一种基于dsp-fpga的多通道ad采集系统。

背景技术:

2.传统技术的基本情况:adc包括三个基本功能:抽样、量化和编码。抽样过程是将模拟信号在时间上离散化,使之成为抽样信号;量化是将抽样信号的幅度离散化使之成为数字信号;而编码则是将数字信号转换成数字系统所能接受的形式。我们知道,从硬件架构上来讲数据采集卡一般分为两类。第一类是同步采集卡,也就是采集卡的每一个通道都有一个单独的adc(模数转换器)和放大器,这样的采集卡适合对信号时序很严格的场合,通道间的同步精度一般会在几个纳秒的级别,但是板卡本身的价格也会比较高。另一种是非同步采集卡(也可以叫做多路复用的采集卡),全部通道共享一个adc和放大器,这种采集卡适合对通道间时序没有那么严格的场合,通道间的相位差会在十几个微秒级别。

3.传统的adc采样系统具有以下不足:

4.1)同步采样通道数不足:传统的adc板卡中,由于主控芯片外设接口有限,一般仅有8~32的模数转化通道;

5.2)数据转换能力不足:为降低系统功耗,传统的控制系统主要是采用fpga(现场可编程门阵列) mcu(微控制器)方案,fpga主要负责对接收换能器调理后的模拟阵元域信号进行模数转换,再将转换后的数字信号传输给mcu来进行处理、存储,由于mcu信号处理能力较弱,数据转换能力不足。

6.3)多板卡同步控制较差:传统的采集板卡,当多板卡级联时,由于时钟传输的延时,在工作信号频率较高的情况下,相位一致性较差。

7.4)板卡没有预处理功能:传统的采集板卡,功能较为单一,只能把原始数据打包后上传至上级系统,无预处理能力。

技术实现要素:

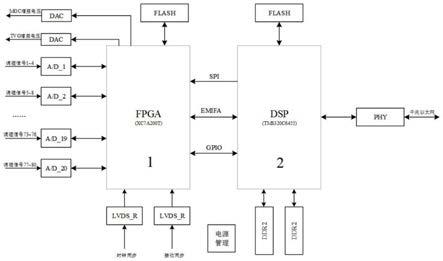

8.针对现有技术的不足,本发明提供了一种基于dsp-fpga的多通道ad采集系统,采用通用化的硬件结构,使用高性能dsp(tms320c6455)、高密度fpga(xc7a200t)为核心,由多片模数转换芯片、ddr2、flash、phy及电源管理等组成外围电路。

9.本发明通过以下技术方案予以实现:

10.一种基于dsp-fpga的多通道ad采集系统,包括采集传输板;所述采集传输板包括:

11.fpga模块:主要完成对20片模数转换芯片ltc进行控制、读取,将ltc输出信号分布式存储到存储器recv_ram1~recv_ram5中,进而通过多个16通道ddc完成下变频处理,将阵元回波信号变换为基带i/q路数字信号,并存入ri_ram中;通过fifo半满标志位通知dsp读取fpga端数据至ddr2中;

12.dsp模块:主要实现接收网络控制命令并处理、控制fpga端状态机切换、接收来自

fpga端数据包以及通过网络上行发送数据。

13.优选的,所述fpga模块和所述dsp模块之间还包括用于通信传输的spi、emifa和gpio通信接口。

14.优选的,还包括接收电源同步板,所述接收电源同步板上还包括两类同步信号:时钟同步信号和接收同步信号,均采用lvds_r双绞线传输方式传输至所述采集传输板上。

15.优选的,该同步信号的接收采用snsn65lvds4接收器实现,该接收器最高速率可达500mbps,典型传输延迟2.1ns;

16.所述接收同步信号的最大频率小于10hz,所述时钟同步信号的频率为50mhz。

17.优选的,所述dsp模块上还包括设置的外围电路,所述外围电路包括flash芯片、phy芯片和ddr2芯片;所述dsp模块和所述外围电路完成对下行网络命令的解析,进而对所述fpga模块端进行状态控制,读取80通道模数转换后的数字信号,并按udp协议将数据上传。

18.优选的,还包括千兆以太网模块emac/mdio,负责以太网数据的接收和发送。

19.优选的,所述emac模块体提供mii、rmii、gmii和rgmii接口,能够与符合ieee802.3标准的片外所述phy芯片无缝连接;

20.所述mdio模块负责管理与emac相连的所有所述phy芯片,包括对所述phy芯片进行枚举、配置和器件状态进行检测。

21.优选的,所述emac/mdio模块的配置、运行操作均是通过控制其内部寄存器组来实现的;

22.此外,所述emac模块内部有两块8k大小的缓冲区,分别用来存放待发送和接收以太网数据包的描述信息。

23.优选的,所述采集传输板中的dsp模块接收下行的命令后将之解析,通过spi串行接口转发至fpga模块,以控制所述fpga模块状态机的运行;同时,所述fpga模块采集20片ltc同步输出的数字信号并按数据协议进行封装,通过emifa并行数据总线传送至所述dsp模块,所述dsp模块与所述fpga模块命令/数据交互的过程使用gpio通信接口作为中断或标志位。

24.本发明的有益效果为:

25.1)搭载的模数转换芯片将输入的80路调理信号转换为数字,最高支持5m采样率。

26.2)1000m以太网数据输出,系统最大数据吞吐率不小于400mbps。

27.3)可多板卡级联并行工作,软件控制主从,板件相位差小于6

°

。

28.4)板卡有预处理功能,通过fpga、dsp的软件编程,实现波束形成,数字滤波、脉冲压缩等信号处理功能。实现了数据压缩,减轻了上级系统处理负担。

附图说明

29.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

30.图1是本发明的整体电路功能框图;

31.图2是本发明中采集传输板原理框图;

32.图3是本发明中同步信号传输示意图;

33.图4是本发明中lvds接收器特性图;

34.图5是本发明中dsp组成框图;

35.图6是本发明中dsp/phy连接示意图;

36.图7是本发明中dsp软件多线程流转示意图;

37.图8是本发明中fpga软件功能框图。

38.图中:1-fpga模块、2-dsp模块。

具体实施方式

39.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

40.实施例一:

41.请参阅图1~8所示,本实施例具体公开提供了一种基于dsp-fpga的多通道ad采集系统的技术方案,包括采集传输板;所述采集传输板包括:

42.fpga模块1:主要完成对20片模数转换芯片ltc进行控制、读取,将ltc输出信号分布式存储到存储器recv_ram1~recv_ram5中,进而通过多个16通道ddc完成下变频处理,将阵元回波信号变换为基带i/q路数字信号,并存入ri_ram中;通过fifo半满标志位通知dsp读取fpga端数据至ddr2中;

43.dsp模块2:主要实现接收网络控制命令并处理、控制fpga端状态机切换、接收来自fpga端数据包以及通过网络上行发送数据。

44.具体的,所述fpga模块1和所述dsp模块2之间还包括用于通信传输的spi、emifa和gpio通信接口。

45.具体的,还包括接收电源同步板,所述接收电源同步板上还包括两类同步信号:时钟同步信号和接收同步信号,均采用lvds_r双绞线传输方式传输至所述采集传输板上。

46.具体的,该同步信号的接收采用snsn65lvds4接收器实现,该接收器最高速率可达500mbps,典型传输延迟2.1ns;

47.所述接收同步信号的最大频率小于10hz,所述时钟同步信号的频率为50mhz。

48.具体的,所述dsp模块2上还包括设置的外围电路,所述外围电路包括flash芯片、phy芯片和ddr2芯片;所述dsp模块2和所述外围电路完成对下行网络命令的解析,进而对所述fpga模块1端进行状态控制,读取80通道模数转换后的数字信号,并按udp协议将数据上传。

49.具体的,还包括千兆以太网模块emac/mdio,负责以太网数据的接收和发送。

50.具体的,所述emac模块体提供mii、rmii、gmii和rgmii接口,能够与符合ieee802.3标准的片外所述phy芯片无缝连接;

51.所述mdio模块负责管理与emac相连的所有所述phy芯片,包括对所述phy芯片进行枚举、配置和器件状态进行检测。

52.具体的,所述emac/mdio模块的配置、运行操作均是通过控制其内部寄存器组来实现的;

53.此外,所述emac模块内部有两块8k大小的缓冲区,分别用来存放待发送和接收以太网数据包的描述信息。

54.具体的,所述采集传输板中的dsp模块2接收下行的命令后将之解析,通过spi串行接口转发至fpga模块1,以控制所述fpga模块1状态机的运行;同时,所述fpga模块1采集20片ltc同步输出的数字信号并按数据协议进行封装,通过emifa并行数据总线传送至所述dsp模块2,所述dsp模块2与所述fpga模块1命令/数据交互的过程使用gpio通信接口作为中断或标志位。

55.本发明实施例还包括如下内容:

56.a、fpga/dsp接口设计:下表1fpga/dsp通信接口定义表:

[0057][0058]

b、同步设计:

[0059]

采集传输板接收来自接收电源同步板两类同步信号:时钟同步、接收同步,示意如图3所示。由于两板之间的距离最远可达约1m,为了有效、可靠的传输同步信号,采用lvds双绞线传输方式。

[0060]

同步信号的接收采用snsn65lvds4实现,该接收器最高速率可达500mbps,典型传输延迟2.1ns,接收器的特性如图4所示。接收同步信号最大频率小于10hz,时钟同步信号频率为50mhz,该芯片可满足传输率要求。

[0061]

c、dsp硬件设计:

[0062]

dsp及外围电路完成对下行网络命令的解析,进而对fpga端进行状态控制,读取80通道模数转换后的数字信号,并按udp协议将数据上传,其外围电路如图5所示。

[0063]

d、千兆以太网设计:

[0064]

千兆以太网模块emac/mdio是dsp内核与片外的网络物理层数据传输的接口,负责以太网数据的接收和发送,实现了ieee802.3标准的以太网mac层协议功能。emac模块体提供mii、rmii、gmii和rgmii接口,能够与符合ieee802.3标准的片外phy芯片无缝连接。mdio模块负责管理与emac相连的所有phy芯片,包括对phy芯片进行枚举、配置和器件状态检测等。

[0065]

emac/mdio模块的配置、运行等操作都是通过控制其内部寄存器组来实现的。此外,emac模块内部有两块8k大小的缓冲区,分别用来存放待发送和接收以太网数据包的描述信息,如数据包长度,存放位置等。因此,借助与这些数据包描述信息和片内直接存储edma控制器,emac/mdio可以在不中断cpu的情况下直接访问存储区的数据,相对独立的工作,从而满足不小于246mbps的设计指标。

[0066]

图6为基于dsp的emac/mdio模块、片外phy芯片(88e1111)及其他外围电路连接示意。

[0067]

e、软件设计:

[0068]

dsp所采用dsp/bios嵌入式操作系统提供了抢占式多线程调度、硬件抽象、实时分析和配置工具,并具有良好实时性的软件运行环境。dsp软件主要实现功能包括:接收网络控制命令并处理;控制fpga端状态机切换;接收来自fpga端数据包;通过网络上行发送数据等。多线程流转如图7所示。

[0069]

fpga软件主要完成对20片模数转换芯片ltc进行控制、读取,将ltc输出信号分布式存储到存储器recv_ram1~recv_ram5中,进而通过多个16通道ddc完成下变频处理,将阵元回波信号变换为基带i/q路数字信号,并存入ri_ram中。通过fifo半满等标志位通知dsp读取fpga端数据至ddr2中图8软件功能框图。

[0070]

f、工作原理:

[0071]

采集传输板中dsp接收下行的命令后将之解析,通过spi串行接口转发至fpga,以控制fpga状态机的运行。同时,fpga采集20片ltc同步输出的数字信号并按数据协议进行封装,通过emifa并行数据总线传送至dsp,dsp与fpga命令/数据交互的过程使用gpio作为中断或标志位。

[0072]

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。