技术特征:

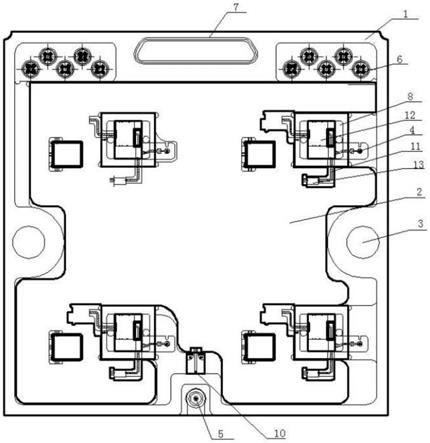

1.一种具有氮化镓结构的电阻晶体管逻辑电路,其特征在于,包含:氮化镓层,具有高压元件区、低压元件区以及电阻区;氮化铝镓阻障层,位于该氮化镓层上;多条p型掺杂氮化镓覆盖层,位于该氮化铝镓阻障层上,其中在该高压元件区与该低压元件区中部分的该些p型掺杂氮化镓覆盖层使得其下方的该氮化镓层变为栅极空乏区,该电阻区中未被该些p型掺杂氮化镓覆盖层所覆盖的该氮化镓层作为二维电子气(2deg)电阻器;多个第一栅极,每个该第一栅极形成在该高压元件区中的一条该p型掺杂氮化镓覆盖层上;多个第一源极与多个第一漏极,形成在该高压元件区中的该氮化镓层上,其中该些第一栅极、该些第一源极以及该些第一漏极构成高压高电子移动率晶体管;多个第二栅极,每个该第二栅极形成在该低压元件区中的一条该p型掺杂氮化镓覆盖层上;以及多个第二源极与多个第二漏极,形成在该低压元件区中的该氮化镓层上,其中该些第二栅极、该些第二源极以及该些第二漏极构成低压逻辑场效晶体管。2.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该低压逻辑场效晶体管的该第二栅极到该第二源极的距离与该第二栅极到该第二漏极的距离相同。3.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该高压高电子移动率晶体管的该第一栅极到该第一漏极的距离大于该第一栅极到该第一源极的距离。4.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该些p型掺杂氮化镓覆盖层在该电阻区中的该氮化镓层上错位排列,使得未被该些p型掺杂氮化镓覆盖层所覆盖的该氮化镓层形成该二维电子气电阻器的绕线图案。5.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该氮化镓层包含下方的氮化镓外延层与上方的氮化镓平台层,该氮化铝镓阻障层位于该氮化镓平台层上。6.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,还包含第三源极与第三漏极形成在该电阻区中的该二维电子气电阻器上。7.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,还包含钝化层位于该氮化镓层与该些p型掺杂氮化镓覆盖层上并裸露出该些第一栅极、该些第一源极、该些第一漏极、该些第二栅极、该些第二源极以及该些第二漏极。8.如权利要求7所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该些第一栅极、该些第一源极、该些第一漏极、该些第二栅极、该些第二源极以及该些第二漏极还具有场板部位位于该钝化层上。9.如权利要求7所述的具有氮化镓结构的电阻晶体管逻辑电路,还包含场板结构位于该高压元件区中该些第二漏极与该些第二栅极之间的该钝化层上。10.如权利要求9所述的具有氮化镓结构的电阻晶体管逻辑电路,其中该场板结构与该场板部位相连接。11.如权利要求1所述的具有氮化镓结构的电阻晶体管逻辑电路,还包含多层金属层位于该高压元件区中的该些高压高电子移动率晶体管上方,其中部分的该些金属层构成了金属互连电阻器。

12.一种具有氮化镓结构的电阻器,其特征在于,包含:氮化镓层,其具有二维电子气电阻区与未掺杂多晶硅电阻区;氮化铝镓阻障层,位于该二维电子气电阻区中的该氮化镓层上;多条p型掺杂氮化镓覆盖层,排列在该氮化铝镓阻障层上,使得该二维电子气电阻区中未被该些p型掺杂氮化镓覆盖层所覆盖的该氮化镓层变为二维电子气电阻器;钝化层,位于该氮化镓层上;以及未掺杂多晶硅层,位于该未掺杂多晶硅电阻区中的该钝化层上并构成未掺杂多晶硅电阻器。13.如权利要求12所述的具有氮化镓结构的电阻器,其中该氮化镓层包含下方的氮化镓外延层与上方的氮化镓平台层,该氮化铝镓阻障层位于该氮化镓平台层上。14.如权利要求11所述的具有氮化镓结构的电阻器,其中该些p型掺杂氮化镓覆盖层在该二维电子气电阻区中的该氮化镓层上错位排列,使得未被该些p型掺杂氮化镓覆盖层所覆盖的该氮化镓层形成该二维电子气电阻器的绕线图案。15.如权利要求11所述的具有氮化镓结构的电阻器,其中该未掺杂多晶硅层在该钝化层上呈绕线图案。16.如权利要求11所述的具有氮化镓结构的电阻器,还包含第一源极与第一漏极形成在该二维电子气电阻器上。17.如权利要求11所述的具有氮化镓结构的电阻器,其中该氮化镓层还包含掺杂多晶硅电阻区,该掺杂多晶硅电阻区中的该钝化层上具有掺杂多晶硅层,该掺杂多晶硅层构成掺杂多晶硅电阻器。18.如权利要求17所述的具有氮化镓结构的电阻器,其中该掺杂多晶硅层在该钝化层上呈绕线图案。19.一种具有氮化镓结构的电阻晶体管逻辑电路的制作方法,包含:提供基底,其具有高压元件区、低压元件区以及电阻区;在该基底上依序形成氮化镓层、氮化铝镓阻障层与p型掺杂氮化镓覆盖层;图案化该p型掺杂氮化镓覆盖层形成多条p型掺杂氮化镓覆盖图案,其中在该高压元件区与该低压元件区中部分的该些p型掺杂氮化镓覆盖图案下方的该氮化镓层变为栅极空乏区,该电阻区中未被该些p型掺杂氮化镓覆盖图案覆盖的该氮化镓层作为二维电子气(2deg)电阻器;在该氮化镓层与该些p型掺杂氮化镓覆盖图案上形成钝化层;在该钝化层中的该氮化镓层上形成多个源极与多个漏极;在该钝化层中的该些p型掺杂氮化镓覆盖图案上形成多个栅极,其中该高压元件区中的该些栅极、该些源极以及该些漏极构成高压高电子移动率晶体管,该低压元件区中的该些栅极、该些源极以及该些漏极构成低压逻辑场效晶体管。20.如权利要求19所述的具有氮化镓结构的电阻晶体管逻辑电路的制作方法,还包含在形成该p型掺杂氮化镓覆盖层前对该氮化镓层进行平台蚀刻界定出氮化镓平台隔离区,该氮化铝镓阻障层位于该氮化镓平台隔离区上。21.如权利要求19所述的具有氮化镓结构的电阻晶体管逻辑电路的制作方法,还包含在该钝化层上形成图案化的未掺杂多晶硅层作为未掺杂多晶硅电阻器。

22.如权利要求19所述的具有氮化镓结构的电阻晶体管逻辑电路的制作方法,还包含在该钝化层上形成图案化的掺杂多晶硅层作为掺杂多晶硅电阻器。23.如权利要求19所述的具有氮化镓结构的电阻晶体管逻辑电路的制作方法,其中在形成该些栅极的步骤中同时形成位于该钝化层上的场板结构。24.如权利要求19所述的具有氮化镓结构的电阻晶体管逻辑电路的制作方法,其中在形成该些源极与该些漏极的步骤中同时形成位于该钝化层上的场板结构。

技术总结

本发明公开一种具有氮化镓结构的电阻器、电阻晶体管逻辑电路及其制法,电阻晶体管逻辑电路包含氮化镓层;氮化铝镓阻障层位于该氮化镓层上;多条p型掺杂氮化镓覆盖层位于氮化铝镓阻障层上,高、低压元件区中部分p型掺杂氮化镓覆盖层使得其下方的氮化镓层变为栅极空乏区,电阻区中未被p型掺杂氮化镓覆盖层覆盖的氮化镓层作为二维电子气电阻器;多个第一栅极,其中每个形成在高压元件区中的一条p型掺杂氮化镓覆盖层上;多个第一源极与多个第一漏极,形成在高压元件区中的氮化镓层上;多个第二栅极,其中每个形成在低压元件区中的一条p型掺杂氮化镓覆盖层上;多个第二源极与多个第二漏极,形成在低压元件区中的该氮化镓层上。形成在低压元件区中的该氮化镓层上。形成在低压元件区中的该氮化镓层上。

技术研发人员:李国兴 薛胜元 吴建良 叶德炜 陈怡君

受保护的技术使用者:联华电子股份有限公司

技术研发日:2020.09.21

技术公布日:2022/3/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。