1.本发明涉及一种半导体制造,且特别是涉及高电压晶体管结构及其制造方法。

背景技术:

2.随着电子产品的多样功能,其控制电路需要能同时驱动操作在高电压的高电压组件以及操作在低电压组件。因应高电压组件以及低电压组件的操作,其中例如电源模块需要能提供高电压电源以及低电压电源。高电压电路在电源模块的控制中扮演重要的角色。也就是说,为了增加更多的驱动能力,整体的集成电路会包含高电压晶体管来驱动不同的动作。

3.高电压晶体管是在相对高电压下操作,电压晶体管的击穿电压的高低是决定其质量的一个重要因素。具有较高击穿电压的高电压晶体管可以相对较长时间承受高电压操作而不产生击穿,进而也以维持产品的寿命。

4.为了提升高电压晶体管的击穿电压,除了增加栅极绝缘层的厚度外,其当作源极与漏极的掺杂结构也会调整,使晶体管的通道(channel)能够在高电压下正常稳定操作。

5.源极与漏极的掺杂结构的设计会影响高电压晶体管的击穿电压,因此如何设计高电压晶体管的源极与漏极的掺杂结构仍在继续研发中。

技术实现要素:

6.本发明提供高电压晶体管的结构及其制造方法,其源极与漏极的掺杂结构可以有效提升击穿电压也可以维持大的操作电流。

7.在一实施例,本发明提供一种高电压晶体管结构,其包括基板。第一导电型的外延掺杂结构形成在所述基板中。所述外延掺杂结构的顶部包含未掺杂外延顶层。栅极结构设置在所述基板上,且至少重叠于所述未掺杂外延顶层。第二导电型的源/漏极区域形成在所述外延掺杂结构中,在所述栅极结构侧边。所述第一导电型不同于所述第二导电型。

8.在一实施例,对于所述的高电压晶体管结构,所述外延掺杂结构包含多个掺杂外延层在所述未掺杂外延顶层下方,且所述第一导电型的掺杂浓度是往下递减。

9.在一实施例,对于所述的高电压晶体管结构,所述外延掺杂结构包含未掺杂外延底层,介接于所述基板。

10.在一实施例,对于所述的高电压晶体管结构,所述基板是硅基板,所述外延掺杂结构包括多个硅外延层。硅外延顶层是所述未掺杂外延顶层,硅外延底层是未掺杂外延底层,所述多个硅外延层的一部分在所述未掺杂外延顶层与所述未掺杂外延底层之间,是所述掺杂外延层。

11.在一实施例,对于所述的高电压晶体管结构,所述第一导电层是n导电型或是p导电型,且所述多个掺杂外延层是分别对应掺杂n导电型掺质或是p导电型掺质。

12.在一实施例,对于所述的高电压晶体管结构,所述多个掺杂外延层包括n导电型的sip或是p导电型的sige。

13.在一实施例,对于所述的高电压晶体管结构,所述栅极结构包括高电压栅极绝缘层,设置在所述基板上。栅极层设置在所述高电压栅极绝缘层上。间隙壁设置在所述基板上,且在所述栅极层的侧壁上。所述未掺杂外延顶层是在所述间隙壁下,且延伸到所述高电压栅极绝缘层的下面。

14.在一实施例,本发明也提供一种制造高电压晶体管的方法,包括提供基板。制造方法还包括形成凹陷在所述基板中。形成第一导电型的外延掺杂结构,在所述基板的所述凹陷中,其中所述外延掺杂结构的顶部包含未掺杂外延顶层。形成栅极结构在所述基板上,且至少重叠于所述未掺杂外延顶层。形成第二导电型的源/漏极区域在所述外延掺杂结构中,在所述栅极结构侧边。所述第一导电型不同于所述第二导电型。

15.在一实施例,对于所述制造高电压晶体管的方法,所形成的所述外延掺杂结构包含多个掺杂外延层在所述未掺杂外延顶层下方,且所述第一导电型的掺杂浓度是往下递减。

16.在一实施例,对于所述制造高电压晶体管的方法,所形成的所述外延掺杂结构包含未掺杂外延底层,介接于所述基板。

17.在一实施例,对于所述制造高电压晶体管的方法,所提供的所述基板是硅基板,所形成的所述外延掺杂结构包括多个硅外延层。硅外延顶层是所述未掺杂外延顶层,硅外延底层是未掺杂外延底层,所述多个硅外延层的一部分在所述未掺杂外延顶层与所述未掺杂外延底层之间,是所述掺杂外延层。

18.在一实施例,对于所述制造高电压晶体管的方法,所述第一导电层是n导电型或是p导电型,且所述多个掺杂外延层是分别对应掺杂n导电型掺质或是p导电型掺质。

19.在一实施例,对于所述制造高电压晶体管的方法,所述多个掺杂外延层包括n导电型的sip或是p导电型的sige。

20.在一实施例,对于所述制造高电压晶体管的方法,所形成的所述栅极结构包括高电压栅极绝缘层,设置在所述基板上。栅极层设置在所述高电压栅极绝缘层上。间隙壁设置在所述基板上,且在所述栅极层的侧壁上。所述未掺杂外延顶层是在所述间隙壁下,且延伸到所述高电压栅极绝缘层的下面。

21.在一实施例,对于所述制造高电压晶体管的方法,于形成所述外延掺杂结构的所述步骤包括原位掺杂工艺,以形成多个掺杂外延层。

附图说明

22.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

23.图1是本发明一实施例,所探究的高电压晶体管结构示意图;

24.图2是本发明一实施例,高电压晶体管结构示意图;及

25.图3到图4是本发明一实施例,形成外延掺杂结构的流程示意图。

26.附图标号说明

27.100:基板

28.102:高电压栅极绝缘层

29.104:栅极层

30.106:间隙壁

31.108:掺杂区域

32.108a、108b、108c:掺杂层

33.200:基板

34.202:高电压栅极绝缘层

35.204:栅极层

36.206:间隙壁

37.208:栅极结构

38.210:未掺杂外延底层

39.212、214:掺杂外延层

40.218:未掺杂外延顶层

41.220:掺杂区域

42.230:凹陷

43.250:外延掺杂结构

具体实施方式

44.本发明是关于高电压晶体管的结构及其制造方法。高电压晶体管的源极与漏极的下方增加不同导电型的外延(epitaxial)掺杂结构,可以有效提升击穿电压也可以维持大的操作电流。

45.因应可以同时在高电压操作与低电压操作的集成电路,高电压晶体管是高电压操作的主要构件。具有较高击穿电压的高电压晶体管可以提升集成电路的质量与寿命。

46.本发明提出高电压晶体管的设计,能有效提升击穿电压。以下举多个实施例来说明本发明,但是本发明不限于举多个实施例。

47.在提出可以提升击穿电压的高电压晶体管的设计前,本发明先探究(looking into)较直接的高电压晶体管的结构,其后更提出可以有效提升击穿电压的高电压晶体管。

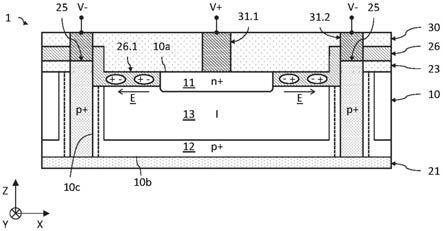

48.图1是依据本发明一实施例,所探究的高电压晶体管结构示意图。参阅图1,根据场效晶体管的结构,在金属-氧化物-半导体(metal-oxide-semiconductor,mos)的结构,其如一般低电压的场效晶体管,还是以硅基板100为基础,其上形成有栅极绝缘层102、栅极层104及在栅极层104侧壁的间隙壁106。因应高电压操作,栅极绝缘层102的厚度会增加,以承受高电压操作。另外,当作源极或是漏极的掺杂区域108也形成在基板100中,在栅极层104的两侧。高电压晶体管可以是p型晶体管或是n型晶体管。本实施例以p型晶体管为例,其掺杂区域108是p导电型。n型晶体管的导电型与p型晶体管相反。

49.为了能提升晶体管的击穿电压,掺杂区域108例如采用掺杂浓度的控制。使用多次的掺杂工艺,掺杂区域108依掺杂浓度的不同有多个掺杂层,例如包括掺杂层108a、掺杂层108b及掺杂层108c。掺杂浓度由基板100的表面往下递减(gradient decreasing)。例如,掺杂层108c的掺杂浓度大于掺杂层108b。掺杂层108b的掺杂浓度大于掺杂层108a。

50.图1的高电压晶体管结构,其掺杂区域220采用浓度是递减的设计,可以提升击穿电压,但是探究后观察到其操作电流仍可能不足够大。本发明再提出高电压晶体管的结构,可以提升击穿电压也可以维持大的操作电流。

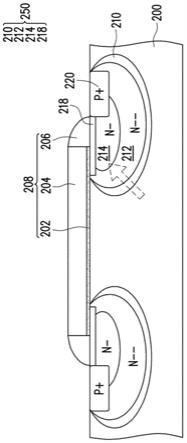

51.图2是依据本发明一实施例,高电压晶体管结构示意图。参阅图2,以基板200当作高电压晶体管的为结构基础。本实施例以p型的高电压晶体管为例来说明。对于n型的高电压晶体管,其掺质(dopant)的导电型以n型取代n型掺质即可。

52.高电压晶体管结构包括基板200。具有第一导电型例如n导电型的外延掺杂结构250,形成在基板200中。外延掺杂结构250是在基板200心形成凹陷(recess),其后在凹陷中进行外延工艺,形成外延层在凹陷。在形成外延层的过程中,有同时采用原位(in-situ)掺杂,如此外延掺杂结构250包含多层掺杂外延层212、214。另外,在外延掺杂结构250的顶部包含未掺杂外延顶层218,在外延掺杂结构250的底部,在一实施例,也包含未掺杂外延底层210介接(interfacing)于基板200。外延掺杂结构250例如包含未掺杂外延底层210、掺杂外延层212、掺杂外延层214及未掺杂外延顶层218。后面图3与图4会较详细描述。

53.栅极结构208设置在基板200上,且至少重叠于未掺杂外延顶层218。相对于第一导电型的第二导电型例如是p 的掺杂区域220,当作晶体管的源/漏极区域,是形成在外延掺杂结构250中,在栅极结构208的侧边。

54.栅极结构208包括高电压栅极绝缘层202,设置在基板200上。高电压栅极绝缘层202的厚度因应高电压,调整为足够承受高电压的程度,而不限于特定值。栅极层204例如是多晶硅层,设置在高电压栅极绝缘层202上。间隙壁206设置在基板200上,且在栅极层204的侧壁上。

55.未掺杂外延顶层218是在间隙壁206下,且延伸到高电压栅极绝缘层202的下面。此未掺杂外延顶层218在栅极层204的下方与其重叠。未掺杂外延顶层218可以产生高阻抗的效果,可以进一步防止电压击穿。

56.第一导电型例如是n型不同于掺杂区域220的第二导电型。第二导电型在此实施例是p型,以p 表示。在硅外延工艺中,例如以磷(phosphorus)提供n形掺质,也就是磷与硅组合成sip的外延材料,而依照磷的浓度,依序形成掺杂外延层212与掺杂外延层214,浓度如箭头表示往上递增,浓度以n

--

与n-表示。未掺杂外延底层210以及未掺杂外延顶层218实质上是不含磷或是含量接近于零。掺杂区域220是后续使用注入工艺所形成,而不是外延工艺所形成。其浓度是p ,当作源极与漏极的作用,会形成在外延掺杂结构250中,覆盖过未掺杂外延顶层218的一部分。

57.于此,如果要制造n型高电压晶体管,则磷的n型掺质例如可以改变为p型掺质例如是ge,掺杂外延层212、214的材料改变为sige,而当作源极与漏极的掺杂区域220则改变为n 的掺杂,其是后续注入工艺所形成。

58.于此,外延掺杂结构250的结构取代如图1直接注入到基板的方式,可以有效增加驱动电流,而对掺质的控制可以提升击穿电压。未掺杂外延顶层218更提供高阻抗效应,也可以提升击穿电压。

59.图3到图4是依据本发明一实施例,形成外延掺杂结构的流程示意图。参阅图3,在基板200例如使用屏蔽层以及湿蚀刻工艺在预定位置先形成凹陷230。参阅图4,以n型的外延掺杂结构250的结构为例,其施加sip的外延工艺,其中磷(p)的含量决定n型掺杂的浓度。对于未掺杂外延底层210与未掺杂外延顶层218,其磷(p)的含量实质上是零。于此未掺杂外延顶层218的几何外形仅是示意,实际上可以不是等厚的一层,其如图2,可以延伸到栅极层204的下方,提供高阻抗的效果。在未掺杂外延顶层218与未掺杂外延底层210之间的掺杂外

延层212、214的数量是多层,不限于实施例的二层。未掺杂外延顶层218可以采用半导体制造的适合的其它工艺来形成,不限于外延工艺。另外,在后续形成栅极结构208前,例如也可以先施加研磨平坦化的工艺。也就是,本发明形成外延掺杂结构250的工艺可以根据半导体制造技术可采用的工艺来达成所要的结构。

60.在一实施例,本发明也提供一种制造高电压晶体管的方法,其包括提供基板200,当作制造的结构基础。接着,凹陷230形成在基板200中。第一导电型例如n型的外延掺杂结构250,形成在基板200的凹陷230中。外延掺杂结构250的顶部包含未掺杂外延顶层218。栅极结构208形成在基板200上,且至少重叠于未掺杂外延顶层218。第二导电型例如p型的掺杂区域220形成在外延掺杂结构250中,在栅极结构208的侧边。第一导电型例如n型不同于所述第二导电型例如p型。

61.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。