1.本发明涉及电子电路技术领域,特别涉及一种微处理器上电过程中引脚无序状态的时序管理方法。

背景技术:

2.微处理器广泛用于通信设备、仪器仪表、医疗器械、家用电器等电子设备的智能化管理及过程控制。

3.在各个应用领域中,微处理器作为主控芯片通过引脚的逻辑高低电平输出来控制各种外围电路的工作。而在微处理器上电启动过程中,其引脚逻辑高低电平状态是无序的。即微处理器引脚输出状态可以为高电平亦可能为低电平,而这无序状态,工程师在电路设计初期无法得到确认。另一方面,由于微处理器本身处于上电启动过程中,无法对自身引脚状态进行控制管理。

4.各种电子器件、电子开关都是高电平有效或者是高电平使能。如果控制这些电子设备的微处理io管脚在启动过程中是高电平,这样就会导致被其控制的外围电路也一起被触发。

5.在微处理器控制的诸多领域,基于功耗、功能等原因,并不希望所控制的外围设备在微处理器上电过程中或者整个系统上电后也跟随工作。

6.因此,有必要提供一种微处器上电过程中引脚无序状态的时序管理方法,将微处理器上电过程中引脚的时序确定为逻辑“0”输出。

技术实现要素:

7.本发明的目的在于提供一种微处理器上电过程中引脚无序状态的时序管理方法,其能将微处理器上电过程中引脚无序状态有效的确定为低电平逻辑“0”输出。

8.为实现上述目的,本发明提供如下技术方案:

9.一种微处理器上电过程中引脚无序状态的时序管理方法,将微处理器上电过程中引脚的时序确定为逻辑“0”输出。

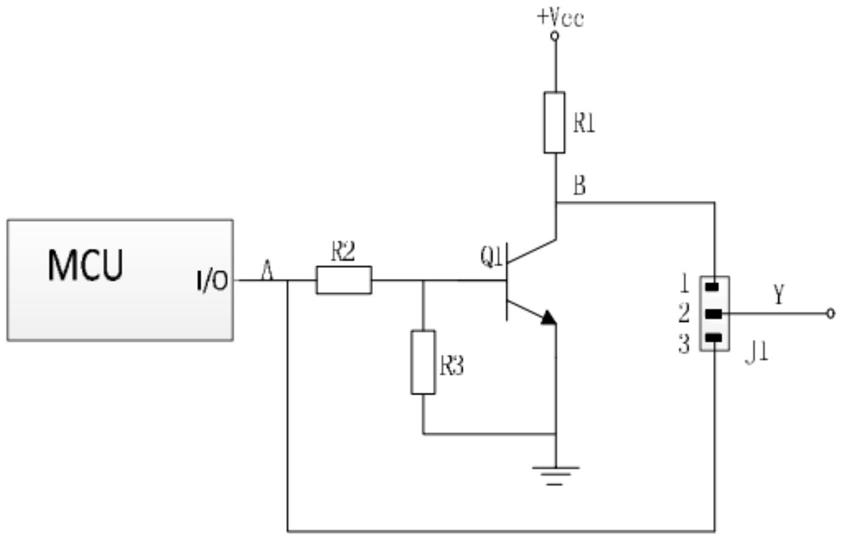

10.进一步的,电路包括一微处理器mcu、一反向器模块电路、一跳线j1。

11.进一步的,所述的反向器模块电路由一晶体管q1、一上拉电阻r1、一限流电阻r2、一晶体管q1基极对地电阻r3组成。

12.进一步的,所述的跳线j1包括跳线管脚pin1、跳线管脚pin2和跳线管脚pin3,所述跳线管脚pin1与反相器模块电路输出端b连接,所述跳线管脚pin3与微处理器i/o引脚端a连接,所述跳线管脚pin2为整定后的引脚时序逻辑“0”输出端y。

13.其中,跳线引脚的选择由跳线帽来实现。

14.基于微处理器在上电过程中,其引脚输出时序逻辑高低电平状态不确定;有可能为时序逻辑“低”,亦可能为时序逻辑“高”;当其时序逻辑“低”时,直接提供给被控制单元的控制时序逻辑电平即为“低”;当其时序逻辑为“高”时,本发明提供的反向器模块对其进行

反向,让其时序状态跳转为“低”后,提供给后端的被控制单元。

15.进一步,所述低电平为逻辑“0”,指微处理器io管脚输出电压范围为0vdc~0.7vdc,所述高电平为逻辑“1”,指微处理器io管脚输出电压范围为1.7vdc~3.3v。

16.与现有技术相比,本发明的有益效果是:本发明电路结构简单,具有通用性,能满足所有微处理器的应用需要。

附图说明

17.图1为本发明的电路结构原理图。

具体实施方式

18.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

19.请参阅图1所示,本发明提供一种技术方案:一种微处理器上电过程中引脚无序状态的时序管理方法,将微处理器上电过程中引脚的时序确定为逻辑“0”输出。

20.其中,电路包括一微处理器mcu、一反向器模块电路、一跳线j1。

21.其中,所述的反向器模块电路由一晶体管q1、一上拉电阻r1、一限流电阻r2、一晶体管q1基极对地电阻r3组成。

22.其中,所述的跳线j1包括跳线管脚pin1、跳线管脚pin2和跳线管脚pin3,所述跳线管脚pin1与反相器模块电路输出端b连接,所述跳线管脚pin3与微处理器i/o引脚端a连接,所述跳线管脚pin2为整定后的引脚时序逻辑“0”输出端y。跳线引脚的选择由跳线帽来实现。

23.具体地,基于微处理器在上电过程中,其引脚输出时序逻辑高低电平状态不确定;有可能为时序逻辑“低”,亦可能为时序逻辑“高”;当其时序逻辑“低”时,直接提供给被控制单元的控制时序逻辑电平即为“低”;当其时序逻辑为“高”时,本发明提供的反向器模块对其进行反向,让其时序状态跳转为“低”后,提供给后端的被控制单元。

24.其中,所述低电平为逻辑“0”,指微处理器io管脚输出电压范围为0vdc~0.7vdc,所述高电平为逻辑“1”,指微处理器io管脚输出电压范围为1.7vdc~3.3v。

25.具体地,对电路板进行初次上电时,跳线不插跳线帽;上电过程中,测试跳线j3的第3脚pin3的电平,即微处理器io口的输出电平,如果是低电平,跳线帽连接j3的pin2与pin3;低电平输出给后端被控电路;如果是高电平,跳线帽连接j3的pin1与pin2,即微处理器io口的电平经反相器反相为低电平后,输出给后端被控制电路。

26.其中,在所述反相器模块电路中,上拉电阻r1与电源vcc相连;r2为限流电阻,防止流过基极电流过大损坏晶体管;对地电阻r3有着重要的作用,其一为:对地电阻r3相当于基极的下拉电阻,如果a端被悬空则由于对地电阻r3的存在能够使晶体管保持在可靠的关断状态;其二为:对地电阻r3可提升三极管高电平的门槛压,保证晶体管不误导通。

27.具体地,当微处理器io输出为低电平,晶体管基极没有电流,晶体管不导通,反相器的输出端b电势为vcc;当微处理器io输出为高电平,晶体管导通,反相器的输出端b电势

为零。

28.其中,所述晶体管q1的型号为mmbt3904lt。

29.其中,所述电源 vcc为直流电平3.3v。

30.终上所述,本发明能将微处理器上电过程中引脚无序状态有效的确定为低电平即:逻辑“0”输出。本发明电路结构简单,能有效的确定微处理器上电过程中输出引脚高低电平时序,增加微处理器电路系统的可靠性,具有通用性,能满足所有微处理器的应用需要。

31.尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

技术特征:

1.一种微处理器上电过程中引脚无序状态的时序管理方法,其特征在于:将微处理器上电过程中引脚的时序确定为逻辑“0”输出。2.根据权利要求1所述的一种微处理器上电过程中引脚无序状态的时序管理方法,其特征在于:电路包括一微处理器mcu、一反向器模块电路、一跳线j1。3.根据权利要求2所述的一种微处理器上电过程中引脚无序状态的时序管理方法,其特征在于:所述的反向器模块电路由一晶体管q1、一上拉电阻r1、一限流电阻r2、一晶体管q1基极对地电阻r3组成。4.根据权利要求2所述的一种微处理器上电过程中引脚无序状态的时序管理方法,其特征在于:所述的跳线j1包括跳线管脚pin1、跳线管脚pin2和跳线管脚pin3,所述跳线管脚pin1与反相器模块电路输出端b连接,所述跳线管脚pin3与微处理器i/o引脚端a连接,所述跳线管脚pin2为整定后的引脚时序逻辑“0”输出端y。

技术总结

本发明公开了一种微处理器上电过程中引脚无序状态的时序管理方法,所述一种微处理器上电过程中引脚无序状态的时序管理方法能将微处理器上电过程中引脚无序状态有效的确定为低电平即:逻辑“0”输出;其电路包括一微控制器、一反相器模块电路、一跳线。本发明电路结构简单,能有效的确定微处理器上电过程中输出引脚高低电平时序,增加微处理器电路系统的可靠性,具有通用性,能满足所有微处理器的应用需要。要。

技术研发人员:张静 王俊波

受保护的技术使用者:湖北视拓光电科技有限公司

技术研发日:2020.09.25

技术公布日:2022/3/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。