1.本实用新型涉及集成电路技术领域,尤其涉及一种带有实时时钟的核心板。

背景技术:

2.随着自动化控制、物联网应用及各类数据采集处理系统中的应用不断扩展,各类核心板的应用也在逐步扩展中,给各类工控和数据采集处理系统新产品开发带来了功能更多的工具。核心板一般是在pcb电路板本体上设有主控制器模块、存储器模块以及与主控制器模块所对应连接的其它辅助模块,如电源模块、复位振荡模块、usb接口电路等,以此构成一个最小的开发系统。

3.rtc(real_time clock,实时时钟)功能保证时间与正常时间同步,由于时间同步的重要性,许多工业或军事类应用均对rtc功能具有要求,但现有的核心板通常不带有rtc功能,需要在使用时在外部的电路板上加设rtc实时时钟模块,对于电路布局较为不易。

技术实现要素:

4.本实用新型所要解决的技术问题是:提供一种带有实时时钟的核心板,核心板上集成了rtc实时时钟功能,无需加装rtc实时时钟模块。

5.为了解决上述技术问题,本实用新型采用的技术方案为:一种带有实时时钟的核心板,包括pcb板,所述pcb板上一面集成有有处理器、易失存储器、非易失存储器、电源管理模块和rtc实时时钟模块;

6.所述处理器通过pcb板上的走线分别与易失存储器、非易失存储器、电源管理模块和rtc实时时钟模块电连接,所述电源管理模块通过pcb板上的走线与易失存储器、非易失存储器和rtc实时时钟模块电连接;

7.所述pcb板上安装器件的一面固定安装有屏蔽罩。

8.进一步地,所述处理器是am335x处理器。

9.进一步地,所述rtc实时时钟模块是ds1339实时时钟模块。

10.进一步地,所述非易失存储器是nand flash芯片或emmc芯片。

11.进一步地,所述nand flash芯片是slc的nand flash芯片。

12.进一步地,所述核心板的对外引脚是邮票孔式引脚。

13.进一步地,所述相邻两个邮票式引脚的间隔是1.0mm。

14.进一步地,还包括沿pcb板边沿布置的屏蔽夹,所述屏蔽罩通过屏蔽夹与pcb板可拆卸地固定连接。

15.进一步地,所述核心板还包括至少一个用于指示核心板工作状态的指示灯,控制器电连接所述指示灯。

16.进一步地,所述指示灯包括运行指示灯和复位指示灯,所述控制器分别电连接所述运行指示灯和复位指示灯。

17.本实用新型的有益效果在于:一种带有实时时钟的核心板,集成了rtc实时时钟功

能,应用在工控板等设备上时,无需另外设置rtc实时时钟模块,方便了电路布局,屏蔽罩用于屏蔽外界电磁波对内部电路的影响和内部产生的电磁波向外辐射,保证核心板系统的稳定。

附图说明

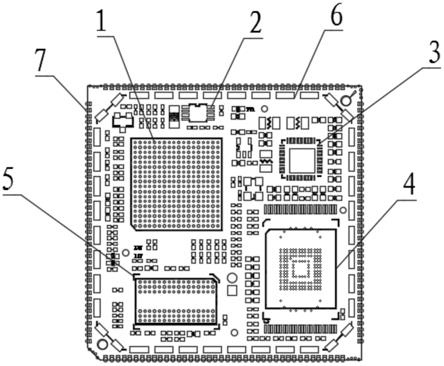

18.图1为本实用新型实施例的一种带有实时时钟的核心板的结构示意图。

19.标号说明:

20.1、处理器;2、rtc实时时钟模块;3、电源管理模块;4、非易失存储器;5、易失存储器;6、屏蔽夹;7、邮票孔式引脚。

具体实施方式

21.为详细说明本实用新型的技术内容、所实现目的及效果,以下结合实施方式并配合附图予以说明。

22.请参照图1,一种带有实时时钟的核心板,包括pcb板,所述pcb板上一面集成有有处理器、易失存储器、非易失存储器、电源管理模块和rtc实时时钟模块;

23.所述处理器通过pcb板上的走线分别与易失存储器、非易失存储器、电源管理模块和rtc实时时钟模块电连接,所述电源管理模块通过pcb板上的走线与易失存储器、非易失存储器和rtc实时时钟模块电连接;

24.所述pcb板上安装器件的一面固定安装有屏蔽罩。

25.由上述描述可知,本实用新型的有益效果在于:一种带有实时时钟的核心板,集成了rtc实时时钟功能,应用在工控板等设备上时,无需另外设置rtc实时时钟模块,方便了电路布局,屏蔽罩用于屏蔽外界电磁波对内部电路的影响和内部产生的电磁波向外辐射,保证核心板系统的稳定。

26.进一步地,所述处理器是am335x处理器。

27.由上述描述可知,am335x处理器,其主频达到1ghz,运算能力达到1600dmips,具有较高的运算性能。

28.进一步地,所述rtc实时时钟模块是ds1339实时时钟模块。

29.由上述描述可知,ds1339实时时钟模块,其备份电池最低电压低至1.3v,功耗低至na级别,可以让时钟维持更长时间且与pmic电源管理芯片兼容性更佳。

30.进一步地,所述非易失存储器是nand flash芯片或emmc芯片。

31.由上述描述可知,nand flash芯片和emmc芯片各自具有优点,核心板提供两种不同的接口供两种不同的非易失存储器使用,客户可以根据实际应用场景的需求,选择需要的非易失存储器使用。

32.进一步地,所述nand flash芯片是slc的nand flash芯片。

33.由上述描述可知,slc的nand flash芯片,具有更高的可靠性、更多的擦写寿命和更好的耐用性,更适合需要高可靠性的应用场景。

34.进一步地,所述核心板的对外引脚是邮票孔式引脚。

35.由上述描述可知,邮票孔式引脚作为对外通信的接口,其相对于插接引脚,由于不受接触度的影响,在高频震动情况下也不影响通信,具有更好的抗震性和可靠性。

36.进一步地,所述相邻两个邮票式引脚的间隔是1.0mm。

37.由上述描述可知,邮票式引脚1.0mm的间隔的核心板具有废板率低、生产成本较低、测试制具制作容易、手工焊接焊接时的不良率和smt贴装时的不良低、同样尺寸能引出的电信号数量较多和两个电信号距离远适中,符合器件孔最小间距24mil的安全距离。不会产生caf现象和短路风险的优点。

38.进一步地,还包括沿pcb板边沿布置的屏蔽夹,所述屏蔽罩通过屏蔽夹与pcb板可拆卸地固定连接。

39.由上述描述可知,采用屏蔽夹的方案安装屏蔽罩,不仅成本较低,且维修时只要把屏蔽盖拆开,即可进行维修,维修工序简单。

40.进一步地,所述核心板还包括至少一个用于指示核心板工作状态的指示灯,控制器电连接所述指示灯。

41.由上述描述可知,指示灯能用于指示核心板的工作状态,使得用户能通过指示灯了解核心板的运行情况。

42.进一步地,所述指示灯包括运行指示灯和复位指示灯,所述控制器分别电连接所述运行指示灯和复位指示灯。

43.由上述描述可知,运行指示灯用于指示核心板处于上电运行状态,复位指示灯用于指示核心板处于复位状态。

44.实施例一

45.请参照图1,本实施例的一种带有实时时钟的核心板,其包括pcb板,pcb板上安装有处理器1、易失存储器5、非易失存储器4、电源管理模块3和rtc实时时钟模块2。

46.处理器1通过pcb板上的走线分别与易失存储器5、非易失存储器4、电源管理模块3和rtc实时时钟模块2电连接,电源管理模块3通过pcb板上的走线与易失存储器5、非易失存储器4和rtc实时时钟模块2电连接。

47.具体的,本实施例中,处理器1采用am335x处理器1,其主频达到1ghz,运算能力达到1600dmips;rtc实时时钟模块2采用ds1339实时时钟模块,其备份电池最低电压低至1.8v,功耗低至na级别,可以让时钟维持更长时间;易失存储器5采用ddr3 ram,其具有较高的运行性能和较低的成本;非易失存储器4采用nada flash芯片和emmc芯片,其中,emmc芯片,其具有结构极其简单、体积超小、低复杂度、高度集成、低布线难度的优点,且emmc能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也较快,nada flash具体采用了slc的nada flash芯片,其相对于emmc具有更高的可靠性、更多的擦写寿命和更好的耐用性,相对emmc芯片更适合需要高可靠性的应用场景。

48.本实施例中,全部电路和器件均集成于一块45mm*45mm的pcb板上,pcb板的四边分布160个邮票孔式引脚7,引脚与pcb板上各个模块电连接,作为对外通信的接口,其相对于插接引脚,由于不受接触度的影响,在高频震动情况下也不影响通信,具有更好的抗震性和可靠性。

49.本实施例中,相邻两个邮票式引脚之间的间隔具体是1.0mm,邮票式引脚1.0mm的间隔的核心板具有废板率低、生产成本较低、测试制具制作容易、手工焊接焊接时的不良率和smt贴装时的不良低、同样尺寸能引出的电信号数量较多和两个电信号距离远适中,符合器件孔最小间距24mil的安全距离。不会产生caf现象和短路风险的优点。

50.还包括沿核心板边沿布置的屏蔽夹6,屏蔽夹6用于可拆卸地固定安装屏蔽罩,采用屏蔽夹6的方案安装屏蔽罩,不仅成本较低,且维修时只要把屏蔽盖拆开,即可进行维修,维修工序简单。屏蔽罩用于屏蔽外界电磁波对内部电路的影响和内部产生的电磁波向外辐射,保证核心板系统的稳定。

51.本实施例中,核心板上具有运行(run)指示灯和复位(rst)指示灯,控制器分别电连接运行指示灯和复位指示灯,运行指示灯在核心板上电运行的时候闪烁作为心跳灯指示核心板处于上电运行状态,复位指示灯用于在核心板复位时闪动,表示核心板处于复位状态。

52.综上所述,本实用新型提供的一种带有实时时钟的核心板,集成了rtc实时时钟功能,具有低能耗、结构简单等优点,且设置了屏蔽罩以屏蔽外部电池波对内部电路的影响,保证核心板系统的稳定运行。

53.以上所述仅为本实用新型的实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等同变换,或直接或间接运用在相关的技术领域,均同理包括在本实用新型的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。