一种ldmosfet、制备方法及芯片和电路

技术领域

1.本发明涉及半导体领域,具体地涉及一种ldmosfet、制备方法及芯片和电路。

背景技术:

2.ldmosfet器件常常被用于各种应用,例如汽车应用中。现有技术中常常通过降低ldmosfet器件中的表面电场(resurf)结构来防止高压施加于漏极造成击穿。通常的ldmosfet制造工艺采用hvnw,hvpw, nrf 和p-body注入,形成高压的pn结,尤其是hynw和hvpw注入能量很高,需要长时间高温推阱,这对光刻工艺、离子注入设备和扩散设备都有很高的要求。

技术实现要素:

3.本发明实施例的目的是提供一种ldmosfet、制备方法及芯片和电路,该ldmosfet不需要高能量离子注入,具有工艺简单,成本低的特点。

4.为了实现上述目的,本发明实施例提供一种ldmosfet,包括:衬底,所述衬底上设有外延层;所述外延层上方依次设有第一重掺杂n 离子、p型硅、n型硅及第二重掺杂n 离子;所述p型硅中设有轻掺杂n型离子,所述n型硅中设有轻掺杂p型离子。

5.可选的,所述轻掺杂n型离子与所述轻掺杂p型离子均呈柱状分布。

6.可选的,所述p型硅与所述n型硅相接构成pn结。

7.可选的,所述ldmosfet的上方设有多晶硅。

8.可选的,所述n型硅上形成厚氧化层,所述厚氧化层为sio2。

9.可选的,所述衬底为p型衬底。

10.另一方面,本发明提供一种ldmosfet的制备方法,包括:形成衬底,所述衬底上形成外延层;所述外延层上方依次形成第一重掺杂n 离子、p型硅、n型硅及第二重掺杂n 离子;所述p型硅中形成轻掺杂n型离子,所述n型硅中形成轻掺杂p型离子。

11.可选的,所述n型硅上形成厚氧化层,所述厚氧化层为sio2。

12.可选的,所述轻掺杂n型离子与所述轻掺杂p型离子均呈柱状分布。

13.可选的,所述p型硅与所述n型硅相接构成pn结。

14.另一方面,本发明提供一种芯片,该芯片包括上述所述的ldmosfet。

15.另一方面,本发明还提供一种电路,该电路包括上述所述的ldmosfet。

16.本发明提供的一种ldmosfet包括:衬底,所述衬底上设有外延层;所述外延层上方依次设有第一重掺杂n 离子、p型硅、n型硅及第二重掺杂n 离子;所述p型硅中设有轻掺杂n型离子,所述n型硅中设有轻掺杂p型离子。该ldmosfet不需要高能量离子注入,具有工艺简单,成本低的特点。

17.本发明实施例的其它特征和优点将在随后的具体实施方式部分予以详细说明。

附图说明

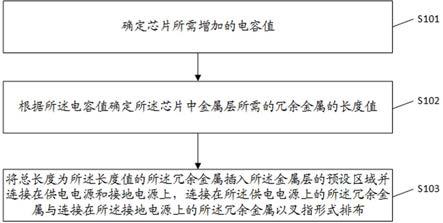

18.附图是用来提供对本发明实施例的进一步理解,并且构成说明书的一部分,与下面的具体实施方式一起用于解释本发明实施例,但并不构成对本发明实施例的限制。在附图中:图1-图5是本发明的一种ldmosfet的制备方法的示意图。

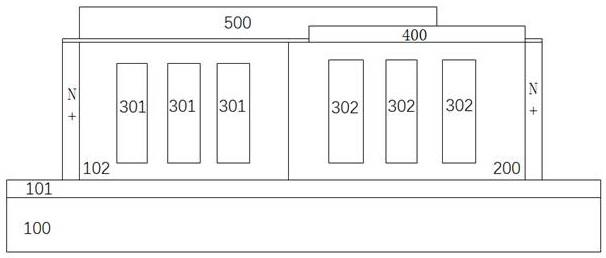

19.附图标记说明100-衬底;101-外延层;102-p型硅;200-n型硅;301-轻掺杂n型离子;302-轻掺杂p型离子;400-二氧化硅;500-多晶硅。

具体实施方式

20.以下结合附图对本发明实施例的具体实施方式进行详细说明。应当理解的是,此处所描述的具体实施方式仅用于说明和解释本发明实施例,并不用于限制本发明实施例。

21.本发明提供了一种ldmosfet,如图5所述,所述ldmosfet包括:衬底100,所述衬底100优选为p型衬底,所述衬底100上设有外延层101;所述外延层101上方依次设有第一重掺杂n 离子、p型硅102、n型硅200及第二重掺杂n 离子,所述第一重掺杂n 离子和第二重掺杂n 离子设于所述p型硅102、n型硅200的两侧,其掺杂浓度相同,所述第一重掺杂n 离子和第二重掺杂n 离子用于增加耗尽层宽度。按照一种优选的实施方式,重掺杂浓度的范围为5e19~3e20/cm3。

22.所述p型硅102中设有轻掺杂n型离子301,所述n型硅200中设有轻掺杂p型离子302,优选的,所述轻掺杂n型离子301与所述轻掺杂p型离子302均呈柱状分布,具体的分布密度和离子浓度可以根据击穿电压确定,按照一种优选的实施方式,所述分布密度为1~1.5um/1,所述轻掺杂n型离子301与所述轻掺杂p型离子302的离子浓度为1e15~1e16,击穿电压范围为几十伏特到几百伏特。

23.所述轻掺杂n型离子301与p型硅102形成超级pn结,减少了导通电流和击穿电压,同理,所述轻掺杂p型离子302与n型硅200形成超级pn结,减少了导通电流和击穿电压。并且,所述p型硅102与所述n型硅200相接构成pn结,用于减小击穿电压。

24.所述ldmosfet没有高能的hvpw(高压n阱区)、hvnw(高压p阱区)、nrf(n型漂移区)及p-body(n型体区)等高能量离子注入,并且不需要光刻技术,制作过程也不需要长时间的高温推阱,所以所述ldmosfet具有工艺简单实用,生产成本低等特点。

25.本发明还提出了一种ldmosfet的制备方法,包括:形成衬底100,所述衬底100上形成外延层101;所述外延层101上方依次形成第一重掺杂n 离子、p型硅102、n型硅200及第二重掺杂n 离子;所述p型硅102中形成轻掺杂n型离子301,所述n型硅200中形成轻掺杂p型离子302。所述轻掺杂n型离子301注入p型硅102前及所述轻掺杂p型离子302注入n型硅200前

均预先注入光刻胶。优选的,所述轻掺杂n型离子301与所述轻掺杂p型离子302均呈柱状分布。所述p型硅102与所述n型硅200相接构成pn结。

26.图1-图5是本发明的一种ldmosfet的制备方法的示意图,具体的,如图1所示,定制满足要求厚度和浓度的衬底100(soi),也可以在衬底100上面再长一层外延层101,以满足厚度和浓度的要求,所述外延层101上长出一层p型硅102。

27.接下来对图1中的p型硅102光刻出一定区域,所述区域注入n型离子形成n型硅200,然后再次光刻,干法刻蚀掉不需要硅的区域,形成如图2所示的结构。

28.然后,轻掺杂p型离子302注入光刻,在n型硅200里面注入轻掺杂p型离子302,然后是轻掺杂n型离子301注入光刻,在p型硅102里面注入轻掺杂n型离子301,形成如图3所示的结构。

29.如图4所示,对图3中的ldmosfet进行cvd sio2及光刻,并干法刻蚀sio2,然后扩散,在p型硅102和n型硅200的侧面形成n 掺杂的源漏,用于增加耗尽层宽度。

30.如图5所示,接下来部分去除cvd sio2,剩下的cvd sio2用于n型硅200上的厚氧化层,增加隔离效果,然后在p型硅102上和小部分n型硅200上进行栅氧化工艺,最后,lpcvd多晶硅和掺杂,栅氧化物(poly gate)光刻及干法刻蚀形成最终的ldmosfet。

31.本发明提出的一种ldmosfet包括:衬底100,所述衬底100上设有外延层101;所述外延层101上方依次设有第一重掺杂n 离子、p型硅102、n型硅200及第二重掺杂n 离子;所述p型硅102中设有轻掺杂n型离子301,所述n型硅200中设有轻掺杂p型离子302。所述轻掺杂n型离子301与p型硅102形成超级pn结,以及所述轻掺杂p型离子302与n型硅200也形成超级pn结,二者均减少了导通电流和击穿电压。所述ldmosfet没有高能的hvpw(高压n阱区)、hvnw(高压p阱区)、nrf(n型漂移区)及p-body(n型体区)等高能量离子注入,并且不需要光刻技术,制作过程也不需要长时间的高温推阱,所以其具有工艺简单实用,生产成本低等特点。

32.以上结合附图详细描述了本发明实施例的可选实施方式,但是,本发明实施例并不限于上述实施方式中的具体细节,在本发明实施例的技术构思范围内,可以对本发明实施例的技术方案进行多种简单变型,这些简单变型均属于本发明实施例的保护范围。

33.另外需要说明的是,在上述具体实施方式中所描述的各个具体技术特征,在不矛盾的情况下,可以通过任何合适的方式进行组合。为了避免不必要的重复,本发明实施例对各种可能的组合方式不再另行说明。

34.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括要素的过程、方法、商品或者设备中还存在另外的相同要素。

35.以上仅为本技术的实施例而已,并不用于限制本技术。对于本领域技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本技术的权利要求范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。