一种iii-v族半导体晶圆的减薄方法

技术领域

1.本发明涉及一种iii-v族半导体的加工工艺,具体涉及一种iii-v族半导体晶圆的减薄方法。

背景技术:

2.iii-v族化合物,是元素周期表中iii族的b,al,ga,in和v族的n,p,as,sb形成的化合物,通常所说的iii-v族半导体是由上述iii族和v族元素所形成的两元化合物,其成分化学比为1:1。iii-v族化合物半导体材料在光电子器件、光电集成、超高速微电子器件和超高频微波器件及电路上已得到了重要应用,具有广阔前景。目前工业上所使用的iii-v族半导体主要为砷化镓(gaas)、磷化铟(inp)和氮化镓(gan)。

3.在实际应用中,出于散热和减小芯片电路尺寸需要,iii-v族半导体器件封装过程中一般需要对衬底进行减薄。通常的做法是先通过外延生长、蚀刻等工艺在整块晶圆的正面制作出由一系列分割线划分出的多个器件单元,然后通过对整块晶圆的背面进行研磨和抛光来将厚度减薄,最后按照分割线将完成减薄后的晶圆分割为一系列独立的半导体器件(芯片)。

4.由于iii-v族半导体与硅半导体在物理性能和化学性能方面存在的较大差异,现有成熟的硅半导体研磨工艺往往无法应用于iii-v族半导体,这就为iii-v族半导体的减薄工艺带来了一系列问题。目前主流的iii-v族半导体减薄方法采用上下蜡工艺,具体如下:1、先在晶圆正面制作一层保护层,以防止表面的器件表面在后续过程中被刮伤;2、加热载具(例如蓝宝石片、玻璃片或不锈钢托盘等),在其表面涂布热塑性的粘结剂(通常采用石蜡),粘结剂受热融化为液态;然后将晶圆背面朝上地放置于载具上并加压,液态粘结剂会填充两者表面之间的间隙,多余的粘结剂则会从中间往边缘排出;然后降温冷却,晶圆和载具相结合;这一工艺过程由于多采用石蜡作为粘结剂,因此通常被称为上蜡工艺;3、对晶圆背面采用研磨、抛光等工艺进行减薄处理;4、将载具连同晶圆放入去蜡液(例如丙酮)中浸泡并加热,去蜡液溶解晶圆和载具之间的粘结剂和保护层,溶解过程从晶圆边缘往中心逐渐进行,最终使得晶圆和载具分离;通常被称为湿法下蜡工艺;然后就可以对晶圆进行进一步的清洗以及裂片等后续操作。

5.在上述减薄工艺中,上蜡工艺过程中的鼓蜡和湿法下蜡工艺耗时是其中主要的两个问题。不同的晶圆具有不同的表面平整度,当晶圆表面结构极为平整时,上蜡工艺过程中晶圆和载具之间多余的液态粘结剂在加压时多余的石蜡不易排出,容易残留在内部造成晶圆局部鼓起,会导致减薄后鼓起的位置厚度偏低,通常称这一现象为鼓蜡;晶圆尺寸越大,厚度越薄,此现象越明显。在湿法下蜡时,由于晶圆和载具之间的间距比较小,去蜡液跟保护层、粘结剂相接触的区域溶解度易达到饱和,导致去蜡液往晶圆中心渗透的速度慢,工艺处理耗时长;晶圆尺寸越大,表面越平整,此现象越明显。

技术实现要素:

6.本发明所要解决的技术问题在于克服现有技术不足,提供一种iii-v族半导体晶圆的减薄方法,可有效克服上蜡工艺过程中的鼓蜡及湿法下蜡工艺耗时的技术问题,同时提升生产质量和生产效率。

7.本发明具体采用以下技术方案解决上述技术问题:一种iii-v族半导体晶圆的减薄方法,包括以下步骤:在晶圆正面制作保护层;使用上蜡工艺将晶圆固定在载具上;对晶圆背面进行减薄处理;使用湿法下蜡工艺将晶圆与载具分离;所述保护层中设置有一系列与晶圆边缘连通的沟槽,所述沟槽的深度小于或等于保护层的厚度。

8.优选地,所述沟槽的深度等于保护层厚度。

9.优选地,所述一系列沟槽纵横交错排布;或者,所述沟槽是以晶圆圆心为端点的射线状沟槽。

10.优选地,所述保护层材料为光刻胶。

11.进一步优选地,使用光刻工艺在所述保护层中制作出所述沟槽。

12.优选地,所述上蜡工艺中所使用的粘合剂为石蜡。

13.优选地,所述下蜡工艺中所使用的去蜡液为丙酮。

14.优选地,所述载具的材料为蓝宝石、玻璃、不锈钢或陶瓷。

15.进一步地,所述iii-v族半导体晶圆的减薄方法还包括:对分离后的晶圆进行清洁的步骤。

16.相比现有技术,本发明技术方案具有以下有益效果:本发明采用设置有沟槽结构的保护层,在上蜡工艺过程中,晶圆和载具之间多余的液态粘合剂在加压时会进入这些沟槽并通过沟槽排出,不会聚集鼓起;在湿法下蜡时,去蜡液容易通过这些沟槽往晶圆中心渗透,溶解速度快,晶圆和载具容易分离。

附图说明

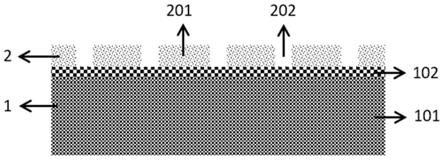

17.图1、图2分别为具体实施例中保护层制作完成后晶圆结构的主视图和俯视图;图3为具体实施例中研磨过程中的晶圆结构示意图;图4为具体实施例中湿法下蜡工艺过程中的晶圆结构示意图;1、晶圆,101、衬底,102、外延和电路层,2、保护层,201、光刻胶,202、沟槽,3、载具,4、粘合剂,401、载具与晶圆之间多余的粘合剂,5、去蜡液,501、沟槽内的去蜡液。

具体实施方式

18.针对技术所存在的上蜡工艺过程中的鼓蜡及湿法下蜡工艺耗时的技术问题,本发明的解决思路是采用设置有沟槽结构的保护层,在上蜡工艺过程中,晶圆和载具之间多余的液态粘合剂在加压时会进入这些沟槽并通过沟槽排出,不会聚集鼓起;在湿法下蜡时,去蜡液容易通过这些沟槽往晶圆中心渗透,溶解速度快,晶圆和载具容易分离;从而同时提高生产质量和生产效率。

19.本发明所提出的iii-v族半导体晶圆的减薄方法,包括以下步骤:在晶圆正面制作保护层;使用上蜡工艺将晶圆固定在载具上;对晶圆背面进行减薄处理;使用湿法下蜡工艺

将晶圆与载具分离;所述保护层中设置有一系列与晶圆边缘连通的沟槽,所述沟槽的深度小于或等于保护层的厚度。

20.优选地,所述沟槽的深度等于保护层厚度。

21.优选地,所述一系列沟槽纵横交错排布;或者,所述沟槽是以晶圆圆心为端点的射线状沟槽。

22.优选地,所述保护层材料为光刻胶。

23.进一步优选地,使用光刻工艺在所述保护层中制作出所述沟槽。

24.优选地,所述上蜡工艺中所使用的粘合剂为石蜡。

25.优选地,所述下蜡工艺中所使用的去蜡液为丙酮。

26.优选地,所述载具的材料为蓝宝石、玻璃、不锈钢或陶瓷。

27.进一步地,所述iii-v族半导体晶圆的减薄方法还包括:对分离后的晶圆进行清洁的步骤。

28.为了便于公众理解,下面通过一个具体实施例并结合附图来对本发明的技术方案进行详细说明:本实施例以4英寸砷化镓晶圆的减薄为例,其具体工艺流程如下:步骤1、保护层制作:如图1、图2所示,先在包括衬底101和外延及电路层102的晶圆1的正面通过匀胶、烘烤、曝光、显影等光刻工艺涂布光刻胶201并在其中制作出一系列与晶圆边缘连通的沟槽202,带有沟槽202的光刻胶201即形成用以防止器件表面在后续过程中被刮伤的保护层2;本实施例中的光刻胶厚度为5~10um,沟槽202为横、竖垂直两个方向,宽度20~100um,深度等于光刻胶201的厚度,相邻沟槽间距100~1000um。

29.步骤2、上蜡:加热载具3(本实施例中为不锈钢托盘),在其表面涂布热塑性的粘合剂4(本实施例中为石蜡),石蜡受热由固态融化为液态;将晶圆1背面朝上地放置于托盘上,然后加压和冷却,使得托盘与晶圆正面贴合;在加压的过程中,托盘和晶圆之间多余的粘合剂401会进入到沟槽202内。

30.步骤3、减薄处理:对晶圆背面使用研磨抛光等工艺进行减薄处理;如图3所示,本实施例中将晶圆背面朝下固定,下部的研磨盘向上缓慢移动对晶圆背面进行研磨,研磨工艺采用现有技术,为节省篇幅起见,这里不做具体描述。

31.步骤4、下蜡:如图4所示,将托盘连同晶圆放入去蜡液5(本实施例中为丙酮溶液)中加热浸泡,去蜡液会通过沟槽202往晶圆1的中心渗透,即图中的501;待去蜡液将托盘和晶圆之间的粘合剂和保护层(即石蜡和光刻胶)完全溶解后,晶圆和托盘分离。

32.步骤5、晶圆清洁:对晶圆进行后续清洗。

33.为验证本发明技术方案的效果,用表面光滑纯平,厚度为625um的4寸砷化镓晶圆假片分别采用传统工艺和本发明工艺进行多次实测,传统工艺的步骤1中的保护层未做沟槽结构,步骤2中上蜡后通常会有0~2处晶圆鼓起,鼓起高度10~20um左右;步骤4湿法下蜡6小时后均未完成晶圆和托盘分离;而采用本发明工艺,即在保护层做了沟槽的,步骤2中上蜡后均未发现晶圆鼓起,步骤4的湿法下蜡均在30分钟内完成晶圆和托盘的分离。显然,本发明技术方案可同时提高iii-v族半导体晶圆的生产质量和生产效率,且实现成本低廉,具有相当高的推广应用价值。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。