1.本发明涉及一种基于异构众核架构的直接内存访问编译优化方法,属于编译优化技术领域。

背景技术:

2.当前深度学习模型越来越复杂,计算数据量暴增,访存逐渐成为性能优化的瓶颈,直接内存访问(dma)方式可以很好解决该问题。直接内存访问(dma)是一种无需cpu的参与就可以让外部设备与系统内存之间进行双向数据传输的硬件机制,完全由硬件执行i/o交换任务,数据不经过运算控制核心而直接在内存和运算核心之间进行,减少了大批量数据传输的开销,从而大大提高系统的吞吐率。

3.深度学习编译器的作用是将深度学习工作负载部署在特定硬件平台以高效完成训练和推理任务,其能够充分挖掘人工智能领域算法特点和模式化特征,将多种典型深度学习框架的模型转化为统一的计算图,再通过一系列领域算法指导的编译优化技术和体系结构相关的底层优化技术,生成面向不同硬件平台的高效代码,用以加速深度学习中的推理过程。tvm(tensor virtual machine)是当今非常流行的一款深度学习编译器,它针对不同的深度学习框架和硬件平台,实现了统一的软件栈,以尽可能高效的方式,将不同框架下的深度学习模型部署到硬件平台。

4.国产异构众核处理器采用新型直接内存访问(dma)机制,该机制不同于现有的cpu/gpu架构,采用“dma操作 回答字判断“相结合的方式完成异步数据交换,完全由硬件执行i/o交换任务,数据不经过运算控制核心而直接在内存和运算核心之间进行,减少了大批量数据传输的开销,具有编程灵活,使用便捷的特点。但是,目前深度学习编译器tvm并不支持针对国产异构众核处理器的dma调度优化。

技术实现要素:

5.本发明的目的是提供一种基于异构众核架构的直接内存访问编译优化方法,其充分利用硬件资源,最大程度实现算子的计算访存操作的重叠,从而提升深度学习负载在异构众核平台上的性能。

6.为达到上述目的,本发明采用的技术方案是:提供一种基于异构众核架构的直接内存访问编译优化方法,包括以下步骤:s1、通过调度原语cache_read,将张量数据由主存搬移到局存,具体如下:s11、对结果张量b计算过程所依赖的张量数据a,为其定义局存副本aa,并通过调度原语cache_read将张量数据a由主存搬移到局存副本aa;s12、将局存副本aa绑定到结果张量b计算过程的循环x的位置;s2、通过调度原语pragma,将s11中的数据搬移操作改写为dma get操作,具体如下:对于局存副本aa,将其数据搬移方式由循环load改写为dma get操作;s3、通过调度原语double_buffer,将s2中的dma get操作优化为双缓冲模式,具体

如下:s31、如果不进行双缓冲优化,则使用基本的异步dma操作,则跳转s4;s32、如果需要进行双缓冲优化,则在s2中调度原语pragma的基础上,将局存副本aa的dma get操作优化为双缓冲模式;s4、通过调度原语pragma,在局存副本aa使用位置前插入回答字判断操作,具体如下:s41、对于s31的情况,在局存副本aa使用位置前插入基本回答字判断操作;s42、对于s32的情况,在局存副本aa使用位置前插入双缓冲回答字判断操作;s5、通过调度原语cache_write,将结果张量b的局存副本bb由局存搬移至主存,具体如下:s51、对结果张量b,为其定义局存副本bb,并且通过调度原语cache_write将局存副本bb搬移到结果张量b;s52、将局存副本bb绑定到结果张量b计算过程的循环y的位置。

7.由于上述技术方案的运用,本发明与现有技术相比具有下列优点:本发明提供了一种基于异构众核架构的直接内存访问编译优化方法,基于国产异构众核处理器的深度学习编译器tvm,通过一系列调度原语,将串行的访存操作变换为异步dma方式,并且提供了双缓冲模式以支持具有依赖关系的计算访存优化,充分利用硬件资源,最大程度实现算子的计算访存操作的重叠,从而提升深度学习负载在异构众核平台上的性能。

附图说明

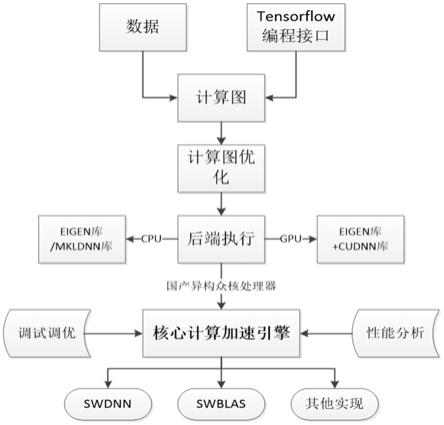

8.附图1为本发明编译优化方法流程图。

具体实施方式

9.实施例:本发明提供一种基于异构众核架构的直接内存访问编译优化方法,具体包括以下步骤:s1、通过调度原语cache_read,将张量数据由主存搬移到局存,具体如下:s11、对结果张量b计算过程所依赖的张量数据a,为其定义局存副本aa,并通过调度原语cache_read将张量数据a由主存搬移到局存副本aa;s12、考虑到局存容量的限制,将局存副本aa绑定到结果张量b计算过程的循环x的位置;s2、通过调度原语pragma,将s11中的数据搬移操作改写为dma get操作,具体如下:对于局存副本aa,将其数据搬移方式由循环load改写为dma get操作;s3、通过调度原语double_buffer,将s2中的dma get操作优化为双缓冲模式,具体如下:s31、如果不进行双缓冲优化,仅使用基本的异步dma操作,则跳转s4;s32、如果需要进行双缓冲优化,则在s2中调度原语pragma的基础上,将局存副本aa的dma get操作优化为双缓冲模式;s4、通过调度原语pragma,在局存副本aa使用位置前插入回答字判断操作,具体如

下:s41、对于s31的情况,在局存副本aa使用位置前插入基本回答字判断操作;s42、对于s32的情况,在局存副本aa使用位置前插入双缓冲回答字判断操作;s5、通过调度原语cache_write,将结果张量b的局存副本bb由局存搬移至主存,具体如下:s51、对结果张量b,为其定义局存副本bb,并且通过调度原语cache_write将局存副本bb搬移到结果张量b;s52、考虑到局存容量的限制,将局存副本bb绑定到结果张量b计算过程的循环y的位置。

10.对上述实施例的进一步解释如下:本发明提出一种基于异构众核架构的直接内存访问编译优化方法,具体流程如图1所示,主要包括将张量数据由主存搬移到局存、将数据搬移操作改写为dma get操作、在数据使用位置前插入回答字判断操作、将dma get操作优化为双缓冲模式、以及将局存数据搬移到主存五个步骤,具体如下:s1、首先,通过调度原语cache_read,将张量数据由主存搬移到局存,具体如下:s11、对结果张量b计算过程所依赖的张量数据a,为其定义局存副本aa,并通过调度原语cache_read将张量数据a由主存搬移到局存副本aa,相应的dsl如下:aa = s.cache_read(a,

ꢀ“

local”, [b]);s12、考虑到局存容量的限制,将局存副本aa绑定到结果张量b计算过程的循环x的位置,相应的dsl如下:s[aa].compute_at(s[b], x);s2、其次,通过调度原语pragma,将s11中的数据搬移操作改写为dma get操作,具体如下:s21、对于局存副本aa,将其数据搬移方式由循环load改写为dma get操作,相应的dsl如下:s[aa].pragma(s[aa].op.axis[0],

ꢀ“

dma_copy”);s3、再次,如果需要进行双缓冲优化,则通过调度原语double_buffer,将s21中的dma get操作优化为双缓冲模式,具体如下:s31、如果不进行双缓冲优化,仅使用基本的异步dma操作,则跳转s4;s32、如果需要进行双缓冲优化,则在s2中调度原语pragma的基础上,将局存副本aa的dma get操作优化为双缓冲模式,相应的dsl如下:s[aa].double_buffer();s4、再次,通过调度原语pragma,在局存副本aa使用位置前插入回答字判断操作,具体如下:s41、对于s31的情况,在局存副本aa使用位置前插入基本回答字判断操作,相应的dsl如下:s[aa].pragma(s[aa].op.axis[0],

ꢀ“

barrier_default 1”);s42、对于s32的情况,在局存副本aa使用位置前插入双缓冲回答字判断操作,相应的dsl如下:s[aa].pragma(s[aa].op.axis[0],

ꢀ“

barrier_double_buffer 1”);s5、最后,通过调度原语cache_write,将结果张量b的局存副本bb由局存搬移至主存,具体如下:s51、对结果张量b,为其定义局存副本bb,并且通过调度原语cache_write将局存副本bb搬移到结果张量b,相应的dsl如下:bb = s.cache_write(b,

ꢀ“

local”);

s52、考虑到局存容量的限制,将局存副本bb绑定到结果张量b计算过程的循环y的位置,相应的dsl如下:s[bb].compute_at(s[b], y)。

[0011]

采用上述一种基于异构众核架构的直接内存访问编译优化方法时,其基于国产异构众核处理器的深度学习编译器tvm,通过一系列调度原语,将串行的访存操作变换为异步dma方式,并且提供了双缓冲模式以支持具有依赖关系的计算访存优化,充分利用硬件资源,最大程度实现算子的计算访存操作的重叠,从而提升深度学习负载在异构众核平台上的性能。

[0012]

为了便于更好的理解本发明,下面将对本文中使用的术语进行简要的解释:编译:将源程序(高级语言)翻译成目标程序(低级语言或机器语言)的过程。

[0013]

异构众核:采用新型的片上异构融合体系结构。

[0014]

深度神经网络:有很多隐藏层的神经网络,又称为深度前馈网络或多层感知机。

[0015]

tvm:tensor virtual machine,亚马逊公司推出的一款深度学习编译器,能够将深度学习工作负载部署在特定硬件平台以高效完成推理任务。

[0016]

直接内存访问:direct memory access,由硬件执行i/o交换任务,数据不经过cpu,直接由源地址批量搬运到目的地址。

[0017]

上述实施例只为说明本发明的技术构思及特点,其目的在于让熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限制本发明的保护范围。凡根据本发明精神实质所作的等效变化或修饰,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。