1.本发明属于神经拟态类脑计算技术领域,具体涉及一种面向类脑计算芯片的自学习实现系统。

背景技术:

2.随着冯诺依曼体系架构计算机“内存墙”与“功耗墙”效应日趋严重,学术界和工业界都在不断探索新型计算模式。随着生物科学的不断进步特别是脑科学的发展,科学家们发现人脑是一部能效极高的计算机,且具备冯诺依曼计算体系架构不可比拟的特征与优势。因此,构建类脑计算机去模拟大脑神经网络的结构与运行机制,被认为是解决后摩尔时代冯诺依曼架构所面临挑战的重要路径之一。

3.目前业界已经推出多款模仿大脑的神经拟态类脑计算芯片(简称向类脑计算芯片),比如ibm的truenorth、intel的loihi、清华的tianjic、浙大的darwin等,但是支持自学习功能的并不多,比较成熟的只有loihi,也存在不足。

4.自学习是神经拟态类脑计算芯片区别于传统人工智能芯片的主要特点之一,目前学习算法还在不断的演进完善中,在神经拟态类脑计算芯片上实现自学还仍存在许多挑战,主要有以下两方面:首先是时间空间信息记录难,类脑计算芯片的学习依赖于突触前信息和突触后信息,即神经元收到的脉冲序列信息和发出的脉冲序列信息。不同于传统神经元网络只有空间维度的信息,脉冲网络的学习还需要考虑时间维度的信息。比如脉冲时间依赖的可塑性(stdp)是一种目前已知的常用的大脑学习模型,其基于突触前后发放脉冲时间相关性进行学习,但stdp学习规则所需信息的时间和空间跨度较大,如果对一定时间窗口内的脉冲序列进行完整的记录,将会占用大量的存储器资源,因此必须有一种机制能够将神经元发出和收到的脉冲序列进行压缩并记录。

5.其次是学习规则多样化,目前面向神经拟态类脑计算的学习算法还不够成熟,神经科学家提出了多种新的大脑学习模型或者基于stdp的变种模型,且大脑的学习模型还在不断的演进完善中,新的模型还在涌现。因此需要有一种灵活可变的学习规则实现机制,以适应不同的学习模型。

6.此外,由于神经拟态类脑计算高度并行的特点,神经拟态类脑计算芯片往往采用分布式实现,各神经元间的通信难度将会变大。因此需要一种基于局部信息进行学习的方式。

技术实现要素:

7.鉴于上述,本发明的目的是提供一种面向类脑计算芯片的自学习实现系统,在减少存储资源的同时,支持面向类脑计算芯片的在线自学习。

8.为实现上述发明目的,本发明提供的技术方案为:一种面向类脑计算芯片的自学习实现系统,包括支持神经拟态计算且能针对类脑

计算芯片的局部神经元信息进行自学习的多个学习节点,每个学习节点包括:神经拟态计算模块,用于根据输入的前脉冲序列对神经元进行膜电位累加,并判断是否产生脉冲,将产生的后脉冲序列输出到目标学习节点;指令编码学习模块,用于根据参数可配置的公式化学习规则生成数据管理指令和权重更新指令,依据数据管理指令和权重更新指令分别实现学习信息存储模块中脉冲序列的管理和神经元连接权重的更新;学习信息存储模块,用于采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加后进行存储空间的共享存储,还用于根据脉冲类型为压缩后的脉冲序列建立多索引;其中,脉冲序列包括前脉冲序列、后脉冲序列、奖励脉冲序列。

9.在一个实施例的学习信息存储模块中,采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加,包括:基于参数可配置的多阶滤波函数构建多阶脉冲滤波器,每阶滤波函数表示为:,,其中,t表示时刻,i和均表示滤波阶数索引,表示t时刻第i阶滤波处理后的脉冲序列,表示t时刻输入的待滤波脉冲序列,表示第i阶滤波处理时的脉冲强度系数,表示t-1时刻第i-j阶滤波处理后的脉冲序列,表示第i阶滤波处理时 对应的衰减系数,和为可配置参数,n为自然数;利用构建的多阶脉冲滤波器对脉冲序列进行滤波并叠加处理,以得到每阶压缩后脉冲序列。

10.在一个实施例的学习信息存储模块中,对压缩后脉冲序列进行存储空间共享的存储,包括:为同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列在存储空间动态分配存储起始地址,然后将同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列拼接后按照动态分配的存储起始地址进行存储。

11.在一个实施例的学习信息存储模块中,根据脉冲类型为压缩后的脉冲序列建立多索引,包括:针对前脉冲序列,为压缩后的前脉冲序列建立树突编号索引;针对后脉冲序列和奖励脉冲序列,为压缩后的后脉冲序列和压缩后的奖励脉冲序列建立神经元编号索引。

12.在一个实施例中,神经拟态计算模块包括:树突单元,用于记录存储神经元与树突的第一连接关系、神经元连接权重,还用于将树突传入的脉冲序列依据第一连接关系和神经元连接权重累积到神经元形成前脉冲序列后,输出前脉冲序列至神经元推理单元;神经元推理单元,用于依据前脉冲序列对神经元是否产脉冲进行推理计算,以得到后脉冲序列;轴突单元,用于记录学习节点之间的第二连接关系、轴突与树突的第三连接关系,还用于依据第二连接关系和第三连接关系,将神经元推理单元计算的后脉冲序列输出至目标学习节点的目标树突。

13.在一个实施例的指令编码学习模块中,根据参数可配置的公式化学习规则生成数据管理指令,包括:数据管理指令由包括载入/存储l/s、脉冲类型class以及滤波阶数order的公式化学习规则生成,通过采用独热码方式载入配置的l/s、class以及order以生成不同数据管理指令;根据数据管理指令实现学习信息存储模块中脉冲序列的管理,包括:依据数据管理指令实现对前脉冲序列、后脉冲序列以及奖励脉冲序列于学习信息存储模块的载入和存储。

14.在一个实施例的指令编码学习模块中,根据参数可配置的公式化学习规则生成权重更新指令,包括:权重更新指令由包括脉冲序列变量fcph、系数cph以及更新公式formula的公式化学习规则生成,通过采用独热编码方式载入配置的cph和fcph,载入的cph和fcph结合到更新公式formula,以生成不同权重更新指令;根据权重更新指令实现神经元连接权重的更新,包括:根据权重更新指令实现神经元连接权重的更新,并将更新的神经元连接权重传输至神经拟态计算模块的树突单元进行记录存储。

15.在一个实施例中,输入的前脉冲序列经过神经拟态计算模块完成一个时间步的神经元正向推导后,启动指令编码学习模块以实现神经元正向推导过程中的脉冲序列的记录和神经元连接权重的更新。

16.在一个实施例的指令编码学习模块中,权重参数学习过程中权重更新指令可以被多次调用以实现权重更新参数的累加。

17.与现有技术相比,本发明具有的有益效果至少包括:学习信息存储模块中,通过参数可配置的多阶脉冲滤波器可以对每时每刻新脉冲序列信息滤波处理并叠加到原始记录的脉冲序列信息中,既可以提高自学习模块的工作效率,又可以大幅度降低存储空间的需求,解决神经拟态类脑计算在线学习所需信息时空跨度大的问题。

18.指令编码学习模块中,将神经拟态类脑学习机制通过参数化方法抽象并公式化,通过配置公式化学习规则参数以形成权重更新指令,通过简单的权重更新指令实现复杂的学习机理,以适应神经拟态类脑计算学习规则的多样化。

19.自学习实现系统可实现在线学习,针对类脑计算芯片突触分布式特点,通过分布式的学习节点仅利用局部脉冲序列信息进行权重自主调节,不需要大量通信,且实现学习过程的大规模并行,提高学习效率。

附图说明

20.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图做简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动前提下,还可以根据这些附图获得其他附图。

21.图1是实施例提供的自学习实现系统的结构示意图;图2是实施例提供的脉冲序列压缩记录原理图;图3是实施例提供的学习节点的结构示意图。

具体实施方式

22.为使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例对本发明进行进一步的详细说明。应当理解,此处所描述的具体实施方式仅仅用以解释本发明,并不限定本发明的保护范围。

23.类脑计算芯片主要以脉冲神经网络实现学习功能,在脉冲神经网络中,每个神经元节点包括树突、神经元以及轴突,通过树突传入的脉冲信号在神经元进行积累后,产生脉冲信号并经轴突传出。大规模脉冲神经网络中实现在线学习算法的关键在于如何利用局部信息和有限计算资源去克服学习规则中所需信息的时间空间跨度大问题。因此,必须在神经元节点内记录脉冲信息。然而,由于学习规则需要的脉冲序列具有很长的时间跨度,在有限的存储资源下无法完整记录脉冲序列。这就需要一种压缩存储记录方式实现在有限存储资源下对脉冲序列的完整记录。再者,基于类脑计算芯片的自学习的分布特性和学习规则多样化。实施例提供了一种面向类脑计算芯片的自学习实现系统。

24.图1是实施例提供的自学习实现系统的结构示意图。如图1所示,实施例提供的自学习实现系统包括分布式布局的多个学习节点。每个学习节点实现对类脑计算芯片的局部神经元信息的自学习,包括神经拟态计算模块、学习信息存储模块和指令编码学习模块。

25.其中,学习信息存储模块中,采用脉冲序列信息压缩记录方式,即采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加,具体包括:首先,基于参数可配置的多阶滤波函数构建多阶脉冲滤波器,每阶滤波函数表示为:,,其中,t表示时刻,i和均表示滤波阶数索引,表示t时刻第i阶滤波处理后的脉冲序列,表示t时刻输入的待滤波脉冲序列,表示第i阶滤波处理时的脉冲强度系数, 表示t-1时刻第i-j阶滤波处理后的脉冲序列,表示第i阶滤波处理时对应的衰减系数,n为自然数。

26.构建多阶脉冲滤波器时,滤波器的阶段不受限制,根据应用需求自行设置。每阶滤波器采用的滤波函数的可配置参数为和,每阶滤波函数除了对上一时刻的当前阶滤波结果利用衰减系数进行衰减,还对上一时刻的低阶滤波结果利用衰减系数进行衰减,然后将所有衰减结果叠加到脉冲强度压缩前脉冲序列得到的结果,以得到最终压缩后脉冲序列。

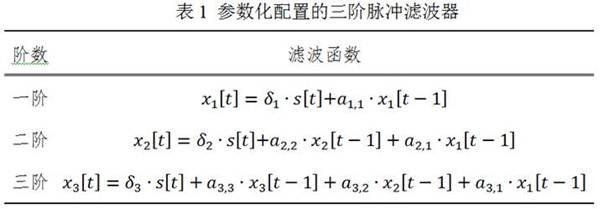

27.表1示例性地给出了可参数化配置的三阶脉冲滤波器。其中,t时刻的一阶滤波值基于输入脉冲序列t时刻的滤波值和t-1时刻一阶滤波值产生,即通过衰减系数结合t时刻之前的滤波值,实现压缩脉冲序列为一个值。二阶滤波值可以结合一阶滤波值、二阶滤波值产生。三阶滤波值则可以结合一阶滤波值、二阶滤波值、三阶信息滤波值产生。

28.其中,可配置参数分别为、、。

29.然后,利用构建的多阶脉冲滤波器对脉冲序列进行滤波并叠加处理,以得到每阶压缩后脉冲序列。

30.上述脉冲序列信息压缩记录方式可以将每时每刻的脉冲序列根据参数编码的规则叠加到原先记录的信息中,以大幅降低存储空间的需求。

31.学习信息存储模块中,采用存储空间的共享方式,即对压缩后脉冲序列进行存储空间的共享存储,包括:为同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列在存储空间动态配置存储起始地址,以实现存储空间的动态分配。然后将同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列拼接后按照动态分配的存储起始地址进行存储,以实现压缩后脉冲序列于存储空间的共享存储。

32.学习信息存储模块中,根据脉冲类型为压缩后的脉冲序列建立多索引,包括:针对前脉冲序列,为压缩后的前脉冲序列建立树突编号索引;针对后脉冲序列和奖励脉冲序列,为压缩后的后脉冲序列和压缩后的奖励脉冲序列建立神经元编号索引。

33.图2是实施例提供的脉冲序列压缩记录原理图。如图2所示,x

fi,n

表示前脉冲序列,x

pi,n

表示后脉冲序列和x

ri,n

表示奖励脉冲序列,下标i,n分别表示滤波阶数和脉冲序列索引编号。时刻的一阶滤波值根据时刻的输入脉冲序列和时刻的一阶滤波值产生,对应采用一阶滤波函数。时刻的二阶滤波值根据时刻的输入脉冲序列、时刻的一阶滤波值和 时刻的二阶滤波值产生,对应采用二阶滤波函数。时刻的三阶滤波值根据时刻的输入脉冲序列、时刻的一阶滤波值、时刻的二阶滤波值和时刻的三阶滤波值产生,对应采用三阶滤波函数。同阶滤波处理后的前脉冲序列x

fi,n

、后脉冲序列x

pi,n

、奖励脉冲序列x

ri,n

拼接存储在同一地址下,如图2中每一行。在存储器中,前脉冲序列x

fi,n

采用索引2,即树突编号索引dedr_id,后脉冲序列x

pi,n

和励脉冲序列x

ri,n

采用索引1,即神经元编号索引neu_id。

34.图3是实施例提供的学习节点的结构示意图。如图3所示,实施例提供的学习节点用于利用分布式的神经元局部信息进行自学习。神经拟态计算模块包括树突单元、神经元推理单元、轴突单元。

35.其中,树突单元用于记录存储神经元与树突的第一连接关系map1、神经元连接权重,还用于将树突传入的脉冲序列依据第一连接关系map1和神经元连接权重累积到神经元形成前脉冲序列后,输出前脉冲序列至神经元推理单元。

36.神经元推理单元用于依据前脉冲序列对神经元是否产脉冲进行推理计算,以得到后脉冲序列。具体地,利用神经元模型指令并根据输入的前脉冲序列进行膜电位累加,通过

比较膜电位是否超过阈值来计算神经元是否产生脉冲,当超过阈值时,则认为产生后脉冲并输出。

37.轴突单元用于记录学习节点之间的第二连接关系map2、轴突与树突的第三连接关系map3,还用于依据第二连接关系map2和第三连接关系map3,将神经元推理单元计算的后脉冲序列输出至目标学习节点的目标树突。

38.图3中,箭头表示脉冲神经网络正向推导流程中的数据流,树突单元收到带有树突编号的脉冲信息,从树突存储中获取神经元与树突的第一连接关系map1和神经元连接权重,依据该第一连接关系map1记录得到前脉冲序列;神经元推理单元根据神经元模型对输入的前脉冲序列进行计算,判断是否发放脉冲,并输出发放的后脉冲序列,轴突单元根据学习节点之间的第二连接关系map2,先索引到目标学习节点,再根据发出后脉冲序列的神经元编号和轴突与树突的第三连接关系map3索引到目标学习节点的目标树突,并将后脉冲序列传输至目标树突。

39.如图3所示,指令编码学习模块用于根据参数可配置的公式化学习规则生成数据管理指令和权重更新指令,依据数据管理指令和权重更新指令分别实现学习信息存储模块中脉冲序列的管理和神经元连接权重的更新。

40.需要说明的是,输入的前脉冲序列经过神经拟态计算模块,即经过树突单元、神经元推理单元以及轴突单元完成一个时间步的神经元正向推导后,启动指令编码学习模块以实现神经元正向推导过程中的脉冲序列的记录和神经元连接权重的更新。

41.指令编码学习模块中,采用根据参数可配置的公式化学习规则生成数据管理指令,数据管理指令实现脉冲序列于学习信息存储模块的载入和存储。

42.具体地,通过数据管理指令实现神经元正向推导过程中的脉冲序列的存储,即将输入的前脉冲序列、产生的后脉冲序列经过多阶脉冲滤波器压缩后,分别采用树突编号索引方式和神经元编号索引方式记录于学习信息存储模块,同时,对输入的用于奖励自学习的奖励脉冲序列采用神经元编号索引方式记录于学习信息存储模块。

43.具体地,通过数据管理指令实现神经元连接权重的更新过程中脉冲序列的调用,即从学习信息存储模块中调用前脉冲序列、后脉冲序列以及奖励脉冲序列进行自学习,实现神经元连接权重的更新。

44.实施例中,数据管理指令由包括载入/存储l/s、脉冲类型class以及滤波阶数order的公式化学习规则生成,通过采用独热码方式载入配置的l/s、class以及order到运算寄存器以生成不同数据管理指令,即不同的lspar指令。表2示例性地给出了针对三阶脉冲滤波处理脉冲序列的lspar指令。

45.其中,位宽1bit的l/s中,当配置为0表示载入操作,当配置为1表示存储操作;位宽3bit的class中,通过配置每个位参数为0或1,以配置脉冲类型,如3’b111表示同时载入前脉冲、后脉冲和奖励脉冲,位宽3bit的order中,通过配置每个位参数为0或1,以配置滤波阶数,如3’b011表示同时载二阶脉冲序列和三阶脉冲序列。

46.指令编码学习模块中,根据参数可配置的公式化学习规则生成权重更新指令,通过执行权重更新指令,实现神经元连接权重的更新,并将更新的神经元连接权重传输至神经拟态计算模块的树突单元进行记录存储。

47.实施例中,权重更新指令由包括脉冲序列变量fcph、系数cph以及更新公式formula的公式化学习规则生成,通过采用独热编码方式载入配置的cph和fcph到运行寄存器,载入的cph和fcph结合到更新公式formula,以生成不同权重更新指令,即不同的upsyn指令。表3示例性地给出了调用三阶脉冲滤波处理脉冲序列的upsyn指令。

48.其中,x

f1

, x

p1

, x

r1

分别表示经过一阶滤波的前脉冲序列、后脉冲序列、奖励脉冲序列,x

f2

, x

p2

, x

r2

分别表示经过二阶滤波的前脉冲序列、后脉冲序列、奖励脉冲序列,x

f3

, x

p3

, x

r3

分别表示经过三阶滤波的前脉冲序列、后脉冲序列、奖励脉冲序列,位宽9bit的fcph中,通过配置每个位参数为0或1,以配置参与权重参数更新计算的脉冲序列变量,即以通过范式配置控制更新公式的形式,比如9’b100100100表示更新公式中选择x

f1

、x

f2

、x

f3

,位宽1bit的cph中,当配置为0bit表示采用默认系数,当配置为1表示采用配置系数。formula中, 表示神经元连接权重的更新量,表示配置的脉冲序列变量,表示配置的系数,m表示脉冲序列变量的索引,符号表示将加到原神经元连接权重上。

49.实施例中,利用构建的权重更新指令更新神经元连接权重时,利用生成的数据管理指令从存储模块中调用选择的脉冲序列变量对应的压缩后脉冲序列参与神经元连接权重的更新计算,同时也从树突单元的存储器中获取原神经元连接权重参与更新计算,更新后的神经元连接权重重新写回树突单元的存储器中。

50.指令编码学习模块中,权重参数学习过程中upsyn指令可以被多次调用以实现权重更新参数的累加。

51.采用指令可编码的公式化学习规则,研究主流的神经拟态类脑学习机制,进行参数化抽象并公式化,通过配置公式中的参数实现各种复杂的学习机理。通过以上简单的学习指令实现复杂的学习机理,以适应神经拟态类脑计算学习规则的多样化。

52.以上所述的具体实施方式对本发明的技术方案和有益效果进行了详细说明,应理解的是以上所述仅为本发明的最优选实施例,并不用于限制本发明,凡在本发明的原则范围内所做的任何修改、补充和等同替换等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。