技术特征:

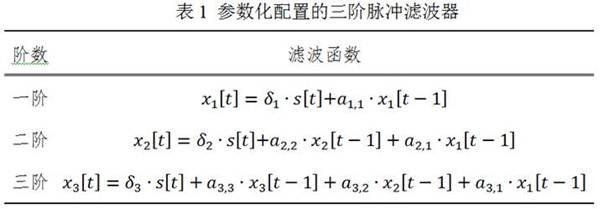

1.一种面向类脑计算芯片的自学习实现系统,其特征在于,包括支持神经拟态计算且能针对类脑计算芯片的局部神经元信息进行自学习的多个学习节点,每个学习节点包括:神经拟态计算模块,用于根据输入的前脉冲序列对神经元进行膜电位累加,并判断是否产生脉冲,将产生的后脉冲序列输出到目标学习节点;指令编码学习模块,用于根据参数可配置的公式化学习规则生成数据管理指令和权重更新指令,依据数据管理指令和权重更新指令分别实现学习信息存储模块中脉冲序列的管理和神经元连接权重的更新;学习信息存储模块,用于采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加后进行存储空间共享的存储,还用于根据脉冲类型为压缩后的脉冲序列建立多索引;其中,脉冲序列包括前脉冲序列、后脉冲序列、奖励脉冲序列。2.根据权利要求1所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述学习信息存储模块中,采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加,包括:基于参数可配置的多阶滤波函数构建多阶脉冲滤波器,每阶滤波函数表示为:,,其中,t表示时刻,i和均表示滤波阶数索引,表示t时刻第i阶滤波处理后的脉冲序列,表示t时刻输入的待滤波脉冲序列,表示第i阶滤波处理时的脉冲强度系数,表示t-1时刻第i-j阶滤波处理后的脉冲序列,表示第i阶滤波处理时对应的衰减系数,和为可配置参数,n为自然数;利用构建的多阶脉冲滤波器对脉冲序列进行滤波并叠加处理,以得到每阶压缩后脉冲序列。3.根据权利要求1所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述学习信息存储模块中,对压缩后脉冲序列进行存储空间共享的存储,包括:为同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列在存储空间动态分配存储起始地址,然后将同阶脉冲滤波器处理后的前脉冲序列、后脉冲序列、奖励脉冲序列拼接后按照动态分配的存储起始地址进行存储。4.根据权利要求1所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述学习信息存储模块中,根据脉冲类型为压缩后的脉冲序列建立多索引,包括:针对前脉冲序列,为压缩后的前脉冲序列建立树突编号索引;针对后脉冲序列和奖励脉冲序列,为压缩后的后脉冲序列和压缩后的奖励脉冲序列建立神经元编号索引。5.根据权利要求1所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述神经拟态计算模块包括:树突单元,用于记录存储神经元与树突的第一连接关系、神经元连接权重,还用于将树突传入的脉冲序列依据第一连接关系和神经元连接权重累积到神经元形成前脉冲序列后,输出前脉冲序列至神经元推理单元;神经元推理单元,用于依据前脉冲序列对神经元是否产脉冲进行推理计算,以得到后脉冲序列;

轴突单元,用于记录学习节点之间的第二连接关系、轴突与树突的第三连接关系,还用于依据第二连接关系和第三连接关系,将神经元推理单元计算的后脉冲序列输出至目标学习节点的目标树突。6.根据权利要求1所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述指令编码学习模块中,根据参数可配置的公式化学习规则生成数据管理指令,包括:数据管理指令由包括载入/存储l/s、脉冲类型class以及滤波阶数order的公式化学习规则生成,通过采用独热码方式载入配置的l/s、class以及order以生成不同数据管理指令;根据数据管理指令实现学习信息存储模块中脉冲序列的管理,包括:依据数据管理指令实现对前脉冲序列、后脉冲序列以及奖励脉冲序列于学习信息存储模块的载入和存储。7.根据权利要求5所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述指令编码学习模块中,根据参数可配置的公式化学习规则生成权重更新指令,包括:权重更新指令由包括脉冲序列变量fcph、系数cph以及更新公式formula的公式化学习规则生成,通过采用独热编码方式载入配置的cph和fcph,载入的cph和fcph结合到更新公式formula,以生成不同权重更新指令;根据权重更新指令实现神经元连接权重的更新,包括:根据权重更新指令实现神经元连接权重的更新,并将更新的神经元连接权重传输至神经拟态计算模块的树突单元进行记录存储。8.根据权利要求1-7任一项所述的面向类脑计算芯片的自学习实现系统,其特征在于,输入的前脉冲序列经过神经拟态计算模块完成一个时间步的神经元正向推导后,启动指令编码学习模块以实现神经元正向推导过程中的脉冲序列的记录和神经元连接权重的更新。9.根据权利要求1-7任一项所述的面向类脑计算芯片的自学习实现系统,其特征在于,所述指令编码学习模块中,权重参数学习过程中权重更新指令被多次调用以实现权重更新参数的累加。

技术总结

本发明公开了一种面向类脑计算芯片的自学习实现系统,包括支持神经拟态计算且能针对类脑计算芯片的局部神经元信息进行自学习的多个学习节点,每个学习节点包括:神经拟态计算模块,用于根据输入的前脉冲序列对神经元进行膜电位累加,并判断是否产生脉冲,将产生的后脉冲序列输出到目标学习节点;指令编码学习模块,用于根据参数可配置的公式化学习规则生成数据管理指令和权重更新指令,并分别实现学习信息存储模块中脉冲序列的管理和神经元连接权重的更新;学习信息存储模块,用于采用参数可配置的多阶脉冲滤波器对脉冲序列压缩叠加后进行存储空间共享的存储,还用于根据脉冲类型为压缩后的脉冲序列建立多索引。类型为压缩后的脉冲序列建立多索引。类型为压缩后的脉冲序列建立多索引。

技术研发人员:马德 李一涛 金孝飞 孙世春 陆启明 潘纲

受保护的技术使用者:浙江大学

技术研发日:2022.02.17

技术公布日:2022/3/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。