1.本发明涉及根据独立权利要求的前序部分的碳化硅(sic)晶体管器件和用于制造碳化硅(sic)晶体管器件的方法。

背景技术:

2.功率晶体管器件广泛地用于切换高电流和承受高电压。金属氧化物半导体场效应晶体管(mosfet)和绝缘栅双极型晶体管(igbt)是用于大规模或超大规模的集成电路的最重要的功率电子器件。低导通电阻和大负载电流使其非常适合用作开关器件。在功率晶体管中,控制信号被供应至与半导体衬底电绝缘的栅电极,并且通过传输电荷载流子来传导电流。功率晶体管采用类似于当今的vlsi电路的半导体处理技术,尽管器件的几何形状、电压和电流水平与在vlsi器件中所使用的设计有显著不同。大多数的晶体管,特别是用于在存储技术中储存数据的晶体管,仍然由硅(si)制成。然而,随着电子技术的发展,高温、高频等对半导体器件和电路的要求越来越高。由于si的材料特性,si无法满足这些要求——特别是对于功率开关的要求,并且因此sic材料已被开发用于在高功率、高温和高频下操作的半导体器件。对于功率开关应用,绝缘栅双极型晶体管(igbt)和金属氧化物半导体场效应晶体管(mosfet)被广泛使用。这些元件具有栅电极部分与元件本体电绝缘的结构。由于只需要对由栅电极和元件本体构成的电容器进行充电和放电,因此栅极控制电流显著小于例如栅极可关断晶体管的电流。

3.us 2013/043490 a1公开了一种半导体器件,该半导体器件包括:半导体层,该半导体层布置在衬底的主表面上并且由宽带隙半导体制成;沟槽,该沟槽布置在半导体层中,并且具有底部和侧表面;绝缘区,该绝缘区布置在沟槽的底部和侧表面上;和导电层,该导电层布置在沟槽中并且通过绝缘区而与半导体层绝缘。绝缘区包括栅极绝缘膜和间隙,该栅极绝缘膜布置在沟槽的底部和侧表面上;该间隙在沟槽的底部处布置在栅极绝缘膜与导电层之间。栅极绝缘膜在沟槽的侧表面的一部分上与导电层接触,但在沟槽的底部处不与导电层接触。从沟槽的底部贯穿到导电层的下表面测量的绝缘区的厚度在沟槽的中心周围比在沟槽的侧表面附近更大。

4.从ep 2 922 094 a2已知一种半导体器件,该半导体器件包括:n型sic层;sic区,该sic区设置在n型sic层上并且含有1

×

10

18

cm-3

或更多且1

×

10

22

cm-3

或更少的量的h(氢)或d(氘);和金属层,该金属层设置在sic区上。此外,在ep 2 922 094 a2中公开了一种用于生产其的方法。

5.us 5,455,432 a1公开了一种具有碳化物夹层的金刚石半导体器件,该金刚石半导体器件包括金刚石层和绝缘栅极结构,该金刚石层在其中具有第一传导类型的半导体金刚石区,该绝缘栅极结构在金刚石层的面上。相对薄的碳化物界面层设置在绝缘栅极结构与金刚石层之间,以便抑制诸如面处的界面态之类的电活性缺陷的形成。通过抑制面处的界面态的形成,碳化物界面层抑制了电荷载流子从金刚石层到绝缘栅极结构的寄生泄漏。碳化物界面层可以是本征碳化硅或本征难熔金属碳化物(例如,tic或wc),或者该层可以具

有相反的传导类型,从而与金刚石层形成p-n异质结。碳化物界面层和绝缘栅极结构可以用于各种不同的金刚石电子器件中,诸如mis电容器、增强型和埋沟道的绝缘栅极场效应晶体管(igfet)、表面沟道的和埋沟道的电荷耦合器件(ccd)、探测器、异质结器件和其他相关的场效应器件。还公开了相关的制造方法。

6.us 9,224,858 a1公开了一种场效应晶体管(fet)(例如,横向双扩散金属氧化物半导体场效应晶体管(ldmosfet))和形成该fet的方法。在fet中,蚀刻终止垫在半导体衬底(例如,p型硅衬底)上。半导体层(例如,硅层)也在该衬底上,并且在蚀刻终止垫上横向延伸。第一阱区(例如,n阱区)延伸穿过半导体层进入衬底中,使得该第一阱区含有蚀刻终止垫。第二阱区(例如,p阱区)在第一阱区中,在蚀刻终止垫上方对齐。源极区(例如,n型源极区)在第二阱区中。埋绝缘区(例如,埋气隙绝缘区)在第一阱区内,在蚀刻终止垫下方对齐,以便限制竖直电容器的形成。

7.wo 1997/33308公开了sic上的金属锇(os),os形成了保持牢固附接到sic表面的接触部,并且形成了抵抗从导电金属扩散的有效势垒。在n型sic上,os形成了陡峭的肖特基(schottky)整流结和肖特基二极管,该肖特基整流结具有达到至少1050℃时基本上不变的工作特性,该肖特基二极管达到1175℃仍维持可工作,并且势垒高度超过1.5ev。在p型sic上,os形成具有10-4

ohmcm2的比接触电阻的欧姆接触部。通过在tic层上沉积wc层,然后沉积金属w层,可以形成到sic衬底上的tic层的欧姆和整流接触部。这种接触部至少在1150℃下是稳定的。电极或直接地或经由保护性结合层(诸如,pt或ptau合金)连接到接触部。

8.通过使用碳化硅作为元件的基础材料,并且通过将源极区和栅极区所在的平面位置在空间上分离,并且使用具有与源电极和第二半导体层电接触的优良晶体匹配的碳化钛,从而获得能够双面压焊的元件结构,jph 0730111 a公开了在包括漏极电极层和碳化钛的衬底上,第一半导体层、第二半导体层和第三半导体层包括一个叠置在另一顶部上的p型和n型掺杂碳化硅的外延层和源极电极层。在从第三半导体层延伸到第一半导体层的凹陷部分上形成栅极绝缘膜,并且在顶部上形成栅电极。由于栅电极设置在凹陷部分处,因此源极电极和栅电极的平面位置在空间上分离开。由与碳化硅具有优良晶体匹配的碳化钛层形成源极电极17与第二半导体层之间的接触部,从而能够得到双面压焊,从而实现具有优良的碳化硅放热特性的大电流性质。

9.理想的功率晶体管将具有非常短的转换时间、接近零的开关导通电阻r

ds(on)

和无限的功率处理能力。这些特性在很大程度上取决于器件物理和技术。当功率开关的高侧导通时,可能会导致开关节点上的高的dv/dt转换。由于米勒电容(=栅极-漏极电容)反馈,电压的这种急剧上升可能会在低侧的mosfet栅极上造成电压脉冲。如果栅极阈值电压是低的,则这种情况的发生可能比具有高栅极阈值的mosfet更频繁。由跨电容建立电压变化所需的时间来确定开关器件的开关性能。rg是栅极的分布电阻,并且与有源面积近似成反比。ls和ld是源极引线电感和漏极引线电感,并且大约为几个时态的nh。在数据表中给出的输入电容(c

iss

)、输出电容(c

oss

)和反向传输电容(c

rss

)的典型值被电路设计人员用作确定电路部件值的起点。

技术实现要素:

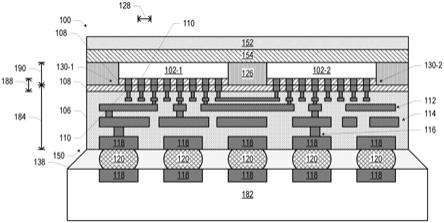

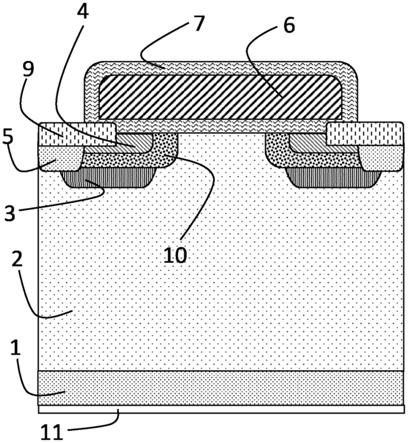

10.因此,本发明的目的是改善射穿(shoot-through)承受能力以保护例如在图1a和

图1b中示出的mos基sic的平面型器件和沟槽型器件,图1a示出了现有技术的沟槽型器件,并且图1b示出了现有技术的平面型器件。图1a和图1b中的两种现有技术的器件是的竖直开关,该竖直开关将竖直流动的电流从n型源极4切换到由栅极6控制的n型漏极11。在sic衬底1上提供n型外延漂移层2。图1a和图1b中的两种器件包括p阱区3、n型源极区4、p型接触区5、栅极电介质7和栅极6。同时在图1a所示的器件中,栅极6和栅极电介质7形成在延伸穿过p阱3的沟槽内,图1b中的栅极结构6、7在器件的顶部上是平面的。根据图1b的平面型器件进一步详细示出了沟道区8。

11.根据本发明的一个实施例的碳化硅(sic)晶体管器件包括:sic半导体衬底,所述sic半导体衬底具有顶表面;sic外延层,所述sic外延层形成在所述sic半导体衬底的顶表面上,所述sic外延层具有顶表面;源极结构,所述源极结构形成在所述sic外延层的顶表面中,所述源极结构具有顶表面,并且包括p阱区、n型源极区和p型接触区;源极接触结构,所述源极接触结构形成在所述源极结构的顶表面上并且电连接至所述源极结构的顶表面,其中所述接触结构包含碳化钛(tic)、碳化钨(wc)和碳化镍(nic3)中的一者;栅极结构,所述栅极结构包括栅极电介质和栅极流道;以及p型沟道区;其中所述栅极电介质覆盖所述沟道区、所述源极结构的至少部分和所述源极接触结构的至少部分,并且其中所述栅极流道通过所述栅极电介质而与所述沟道区、所述源极结构和所述源极接触结构电绝缘,并且所述栅极流道与所述源极接触结构的至少部分和所述沟道区重叠,其中所述栅极结构是平面结构。

12.在另一实施例中,所述源极接触结构具有2nm至200nm范围内的厚度。

13.在另一实施例中,所述sic半导体衬底是4h-sic衬底。

14.在另一实施例中,所述碳化硅(sic)晶体管器件是绝缘栅双极型晶体管(igbt)。

15.在另一实施例中,所述碳化硅(sic)晶体管器件是金属氧化物半导体场效应晶体管(mosfet)。

16.本发明的另一实施例涉及一种用于制造碳化硅(sic)晶体管器件的方法,该方法包括如下步骤:在sic半导体衬底的顶表面上外延地形成sic外延层,所述sic外延层具有顶表面;在所述sic外延层的顶表面中形成源极结构,所述源极结构具有顶表面,并且包括p阱区、n型源极区和p型接触区;在所述源极结构的顶表面上形成源极接触结构,并且所述源极接触结构电连接到所述源极结构的顶表面,其中所述接触结构包含碳化钛(tic)、碳化钨(wc)和碳化镍(nic3)中的一者;以及在形成所述源极接触结构之后,形成包括栅极电介质和栅极流道的栅极结构,使得所述栅极电介质覆盖所述源极结构的至少部分和所述源极接触结构的至少部分,并且使得通过所述栅极电介质而与所述源极结构和所述源极接触结构电绝缘的所述栅极流道与所述源极接触结构的至少部分重叠,其中所述器件包括p型沟道,并且其中所述栅极结构是平面结构。

17.在用于制造碳化硅(sic)晶体管器件的方法的另一实施例中,在600℃至1300℃的范围内的温度下形成所述源极接触结构。

18.通过参考附图进行的本发明的示例性实施例的以下详细描述,本发明的前述和其他目的、特征和优点将变得更加明显。

transistor,sic-bjt)。

29.由于tic与n型sic形成电欧姆接触结,并且tic在高于1000℃的温度下在表面粗糙度和电性能方面非常稳定,因此可以在氧化物沉积/氧化过程之前制造碳化钛(tic)源极接触部。这种氧化物沉积/氧化过程是必要的,例如,对于栅极电介质形成、栅极绝缘或钝化是必要的,以及对于(例如,用于栅极流道的)多晶硅层沉积和高温暴露/活化步骤是必要的。对于常规的镍硅化物源极接触部,由于镍硅化物接触部的温度敏感性,必须在源极接触部沉积之前执行氧化物沉积/氧化过程。因此,tic源极接触部的使用允许集成需要高热预算的全新的过程步骤。在图2a至图2c中示出用于制造平面型竖直功率mosfet的典型的集成次序。

30.从图2a中的平面型mos基器件开始,其中在sic衬底1上提供n型外延漂移层2。图2a至图2c中的器件还包括p阱区3、n型源极区4、p型接触区5、和p型沟道区10。如上面已经提到的,与现有技术的制造过程相反,根据本发明的制造过程的实施例,在形成栅极结构(该栅极结构由栅极6和可以是栅极电介质的栅极绝缘体7构成)之前,按照过程步骤的顺序,形成用于接触该源极区4的tic接触结构9。需要强调的是,根据本发明的制造过程的实施例,在tic源极接触结构9之后形成栅极结构6、7。因为tic承受高温的能力,(改变制造过程步骤的顺序的)这种集成方案是可能的。

31.作为对比示例,在图2d中示出了具有沟槽栅极结构的竖直功率mosfet。在该对比示例中,栅极结构不是平面地形成在sic半导体衬底1的顶表面上,而是在p阱区3内且在n型源极区4之间竖直地形成沟槽中。在该对比示例中,栅电极6形成在沟槽内并且被栅极电介质7绝缘。

32.本发明的另一实施例涉及一种用于制造碳化硅(sic)晶体管器件的方法,该方法包括如下步骤:在sic半导体衬底1的顶表面上外延地形成sic外延层2,该sic外延层2具有顶表面;在sic外延层2的顶表面中形成源极结构3、4、5,该源极结构3、4、5具有顶表面;在源极结构3、4、5的顶表面之上形成源极接触结构9,并且该源极接触结构9电连接该源极结构3、4、5的顶表面,其中接触结构9包含碳化钛(tic)、碳化钨(wc)和碳化镍(nic3)中的一者;在形成源极接触结构9之后形成包括栅极电介质7和栅极流道6的栅极结构6、7,使得该栅极电介质7覆盖该源极结构3、4、5的至少部分和源极接触结构9的至少部分,并且通过栅极电介质7而与源极结构3、4、5和源极接触结构9电绝缘的栅极流道6与源极接触结构9的至少部分重叠。

33.在用于制造碳化硅(sic)晶体管器件的方法的另一实施例中,在600℃至1300℃的范围内的温度下形成源极接触结构9。

34.在另一实施例中,例如,可以使用四氯化钛作为ti源并且使用乙烯作为碳源,在稀释氢中,在1200℃至1300℃的范围内,通过化学气相沉积(chemical vapor deposition,cvd)过程,来形成具有70nm厚度的tic接触层。该温度在tic形成时对tic进行退火。在一实施例中,例如,tic厚度可以小于约180nm,以避免sic层中的应变。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。