1.本发明涉及信号检测领域,特别是涉及基于直接序列扩频信号的检测及处理,包括且不限于扩频体制雷达信号处理、遥测接收等应用场景。

背景技术:

2.从信号体制上说,基于直接序列扩频的伪码调相信号的模糊图为图钉型,具有单一的中心峰值,均匀的旁瓣,因此具有很高的距离和多普勒分辨率,距离和多普勒模糊小,旁瓣抑制好,在雷达等信号检测系统中,与传统多普勒脉冲体制相比,可有效解决距离与速度耦合问题,提高检测效率。

3.但同时,直接序列扩频匹配滤波器由于硬件资源消耗巨大,多普勒容限小,在高阶直接序列扩频体制中,容易产生硬件规模需求大及检测中多普勒失配等问题,从而导致检测差损大,漏警率高等问题,在工程实现上不具有现实可用性。

4.为解决上述技术问题,本发明采用了一种基于高折叠率设计的直接序列扩频多通道匹配滤波器,包括折叠式相关器及多抽头并行通道匹配电路,其特征在于对直接序列扩频信号采用高折叠率及多通道设计进行匹配滤波。通过上述方式,本发明在高阶直接序列扩频信号检测处理上,硬件资源消耗合理,动态能力强。解决了传统方式由于直接序列扩频匹配滤波处理硬件资源消耗巨大,多普勒失配等缺陷而难以工程实现的问题。

技术实现要素:

5.本发明主要解决的技术问题是提供一种基于高折叠率设计的直接序列扩频多通道匹配滤波器,能够解决传统方式由于直接序列扩频匹配滤波处理硬件资源消耗巨大,多普勒失配等缺陷而难以工程实现的问题。

6.为解决上述技术问题,本发明采用的一个技术方案是:提供一种基于高折叠率设计的直接序列扩频多通道匹配滤波器,包括折叠式相关器及多抽头并行通道匹配电路,对高阶直接序列扩频信号采用4、8...最高至64倍的折叠相关处理,对每折叠段采用分段匹配,输出抽头进行矢量旋转,形成多通道匹配滤波输出。

7.与传统方式相比,采用本发明所述设计方案,可以达到以下技术效果:

8.1、本发明硬件资源消耗合理,采用高折叠率匹配滤波及多抽头多相变频方式,较简单并行处理实现方式降低了90%以上,具备工程实现性;

9.2、本发明采用折叠抽头方式,低差损的多通道处理,可有效解决匹配相关的多普勒失配问题,可避免传统多普勒脉冲方式距离速度模糊度问题,实现单脉冲测距及测速。

附图说明

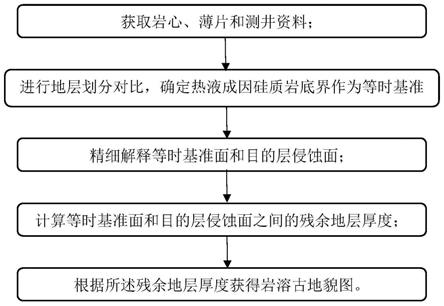

10.图1是本发明一种基于高折叠率设计的直接序列扩频多通道匹配滤波器结构示意图;

11.图2是本发明中高折叠率匹配滤波器结构示意图;

12.图3是本发明中多相数字变频器结构示意图;

13.附图中各部件的标记如下:

14.1、一次脉冲压缩处理器-n折叠匹配滤波;

15.2、输入直接序列扩频零中频信号实部;

16.3、输入直接序列扩频零中频信号虚部;

17.4、匹配滤波器输出实部;

18.5、匹配滤波器输出虚部;

19.6、匹配滤波器时序输出寄存器;

20.7、匹配滤波器时序输出实部;

21.8、匹配滤波器时序输出虚部;

22.9、第一通道多相数字变频器;

23.10、第二通道多相数字变频器;

24.11、第m通道多相数字变频器;

25.12、第一通道多相数字变频器输出实部;

26.13、第一通道多相数字变频器输出虚部;

27.14、第m通道多相数字变频器输出实部;

28.15、第m通道多相字变频器输出虚部;

29.16、第一通道二次脉冲压缩处理器;

30.17、第二通道二次脉冲压缩处理器;

31.18、第m通道二次脉冲压缩处理器;

32.19、第一通道匹配滤波输出实部;

33.20、第一通道匹配滤波输出虚部;

34.21、第二通道匹配滤波输出实部;

35.22、第二通道匹配滤波输出虚部;

36.23、第m通道匹配滤波输出实部;

37.24、第m通道匹配滤波输出虚部;

38.25、n折叠匹配滤波器输入;

39.26、第一移位寄存器;

40.27、第二移位寄存器;

41.28、第k移位寄存器;

42.29、0相关系数寄存器;

43.30、k相关系数寄存器

44.31、(n-1)k相关系数寄存器;

45.32、k-1相关系数寄存器;

46.33、2k-1相关系数寄存器;

47.34、nk-1相关系数寄存器;

48.35、1相关乘法器;

49.36、k相关乘法器;

50.37、树状结构加法器;

51.38、匹配滤波输出;

52.39、固定系数复数乘法器;

53.40、直接数字频率综合器;

54.41、16相位查找表;

55.42、频率及相位控制输入;

56.43、多相变频器输入实部;

57.44、多相变频器输入虚部;

58.45、多相变频器输出实部;

59.46、多相变频器输出虚部。

具体实施方式

60.下面结合附图对本发明的实现进行详细阐述,以使本发明的优点和特征能更易于被本领域技术人员理解,从而对本发明的保护范围做出更为清楚明确的界定。

61.参阅图1,本发明由一次脉冲压缩处理器-n折叠匹配滤波(1),n折叠匹配滤波器时序输出寄存器(6),m通道多相数字变频器(9、10,11),m通道二次脉冲压缩处理器(16、17,18)级联构成。

62.输入直接序列扩频零中频信号(2,3)经过一次脉冲压缩处理器-n折叠匹配滤波(1),以折叠段为单位获得匹配滤波器输出(4,5),经过匹配滤波器时序输出寄存器(6),完成时序控制。匹配滤波器时序输出(7,8)复用到m通道多相数字变频器(9,10,11),m通道多相数字变频器根据设置频率和初相完成矢量旋转并以折叠段为单位输出。多相数字变频器输出(12,13,14,15)经过m通道二次脉冲压缩处理器(16,17,18),实现对直接序列扩频信号的多通道匹配滤波,最后结果为m通道匹配滤波输出(19,20,21,22,23,24)。

63.本发明主要核心模块为一次脉冲压缩处理器-n折叠匹配滤波(1)及多相数字变频器(9,10,11)。

64.参阅图2,一次脉冲压缩处理器-n折叠匹配滤波由k个移位寄存器(26,27,28),n

×

k个相关系数寄存器(29,30,31,32,33,34),k个相关乘法器(35,36),树状结构加法器(37)及相应的适应高折叠率的时序控制模块组成。

65.n折叠匹配滤波器输入(35)以采样率为周期顺序进入移位寄存器(26,27,28),在无外部输入的情况下,以系统时钟周期对k个移位寄存器(26,27,28)的数据进行循环移位,相关系数寄存器(29,30,31,32,33,34)分为k组向下做循环移位,与k个移位寄存器(26,27,28)中的采样数据通过相关乘法器(35,36)进行相关处理,经过树状结构加法器(37)输出匹配滤波数据。

66.以10阶直接序列扩频信号为例,与传统直接匹配方式相比,采用14比特量化,折叠率为8的实现方式,寄存器及查找表消耗均降为25%以下。采用14比特量化,折叠率为16的实现方式,寄存器及查找表消耗均降为15%以下。

67.参阅图3,多相数字变频器由固定系数复数乘法器(39),直接数字频率综合器(40),16相位查找表(41)模块组成,通过频率及相位控制输入(42),直接数字频率综合器(40)产生当前频移载波相位,通过16相位查找表(41),获取变频所需的固定系数,多相变频器输入(43,44)经过固定系数复数乘法器(39)处理实现低延迟的多相变频器输出(45,46)。

68.该多相变频器有消耗资源低,实时性高,差损小等优点,对实现硬件平台的数字信号处理硬件内核无要求。

69.本发明结合上述一次脉冲压缩处理器-n折叠匹配滤波及多相数字变频器,实现实时多通道匹配处理,物理上仅需一套匹配滤波器硬件,在8通道以上处理需求中,较简单并行处理实现方式硬件资源降低了90%以上,具备工程实现性。同时,可扩展的多通道数量及频率间隔设计,可满足多普勒适配及测量要求。

70.以上所述仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。