技术特征:

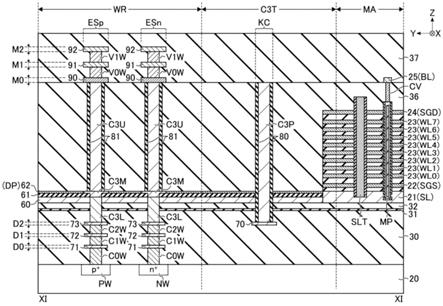

1.一种半导体存储装置,具备:衬底,具有核心区域及以包围所述核心区域外周的方式设置的第1区域;源极线,在所述核心区域设置在所述衬底的上方;多个字线,在所述核心区域设置在所述源极线的上方,并在与所述衬底的表面交叉的第1方向上相互分开地设置;柱,在所述核心区域中在所述第1方向上延伸设置,底部到达所述源极线,且与所述字线的交叉部分作为存储单元发挥功能;外周导电体层,在所述第1区域以包围所述核心区域的方式设置,且包含在具备所述源极线的第1层中;下层导电体层,设置在所述第1区域,且包含在所述第1层与所述衬底之间的第2层中;以及第1接点层,在所述第1区域以包围所述核心区域的方式设置在所述下层导电体层之上,上端包含在所述第1层中,并与所述外周导电体层电连接。2.根据权利要求1所述的半导体存储装置,其中所述外周导电体层与所述源极线之间电绝缘。3.根据权利要求1所述的半导体存储装置,其中所述外周导电体层包含第1外周导电体层及第2外周导电体层,所述第1外周导电体层及所述第2外周导电体层在所述第1方向上相互分开地设置,且所述第1接点将下层侧的所述第1外周导电体层分断并在所述第1方向上延伸,所述第1接点的上端与上层侧的所述第2外周导电体层的底面接触。4.根据权利要求3所述的半导体存储装置,其还具备:第1绝缘体层,跨及所述核心区域及所述第1区域,设置在所述第1层与所述第2层之间的第3层,且由所述第1接点分断;以及第2绝缘体层,设置在所述第1接点的侧面,并与所述第1绝缘体层接触;且所述第1绝缘体层及所述第2绝缘体层分别含有氮化硅。5.根据权利要求1所述的半导体存储装置,其中所述外周导电体层包含第1外周导电体层及第2外周导电体层,所述第1外周导电体层及所述第2外周导电体层在所述第1方向上相互分开地设置,在所述第1外周导电体层及所述第2外周导电体层之间具备绝缘体层,所述柱包含在所述第1方向上延伸设置的半导体,且所述半导体在设置着所述绝缘体层的高度处,与所述源极线接触。6.根据权利要求1所述的半导体存储装置,其中与所述第1接点的上端邻接的所述第1接点的侧面部分与所述外周导电体层接触。7.根据权利要求1所述的半导体存储装置,其还具备第2接点,所述第2接点在所述第1区域以包围所述核心区域的方式设置在所述第1接点的上方,且所述第2接点的上端包含在比所述柱的上端更靠上层处。8.根据权利要求7所述的半导体存储装置,其还具备中间接点,所述中间接点在所述第1区域以包围所述核心区域的方式设置在所述第1接点与所述第2接点之间,且与所述中间接点的上端邻接的所述中间接点的侧面部分与所述外周导电体层接触,在所述第1接点与所述中间接点的接触部分,所述第1接点的侧面与所述中间接点的侧面对齐设置,且

相比所述第1接点与所述中间接点的接触部分中所述中间接点的所述第2方向的宽度,所述中间接点与所述外周导电体层的接触部分中所述中间接点的与所述第1方向交叉的第2方向的宽度更大。9.根据权利要求1所述的半导体存储装置,其中所述衬底在所述第1区域包含p型阱区域及形成在所述p型阱区域的n型杂质扩散区域,且所述下层导电体层电连接于所述n型杂质扩散区域。10.根据权利要求9所述的半导体存储装置,其中所述衬底还具有设置在所述核心区域与所述第1区域之间的第2区域,且所述外周导电体层经由所述第1区域的一部分连接于所述源极线。11.根据权利要求1所述的半导体存储装置,其中所述第1接点设置为四角环状。12.根据权利要求1所述的半导体存储装置,其还具备设置在所述衬底与所述源极线之间的周边电路,且所述周边电路用于控制所述存储单元。13.一种半导体存储装置,具备:衬底,具有核心区域及以包围所述核心区域外周的方式设置的第1区域;源极线,在所述核心区域设置在所述衬底的上方;多个字线,在所述核心区域设置在所述源极线的上方,并在与所述衬底的表面交叉的第1方向上相互分开地设置;柱,在所述核心区域中在所述第1方向上延伸设置,底部到达所述源极线,且与所述字线的交叉部分作为存储单元发挥功能;外周导电体层,在所述第1区域以包围所述核心区域的方式设置,且包含在具备所述源极线的第1层中;第1下层导电体层,在所述第1区域以包围所述核心区域的方式设置,且包含在所述第1层与所述衬底之间的第2层中,第1下层接点,在所述第1区域以包围所述核心区域的方式设置在所述衬底与所述第1下层导电体层之间,且将与所述衬底之间电连接;第2下层导电体层,在所述第1区域设置在比所述第1下层导电体层更靠近所述核心区域处,且包含在所述第2层中;第2下层接点,在所述第1区域以与所述第1下层接点相同的高度设置在所述衬底与所述第2下层导电体层之间,且所述第2下层接点将所述衬底与所述第2下层导电体层之间电连接;以及第1接点,在所述第1区域设置在所述第2下层导电体层之上,上端包含在所述第1层中,且与所述外周导电体层电连接。14.根据权利要求13所述的半导体存储装置,其中所述衬底与所述第1下层导电体层之间的层构造和所述衬底与所述第2下层导电体层之间的层构造相同。15.根据权利要求13所述的半导体存储装置,其还具备第2接点,所述第2接点在所述第1区域以包围所述核心区域的方式设置在所述第1下层导电体层之上,所述第2接点的上端包含在比所述柱的上端更靠上层处,且所述第2接点与所述外周导电体层电绝缘。16.根据权利要求13所述的半导体存储装置,其还具备第3接点,所述第3接点在所述第1区域以包围所述核心区域的方式设置在所述第1下层导电体层之上,上端包含在所述第1

层中,且与所述外周导电体层电连接,且所述外周导电体层与所述源极线之间电绝缘。17.根据权利要求13所述的半导体存储装置,其中所述衬底在所述第1区域中,包含p型阱区域及形成在所述p型阱区域的n型杂质扩散区域,且所述第2下层接点电连接于所述n型杂质扩散区域。18.根据权利要求13所述的半导体存储装置,其中所述第1接点设置为四角环状。19.根据权利要求13所述的半导体存储装置,其还具备周边电路,所述周边电路设置在所述衬底与所述源极线之间,且用于控制所述存储单元。20.根据权利要求18所述的半导体存储装置,其中所述第2下层导电体层及所述第2下层接点设置为四角环状。

技术总结

实施方式的半导体存储装置包含衬底(20)、源极线(SL)、多个字线(WL)、柱(MP)、外周导电体层(62)、下层导电体层(73)、及第1接点(C3L)。源极线(SL)在核心区域(MA)中设置在衬底(20)的上方。柱(MP)的底部到达源极线(SL),与多个字线(WL)的交叉部分分别作为存储单元发挥功能。外周导电体层(62)在第1区域(WR)中包含在具备源极线(SL)的第1层中,且以包围核心区域(MA)的方式设置。下层导电体层(73)在第1区域(WR)中包含在第2层(D2)中。第1接点(C3L)在第1区域(WR)以包围核心区域(MA)的方式设置在下层导电体层(73)之上,上端包含在第1层中,且与外周导电体层(62)电连接。导电体层(62)电连接。导电体层(62)电连接。

技术研发人员:渡会亜友美 岩崎太一 松浦修武 广津佑 松本壮太

受保护的技术使用者:铠侠股份有限公司

技术研发日:2021.03.08

技术公布日:2022/3/18

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。