半导体存储器设备

1.本技术是申请日为2017年10月10日,申请号为201710935388.8,发明名称为“半导体存储器设备”的专利申请的分案申请。

技术领域

2.各个实施例总体涉及一种半导体集成电路,更特别地,涉及一种半导体存储器设备。

背景技术:

3.半导体存储器设备被配置成存储数据并输出所存储的数据。

4.半导体存储器设备中存储数据的存储器单元可根据其特征而具有不同的保留所存储的数据的时间。

5.在相同条件下读出和放大具有不同特征的存储器单元是效率低的。

技术实现要素:

6.在实施例中,半导体存储器设备可包括:驱动电压提供电路,其适于响应于激活信号、单元特征信息信号和预充电信号将第一驱动电压、第二驱动电压、第三驱动电压、接地电压和预充电电压选择性地提供给第一驱动线和第二驱动线;以及读出放大器,其适于通过被施加从第一驱动线和第二驱动线提供的电压进行操作。

7.在实施例中,半导体存储器设备可包括:多个垫(mat);多个读出放大器,其分别与多个垫电联接;以及多个驱动电压提供电路,其适于响应于多个单元特征信息信号分别将驱动电压选择性地提供给多个读出放大器。

附图说明

8.图1是示出根据实施例的半导体存储器设备的示例的表示的配置图。

9.图2是示出图1所示的电压提供电路的示例的表示的配置图。

10.图3是示出图1所示的预充电电压生成电路的示例的表示的配置图。

11.图4是示出根据实施例的半导体存储器设备的示例的表示的配置图。

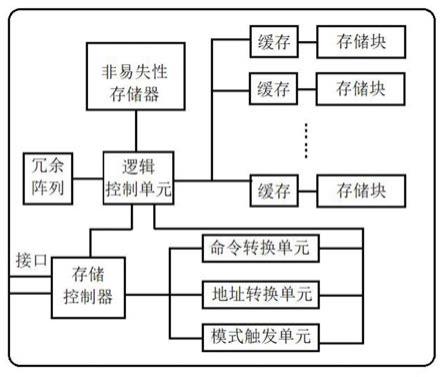

12.图5示出采用根据以上关于图1至图4讨论的各个实施例的半导体存储器设备的系统的表示的示例的框图。

具体实施方式

13.在下文中,将通过实施例的各个示例参照附图描述半导体存储器设备。

14.如图1所示,根据实施例的半导体存储器设备可包括驱动电压提供电路100、单元特征信息存储电路200、预充电电压生成电路300以及读出放大器400。

15.驱动电压提供电路100可响应于激活信号act、单元特征信息信号c_inf和预充电信号pcg中的至少一个将第一驱动电压v_a、第二驱动电压v_b、第三驱动电压v_c、接地电压

vss和预充电电压v_pcg中的至少一个选择性地施加到第一驱动线rto和第二驱动线sb中的至少一个。例如,驱动电压提供电路100可响应于激活信号act和单元特征信息信号c_inf将第一至第三驱动电压v_a、v_b和v_c中的两个驱动电压选择性地提供给第一驱动线rto,并将接地电压vss提供给第二驱动线sb。驱动电压提供电路100可响应于预充电信号pcg将预充电电压v_pcg提供给第一驱动线rto和第二驱动线sb。第一驱动电压v_a可以是第一外部电压(vdd),第二驱动电压v_b可以是内核电压(vcore),第三驱动电压v_c可以是第二外部电压(vsod)。第一驱动电压v_a可等于或高于第二驱动电压v_b的电压电平。第三驱动电压v_c可等于或高于第一驱动电压v_a的电压电平。第三驱动电压v_c可高于第二驱动电压v_b的电压电平。

16.驱动电压提供电路100可包括控制信号生成电路110、电压选择信号生成电路120和电压提供电路130。

17.控制信号生成电路110可响应于激活信号act生成第一读出放大器驱动控制信号sap1、第二读出放大器驱动控制信号sap2和第三读出放大器驱动控制信号san。例如,如果激活信号act被启用,则控制信号生成电路110使第一读出放大器驱动控制信号sap1在第一预定时间启用,并且当第一读出放大器驱动控制信号sap1被禁用时,控制信号生成电路110使第二读出放大器驱动控制信号sap2在第二预定时间启用。控制信号生成电路110使第三读出放大器驱动控制信号san在第一读出放大器驱动控制信号sap1和第二读出放大器驱动控制信号sap2中的至少一个被启用的期间启用。也就是说,控制信号生成电路110使第三读出放大器驱动控制信号san在通过将第一预定时间和第二预定时间相加而获得的时间中启用。

18.电压选择信号生成电路120可响应于单元特征信息信号c_inf将第二读出放大器驱动控制信号sap2输出为第一电压选择信号v_sel1和第二电压选择信号v_sel2中的一个。例如,当单元特征信息信号c_inf被启用时,电压选择信号生成电路120可将第二读出放大器驱动控制信号sap2输出为第一电压选择信号v_sel1,并且当单元特征信息信号c_inf被禁用时,电压选择信号生成电路120可将第二读出放大器驱动控制信号sap2输出为第二电压选择信号v_sel2。电压选择信号生成电路120可包括多路器。

19.电压提供电路130可响应于第一和第三读出放大器驱动控制信号sap1和san、第一和第二电压选择信号v_sel1和v_sel2以及预充电信号pcg中的至少一个将第一至第三驱动电压v_a、v_b和v_c、接地电压vss和预充电电压v_pcg中的至少一个选择性地提供给第一驱动线rto和第二驱动线sb中的至少一个。例如,在第一读出放大器驱动控制信号sap1的启用期间,电压提供电路130可将第一驱动电压v_a提供给第一驱动线rto。电压提供电路130可响应于第三读出放大器驱动控制信号san和预充电信号pcg将接地电压vss和预充电电压v_pcg施加到第二驱动线sb。在第一电压选择信号v_sel1的启用期间,电压提供电路130可将第二驱动电压v_b提供给第一驱动线rto。在第二电压选择信号v_sel2的启用期间,电压提供电路130可将第三驱动电压v_c提供给第一驱动线rto。在预充电信号pcg的启用期间,电压提供电路130可将预充电电压v_pcg提供给第一驱动线rto和第二驱动线sb。

20.单元特征信息存储电路200可存储和提供根据存储器单元的特征的信息作为单元特征信息信号c_inf。单元特征信息存储电路200可包括根据存储器单元的特征确定是否切断熔丝并根据熔丝是否被切断而生成单元特征信息信号c_inf的熔丝电路。单元特征信息

存储电路200可包括存储根据存储器单元的特征的信息作为单元特征信息信号c_inf的寄存器电路。存储器单元的特征可表示存储器单元能够保留数据的时间是长于参考时间还是短于参考时间。例如,当存储器单元的数据保留时间长于参考时间时,单元特征信息存储电路200被配置成启用单元特征信息信号c_inf。当存储器单元的数据保留时间短于参考时间时,单元特征信息存储电路200被配置成禁用单元特征信息信号c_inf。

21.预充电电压生成电路300可响应于单元特征信息信号c_inf选择预充电电压v_pcg的电压电平。例如,当单元特征信息信号c_inf被禁用时,预充电电压生成电路300可生成电压电平比当单元特征信息信号c_inf被启用时更高的预充电电压v_pcg。因此,当单元特征信息信号c_inf被启用时,预充电电压生成电路300可生成电压电平比当单元特征信息信号c_inf被禁用时更低的预充电电压v_pcg。

22.读出放大器400可通过被提供有从第一驱动线rto和第二驱动线sb传输的电压进行操作。

23.如图2所示,电压提供电路130可包括第一电压施加电路131、第二电压施加电路132、第三电压施加电路133、第四电压施加电路134和预充电电压施加电路135。

24.当第一读出放大器驱动控制信号sap1被启用时,第一电压施加电路131可将第一驱动电压v_a施加到第一驱动线rto。

25.第一电压施加电路131可包括第一晶体管n1。第一晶体管n1具有被输入有第一读出放大器驱动控制信号sap1的栅极、被施加有第一驱动电压v_a的漏极和与第一驱动线rto联接的源极。

26.当第一电压选择信号v_sel1被启用时,第二电压施加电路132可将第二驱动电压v_b施加到第一驱动线rto。

27.第二电压施加电路132可包括第二晶体管n2。第二晶体管n2具有被输入有第一电压选择信号v_sel1的栅极、被施加有第二驱动电压v_b的漏极和与第一驱动线rto联接的源极。

28.当第二电压选择信号v_sel2被启用时,第三电压施加电路133可将第三驱动电压v_c施加到第一驱动线rto。

29.第三电压施加电路133可包括第三晶体管n3。第三晶体管n3具有被输入有第二电压选择信号v_sel2的栅极、被施加有第三驱动电压v_c的漏极和与第一驱动线rto联接的源极。

30.当第三读出放大器驱动控制信号san被启用时,第四电压施加电路134可将接地电压vss施加到第二驱动线sb。

31.第四电压施加电路134可包括第四晶体管n4。第四晶体管n4具有被输入有第三读出放大器驱动控制信号san的栅极、与第二驱动线sb联接的漏极和被施加有接地电压vss的源极。

32.当预充电信号pcg被启用时,预充电电压施加电路135可联接第一驱动线rto和第二驱动线sb,并将预充电电压v_pcg施加到第一驱动线rto和第二驱动线sb。

33.预充电电压施加电路135可包括第五至第七晶体管n5、n6和n7。第五晶体管n5具有被输入有预充电信号pcg的栅极、与第一驱动线rto联接的漏极和与第二驱动线sb联接的源极。第六晶体管n6具有被输入有预充电信号pcg的栅极、被施加有预充电电压v_pcg的漏极

和与第一驱动线rto联接的源极。第七晶体管n7具有被输入有预充电信号pcg的栅极、被施加有预充电电压v_pcg的漏极和与第二驱动线sb联接的源极。

34.如图3所示,预充电电压生成电路300可包括第一预先预充电电压生成电路310、第二预先预充电电压生成电路320和电压选择输出电路330。

35.第一预先预充电电压生成电路310可生成电压电平低于第二驱动电压v_b的电压电平的第一预先预充电电压v_pcgp1。例如,第一预先预充电电压生成电路310可生成具有对应于第二驱动电压v_b的电压电平的1/2的电压电平的第一预先预充电电压v_pcgp1。

36.第一预先预充电电压生成电路310可包括第一参考电压生成电路311和第一预电压生成电路312。

37.第一参考电压生成电路311可生成电压电平低于第二驱动电压v_b的电压电平的第一参考电压v_ref1。例如,第一参考电压生成电路311可生成具有对应于第二驱动电压v_b的电压电平的1/2的电压电平的第一参考电压v_ref1。

38.第一参考电压生成电路311可包括第一电阻元件r1和第二电阻元件r2。第一电阻元件r1的一端被施加有第二驱动电压v_b。第二电阻元件r2的一端与第一电阻元件r1的另一端联接,第二电阻元件r2的另一端与接地电压vss的端子联接。第一参考电压v_ref1从与第一电阻元件r1和第二电阻元件r2联接的节点输出。第一电阻元件r1和第二电阻元件r2的电阻水平可相同。

39.第一预电压生成电路312可生成对应于第一参考电压v_ref1的电压电平的第一预先预充电电压v_pcgp1。例如,第一预电压生成电路312可生成电压电平与第一参考电压v_ref1的电压电平相同的第一预先预充电电压v_pcgp1。

40.第二预先预充电电压生成电路320可生成电压电平低于第三驱动电压v_c的电压电平的第二预先预充电电压v_pcgp2。例如,第二预先预充电电压生成电路320可生成具有对应于第三驱动电压v_c的电压电平的1/2的电压电平的第二预先预充电电压v_pcgp2。

41.第二预先预充电电压生成电路320可包括第二参考电压生成电路321和第二预电压生成电路322。

42.第二参考电压生成电路321可生成电压电平低于第三驱动电压v_c的电压电平的第二参考电压v_ref2。例如,第二参考电压生成电路321可生成具有对应于第三驱动电压v_c的电压电平的1/2的电压电平的第二参考电压v_ref2。

43.第二参考电压生成电路321可包括第三电阻元件r3和第四电阻元件r4。第三电阻元件r3的一端被施加有第三驱动电压v_c。第四电阻元件r4的一端与第三电阻元件r3的另一端联接,第四电阻元件r4的另一端与接地电压vss的端子联接。第二参考电压v_ref2从与第三电阻元件r3和第四电阻元件r4联接的节点输出。第三电阻元件r3和第四电阻元件r4的电阻水平可相同。

44.第二预电压生成电路322可生成对应于第二参考电压v_ref2的电压电平的第二预先预充电电压v_pcgp2。例如,第二预电压生成电路322可生成电压电平与第二参考电压v_ref2的电压电平相同的第二预先预充电电压v_pcgp2。

45.电压选择输出电路330可响应于单元特征信息信号c_inf输出第一预先预充电电压v_pcgp1和第二预先预充电电压v_pcgp2中的一个电压作为预充电电压v_pcg。例如,当单元特征信息信号c_inf被启用时,电压选择输出电路330可输出第一预先预充电电压v_

pcgp1作为预充电电压v_pcg。当单元特征信息信号c_inf被禁用时,电压选择输出电路330可输出第二预先预充电电压v_pcgp2作为预充电电压v_pcg。

46.下面将描述根据实施例的如上述所配置的半导体存储器设备的操作。

47.如果存储器单元能够将数据保留长于参考时间的时间,则单元特征信息存储电路200可提供启用的单元特征信息信号c_inf。

48.如果激活信号act被启用,则控制信号生成电路110可使第一读出放大器驱动控制信号sap1在第一预定时间启用,并且当第一读出放大器驱动控制信号sap1被禁用时,控制信号生成电路110可使第二读出放大器驱动控制信号sap2在第二预定时间启用。控制信号生成电路110可使第三读出放大器驱动控制信号san在第一读出放大器驱动控制信号sap1和第二读出放大器驱动控制信号sap2中的一个被启用的期间启用。

49.电压选择信号生成电路120可响应于启用的单元特征信息信号c_inf将第二读出放大器驱动控制信号sap2输出为第一电压选择信号v_sel1。

50.在第一读出放大器驱动控制信号sap1的启用期间,电压提供电路130可将第一驱动电压v_a施加到第一驱动线rto。在第一电压选择信号v_sel1的启用期间,电压提供电路130可将第二驱动电压v_b施加到第一驱动线rto。在第三读出放大器驱动控制信号san的启用期间,电压提供电路130可将接地电压vss施加到第二驱动线sb。在预充电信号pcg的启用期间,电压提供电路130可将预充电电压v_pcg施加到第一驱动线rto和第二驱动线sb。

51.预充电电压生成电路300可响应于启用的单元特征信息信号c_inf将电压电平比当单元特征信息信号c_inf被禁用时更低的预充电电压v_pcg提供给电压提供电路130。

52.读出放大器400可通过被施加有通过第一驱动线rto和第二驱动线sb施加的电压进行操作。

53.如果存储器单元能够将数据保留短于参考时间的时间,则单元特征信息存储电路200可提供禁用的单元特征信息信号c_inf。

54.如果激活信号act被启用,则控制信号生成电路110可使第一读出放大器驱动控制信号sap1在第一预定时间启用,并且当第一读出放大器驱动控制信号sap1被禁用时,控制信号生成电路110可使第二读出放大器驱动控制信号sap2在第二预定时间启用。控制信号生成电路110可使第三读出放大器驱动控制信号san在第一读出放大器驱动控制信号sap1和第二读出放大器驱动控制信号sap2中的一个被启用的期间启用。

55.电压选择信号生成电路120可响应于禁用的单元特征信息信号c_inf将第二读出放大器驱动控制信号sap2输出为第二电压选择信号v_sel2。

56.在第一读出放大器驱动控制信号sap1的启用期间,电压提供电路130可将第一驱动电压v_a施加到第一驱动线rto。在第二电压选择信号v_sel2的启用期间,电压提供电路130可将第三驱动电压v_c施加到第一驱动线rto。在第三读出放大器驱动控制信号san的启用期间,电压提供电路130可将接地电压vss施加到第二驱动线sb。在预充电信号pcg的启用期间,电压提供电路130可将预充电电压v_pcg施加到第一驱动线rto和第二驱动线sb。

57.预充电电压生成电路300可响应于禁用的单元特征信息信号c_inf将电压电平比当单元特征信息信号c_inf被启用时更高的预充电电压v_pcg提供给电压提供电路130。

58.读出放大器400可通过被施加有通过第一驱动线rto和第二驱动线sb施加的电压进行操作。

59.根据实施例的半导体存储器设备可响应于单元特征信息信号c_inf来确定在第二读出放大器驱动控制信号sap2的启用期间待提供给读出放大器400的电压电平。也就是说,因为第二驱动电压v_b比第三驱动电压v_c的电压电平低,所以当单元特征信息信号c_inf被启用时,可通过第一驱动线rto将电压电平比当单元特征信息信号c_inf被禁用时更低的电压提供给读出放大器400。

60.因此,与当存储器单元在第二读出放大器驱动控制信号sap2的启用期间内将数据保留比参考时间短的时间时相比较,当存储器单元能够在第二读出放大器驱动控制信号sap2的启用期间内将数据保留比参考时间长的时间时,根据实施例的半导体存储器设备可将更低的电压电平的电压提供给读出放大器。

61.与当存储器单元在第二读出放大器驱动控制信号sap2的启用期间内将数据保留比参考时间长的时间时相比较,当存储器单元在第二读出放大器驱动控制信号sap2的启用期间内将数据保留比参考时间短的时间时,根据实施例的半导体存储器设备可将更高的电压电平的电压提供给读出放大器。

62.如图4所示,根据实施例的半导体存储器设备可包括第一至第三驱动电压提供电路100-1、100-2和100-3,单元特征信息存储电路200-1,第一至第三预充电电压生成电路300-1、300-2和300-3,第一至第三读出放大器400-1、400-2和400-3,以及第一至第三垫500-1、500-2和500-3。第一至第三驱动电压提供电路100-1、100-2和100-3中的每一个可以与图1的驱动电压提供电路100基本相似的方式配置,并且第一至第三预充电电压生成电路300-1、300-2和300-3中的每一个可以与图3所示的基本相似的方式配置。

63.第一垫500-1可与第一读出放大器400-1电联接,第一读出放大器400-1可与第一驱动电压提供电路100-1电联接,并且第一预充电电压生成电路300-1可与第一驱动电压提供电路100-1电联接。

64.第二垫500-2可与第二读出放大器400-2电联接,第二读出放大器400-2可与第二驱动电压提供电路100-2电联接,并且第二预充电电压生成电路300-2可与第二驱动电压提供电路100-2电联接。

65.第三垫500-3可与第三读出放大器400-3电联接,第三读出放大器400-3可与第三驱动电压提供电路100-3电联接,并且第三预充电电压生成电路300-3可与第三驱动电压提供电路100-3电联接。

66.单元特征信息存储电路200-1可存储关于被包括在第一垫500-1中的存储器单元的特征的信息作为第一单元特征信息信号c_inf1。单元特征信息存储电路200-1可存储关于被包括在第二垫500-2中的存储器单元的特征的信息作为第二单元特征信息信号c_inf2。单元特征信息存储电路200-1可存储关于被包括在第三垫500-3中的存储器单元的特征的信息作为第三单元特征信息信号c_inf3。单元特征信息存储电路200-1可将第一单元特征信息信号c_inf1提供给第一驱动电压提供电路100-1和第一预充电电压生成电路300-1。单元特征信息存储电路200-1可将第二单元特征信息信号c_inf2提供给第二驱动电压提供电路100-2和第二预充电电压生成电路300-2。单元特征信息存储电路200-1可将第三单元特征信息信号c_inf3提供给第三驱动电压提供电路100-3和第三预充电电压生成电路300-3。

67.例如,如果第一至第三单元特征信息信号c_inf1、c_inf2和c_inf3具有相同的信

息,即具有相同的电平,则各个第一至第三驱动电压提供电路100-1、100-2和100-3可通过驱动线rto1、sb1、rto2、sb2、rto3和sb3将相同电平的驱动电压选择性地提供给各个第一至第三读出放大器400-1、400-2和400-3,并且各个第一至第三预充电电压生成电路300-1、300-2、300-3可通过驱动线rto1、sb1、rto2、sb2、rto3和sb3将相同电平的预充电电压提供给各个第一至第三读出放大器400-1、400-2和400-3。进一步地,当相应的单元特征信息信号被启用时,各个第一至第三驱动电压提供电路100-1、100-2和100-3中的每一个可提供电平比当相应的单元特征信息信号被禁用时更低的驱动电压。

68.如果在第一至第三单元特征信息信号c_inf1、c_inf2和c_inf3中存在包括不同信息的信号,即存在具有与其它信号不同的电平的信号,则被输入有不同电平的单元特征信息信号的驱动电压提供电路和预充电电压生成电路将电平与其它驱动电压提供电路和其它预充电电压生成电路不同的驱动电压和预充电电压提供给相应的读出放大器。第一至第三预充电电压生成电路300-1、300-2和300-3可响应于各个单元特征信息信号c_inf1、c_inf2和c_inf3来确定电压电平,并将所确定电压电平的预充电电压分别输出到驱动电压提供电路100-1、100-2和100-3。进一步地,当相应的单元特征信息信号c_inf1、c_inf2和c_inf3中的至少一个被启用时,第一至第三预充电电压生成电路300-1、300-2和300-3中的每一个可生成电压电平比当相应的单元特征信息信号c_inf1、c_inf2和c_inf3被禁用时更低的预充电电压。

69.因此,单元特征信息存储电路200-1可将根据被包括在第一至第三垫500-1、500-2和500-3中的存储器单元的特征的不同电压电平的电压传输至各个读出放大器400-1、400-2和400-3。

70.尽管上面已经描述了各种实施例,但是本领域技术人员将理解,所描述的实施例仅为示例。因此,本文所述的半导体存储器设备不应基于所描述的实施例被限制。

71.上述半导体存储器设备(参见图1-4)在存储器装置、处理器和计算机系统的设计中特别有用。例如,参照图5,示出了采用根据各个实施例的半导体存储器设备的系统的框图,并且一般用附图标记1000表示。系统1000可包括一个或多个处理器(即,处理器)或例如但不限于中央处理单元(“cpu”)1100。处理器(即,cpu)1100可被单独使用或与其他处理器(即,cpu)组合使用。虽然处理器(即,cpu)1100将主要以单数来表示,但是本领域技术人员将理解的是,可实施具有任何数量的物理或逻辑处理器(即,cpu)的系统1000。

72.芯片组1150可以可操作地联接到处理器(即,cpu)1100。芯片组1150是用于处理器(即,cpu)1100和系统1000的其他部件之间的信号的通信路径。系统1000的其他部件可包括存储器控制器1200、输入/输出(“i/o”)总线1250和磁盘驱动器控制器1300。根据系统1000的配置,多个不同信号中的任何一个可通过芯片组1150传输,并且本领域技术人员将理解,可以容易地调整遍及系统1000的信号的路由而不改变系统1000的基本特征。

73.如上所述,存储器控制器1200可以可操作地联接到芯片组1150。存储器控制器1200可包括至少一个如上文参照图1-4所讨论的半导体存储器设备。因此,存储器控制器1200可通过芯片组1150接收从处理器(即,cpu)1100提供的请求。在可选实施例中,存储器控制器1200可被集成到芯片组1150中。存储器控制器1200可以可操作地联接到一个或多个存储器装置1350。在实施例中,存储器装置1350可包括至少一个以上关于图1-4讨论的半导体存储器设备,存储器装置1350可包括用于限定多个存储器单元的多个字线和多个位线。

存储器装置1350可以是众多工业标准存储器类型中的任何一种,包括但不限于单列直插式存储器模块(“simm”)和双列直插式存储器模块(“dimm”)。此外,存储器装置1350可通过存储指令和数据两者来促进外部数据存储装置的安全移除。

74.芯片组1150还可联接到i/o总线1250。i/o总线1250可用作信号从芯片组1150到i/o装置1410、1420和1430的通信路径。i/o装置1410、1420和1430可包括例如但不限于鼠标1410、视频显示器1420或键盘1430。i/o总线1250可采用众多通信协议中的任何一个来与i/o装置1410、1420和1430进行通信。在实施例中,i/o总线1250可被集成到芯片组1150中。

75.磁盘驱动器控制器1300可以可操作地联接到芯片组1150。磁盘驱动器控制器1300可用作芯片组1150与一个内部磁盘驱动器1450或多个内部磁盘驱动器1450之间的通信路径。内部磁盘驱动器1450可通过存储指令和数据两者来促进外部数据存储装置的断开。磁盘驱动器控制器1300和内部磁盘驱动器1450可使用实际上任何类型的通信协议彼此通信或与芯片组1150进行通信,通信协议例如但不限于上文针对i/o总线1250所提到的所有协议。

76.重要的是注意到以上关于图5描述的系统1000仅是采用如上面关于图1-4讨论的半导体存储器设备的系统1000的一个示例。在可选实施例中,例如但不限于蜂窝电话或数码相机,部件可不同于图5所示的实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。