技术特征:

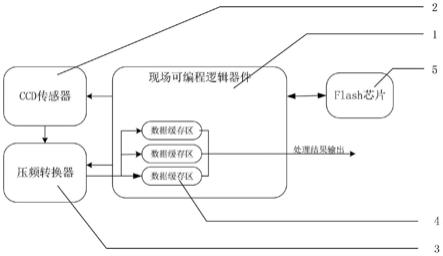

1.一种基于fpga实现光电ccd信号高速采集与处理的系统,包括一个fpga芯片(1)、ccd传感器(2)、压频转换器(3)和存储芯片(5);其特征在于:所述fpga芯片(1)连接ccd传感器(2)、压频转换器(3)和存储芯片(5),ccd传感器(2)连接压频转换器(3);所述fpga芯片(1)为ccd传感器(2)和压频转换器(3)提供时钟频率,保证时钟同步;fpga芯片(1)中的数据缓冲区(4),用于由压频转换器(3)输入fpga芯片(1)的数据处理前的数据缓存;fpga芯片(1)将接收到的数据存入数据缓冲区(4);fpga芯片(1)利用数据并行处理的特性,完成对压频转换器(3)输出数据的处理;存储芯片(5)用于存储程序,程序掉电不丢失。2.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述数据缓冲区(4)由所述fpga芯片(1)内部的嵌入式存储资源构成。3.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述fpga芯片(1)与pc机通过以太网或rs232进行通信。4.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述ccd传感器(2)通过fpga芯片可编程输入/输出(i/o)口与fpga芯片(1)相连。5.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述压频转换器(3)通过fpga芯片可编程输入/输出(i/o)口与fpga芯片(1)相连。6.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述压频转换器(3)通过数据总线与ccd传感器(2)相连。7.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述存储芯片(5)通过数据总线与fpga芯片(1)相连。8.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述fpga芯片(1)包括如下模块:ccd控制模块,用于生成ccd传感器(2)所需的时钟频率,产生ccd传感器(2)所需的控制信号;压频转换器(3)为vfc芯片ad7741,ad7741控制模块,用于生成压频转换器(3)所需的时钟频率,产生相应控制信号驱动压频转换器(3)工作;数据缓存读写控制模块:利用fpga芯片(1)内部ram资源生成fifo数据缓存器,管理读写指针和空满状态,对压频转换器(3)输出数据进行缓存或读取的控制,完成数据读取与写入的时序控制;数据处理模块,对数据缓存区读出的数据进行并行处理,将处理结果送至数据发送模块;数据发送模块,接收数据处理模块的处理结果,将其通过串行接口发至pc端;控制模块,将ccd控制模块、ad7741控制模块、数据缓存读写控制模块、数据处理模块、数据发送模块通过内部总线连接例化与信号引出。9.根据权利要求1所述的基于fpga实现光电ccd信号高速采集与处理的系统,其特征在于:所述数据处理模块输出结果包括一个采样周期内频率最小值及其索引,其中,所述一个采样周期内频率最小值为所述ccd传感器(2)输出模拟信号最小值,索引为所述fpga芯片(1)内部逻辑单元组成的计数器对应值。

技术总结

本发明公开了一种基于FPGA实现光电CCD信号高速采集与处理的系统,由设置于所述FPGA内部的控制模块,线性CCD以及VFC器件组成,通过线性CCD将光学信号转换为模拟电压信号,转换后的模拟电压信号经过VFC器件转换为频率信号,由FPGA芯片对频率信号进行并行信号处理,找出模拟信号数值最低点。本发明解决传统CCD数据采集与处理速度慢以及控制时序不精确的问题,充分利用FPGA的数据处理能力,提高了数据采集与处理的速度。该发明属于模拟数据高速采集与处理领域。采集与处理领域。采集与处理领域。

技术研发人员:杨庆华 刘洋 屠晓伟

受保护的技术使用者:上海大学

技术研发日:2021.11.02

技术公布日:2022/3/15

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。