1.本公开描述一种用于判断存储器系统读取电压的系统以及方法,例如三维非易失性存储器(non-volatile memory,nvm)系统,特别是具有晶载(on-chip)模数转换器(analog-to-digital converter,adc)电路,可快速以及有效率地判断用于读取存储器数据的校准读取电压,从而提升存储器系统的性能。

背景技术:

2.当对数据储存装置,例如一存储器系统中的存储单元进行了编程,通过将单元阈值电压与一个或多个读取电压进行比较来感测每个存储单元编程状态的方式从存储单元读取数据。然而,单元阈值电压可能因为一或多个因素而改变,例如读取干扰(read disturbance)或是数据保存(data retention),可能造成感测到的编程状态与写入的编程状态不同,产生数据读取输出中的位失效。一些现存的系统和技术使用相同的验证读取电压,而不管单元阈值电压的变化。

3.一种用于补偿单元阈值电压改变的技术包含储存具有预设读取电压以及优先级的查找表。如果误差修正技术失效,则系统将依照查找表所设置的优先级,以不同的读取电压重新读取。另一种技术是使用电压校准技术,其中在连续的电压下对开启(on)的位(或存储单元)进行计数以找到“谷(valley)”,例如:在位的计数上变化最小的电压。

4.公开内容

5.本公开一方面的特征在于一存储器装置包含:一存储单元阵列,每一存储单元耦接多个字线中的一对应字线,以及多个位线中的一对应位线;一累加电路耦接至存储单元阵列且配置为:当储存在一页面的数据通过在该页面对应的一位线施加多个读取电压中的各该读取电压进行读取时,累加该页面中各该存储单元的读出信号,以产生对应于该读取电压的累加读出信号各自的一输出值;以及一控制器耦接该累加电路且配置为基于读取电压以及与读取电压相关的输出值,判断页面的一校准读取电压。

6.在一些实施例中,累加电路包含一模数转换器配置为将累加读出信号转换为输出值。

7.在一些实施例中,读出信号包含至少一电流或一电压。

8.在一些实施例中,至少一累加电路或控制器配置为记录各别的输出值。

9.在一些实施例中,存储器装置包含控制电路耦接存储器单元阵列。控制电路可配置为以在一读取电压值序列上连续施加一读取电压的方式将读取电压施加于字线。

10.在一些实施例中,控制器以及累加电路可设置于集成电路中。

11.在一些实施例中,控制电路配置为迭代地增加或减少读取电压。第一相邻读取电压值之间的第一量可以与第二相邻读取电压值之间的第二量不同。第一相邻读取电压值之间的第一量可以与第二相邻读取电压值之间的第二量相同。

12.在一些实施例中,控制电路配置为:判断具有一第一读取电压值的读取电压是否低于一阈值电压;响应于判断具有第一读取电压值的读取电压不大于阈值电压,增加或减

少读取电压以具有一第二读取电压值,以将该第二读取电压值施加于对该页面的一后续读取操作;以及响应于判断具有第一读取电压值的读取电压低于阈值电压,启动控制器以判断页面的校准读取电压。

13.在一些实施例中,控制器配置为:对于读取电压序列中的至少二个读取电压值,判断读取电压值序列中的每一读取电压的输出值与紧接在读取电压值之前的一第二读取电压值之间的一差值,从而提供一差序列。

14.在一些实施例中,控制器配置为从至少二个读取电压值中辨识出一特定读取电压值,特定读取电压值在差序列中提供一最小差异;以及将校准读取电压设定为具有特定读取电压值的方式,以差序列以及读取电压判断校准读取电压。

15.在一些实施例中,控制器配置为:对于读取电压序列中的至少二个读取电压值,判断读取电压值序列中的每一读取电压的该输出值与紧接在读取电压值之前的一第二读取电压值之间的一第二差值,从而提供一第二差序列;以及以第二差序列和读取电压判断校准电压值。

16.在一些实施例中,控制器配置为从至少个读取电压值中辨识出一特定读取电压值,特定读取电压值在第二差序列中提供一最小差异;以及将校准读取电压设定为具有特定读取电压值的方式,以第二差序列以及读取电压判断校准读取电压。

17.在一些实施例中,控制电路配置为:在一第一方向上将读取电压从一初始电压值迭代地改变为一第一读取电压值,第一方向为一增加方向和一减少方向的其中之一;判断第一读取电压值的一第一输出值和紧接在第一读取电压值之前的一第二读取电压值的一第二输出值之间的差小于一第一阈值;以及判断具有第一读取电压值的一第一校准读取电压。第二读取电压值的第二输出值与紧接在第二读取电压值之前的第三读取电压值的第三输出值之间的差可以大于第一阈值。

18.在一些实施例中,控制电路配置为:在一第二方向上将读取电压从初始电压值迭代地改变为一第三读取电压值,第二方向为增加方向和减少方向的其中之一;判断第三读取电压值的一第三输出值和紧接在第三电压值前的一第四读取电压值的一第四输出值之间的差小于一第二阈值;以及判断具有第三读取电压值的一第二校准读取电压,其中校准读取电压以第一校准读取电压以该第二校准读取电压来做判断。

19.在一些实施例中,第四读取电压值的第四输出值与紧接在第四读取电压值之前的第五读取电压值的第五输出值之间的差可以大于第二阈值。

20.在一些实施例中,校准读取电压判断为具有下列表达式:

21.v=β(x-y) y

22.其中v、x以及y分别表示校准读取电压、第一校准读取电压以及第二校准读取电压,且β为区间[0,1]之间的常数。

[0023]

在一些实施例中,控制电路配置为:在一第二方向上将读取电压从初始电压值迭代地改变为一第三读取电压值,第二方向为增加方向和减少方向的其中之一;判断第三读取电压的一第三输出值和紧接在第三电压值前的一第四读取电压值的一第四输出值之间的一第一差值;判断第四读取电压值的输出值和紧接在第四读取电压值的一第五读取电压值的一第五输出值之间的一第二差值;判断第一差值和第二差值之间的一差值小于一第二阈值;以及判断具有第二读取电压值的一第二校准读取电压;其中校准读取电压以第一校

准读取电压和第二校准读取电压来判断。

[0024]

在一些实施例中,校准读取电压判断为具有下列表达式:

[0025]

v=β(x-y) y

[0026]

其中v、x以及y分别表示校准读取电压、第一校准读取电压以及第二校准读取电压,且β为区间[0,1]之间的常数。

[0027]

在一些实施例中,校准读取电压为读取电压值序列中的一初始值为一预设值。

[0028]

在本公开的另一方面的特征为存储器装置包含:一存储阵列包含多个存储单元的页面耦接至多个对应的字线;一模数转换器电路耦接至存储器阵列且配置为:当储存在一页面的数据通过在页面对应的一位线施加多个读取电压中各自的读取电压读取时,累加页面中各个存储单元的读出信号以产生对应于读取电压的累加读出信号各自的一输出值;以及一控制器耦接累加电路且配置为基于读取电压以及与读取电压相关的输出值,判断页面的一校准读取电压。

[0029]

在一些实施例中,模数转换器电路包含控制器。

[0030]

在一些实施例中,存储器装置包含一控制电路耦接至存储阵列且配置为以在一读取电压值序列上连续施加一读取电压的方式将读取电压施加于字线。

[0031]

本公开的另一方面特征在于一种方法包含:施加多个读取电压在对应于一存储器装置的存储单元的一页面的字线;对读取电压中的每一读取电压,累加页面中多个存储单元的读出信号以产生对应于读取电压的累加读出信号各自的一输出值;以及基于读取电压以及与读取电压相关的输出值,判断页面的一校准读取电压。

[0032]

在一些实施例中,判断页面的校准读取电压包含:对于读取电压中的至少二个读取电压,判断读取电压值序列中的每一读取电压的输出值与紧接在读取电压值之前的一第二读取电压值之间的一差值,从而提供一差序列;以及以一差序列以及读取电压判断校准电压值。

[0033]

在一些实施例中,以第二差序列以及读取电压判断校准电压值的步骤包含:对于读取电压序列中的至少二个读取电压值,判断读取电压值序列中的每一读取电压的输出值与紧接在读取电压值之前的一第二读取电压值之间的一第二差值,从而提供一第二差序列;以及以第二差序列以及读取电压判断校准电压值。

[0034]

上述实施例中的技术包括方法、系统、计算机程序产品以及计算机可读取介质。在一范例中,一方法可被存储器所执行,且该方法可包含以上所描述的存储器所执行的步骤,例如:判断非易失性存储器读取电压的步骤。在另一范例中,一个这样的计算机程序产品适当地体现于由一或多个处可器可执行指令的一非瞬时机械可读取介质中。指令配置为使一或多个处理器执行以上描述的步骤。一个这样的计算机可读取介质储存指令,当该指令由一或多个处理器所执行时被配置为使一或多个处理器执行上述步骤。

[0035]

在附图和以下实施方式中描述了一或多个公开的实施例的细节。根据说明书、附图以及权利要求书范围,其他特征、方面以及优点将变得显而易见。

附图说明

[0036]

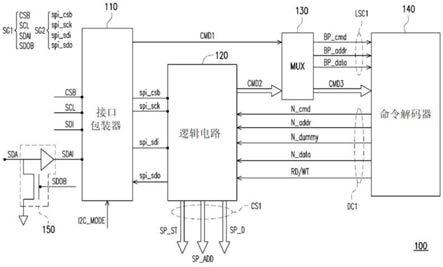

图1a为根据本公开的一或多个实施例中的范例系统的示意图。

[0037]

图1b为根据本公开的一或多个实施例中,包含模数转换器电路的示例性存储器框

图。

[0038]

图1c为根据本公开的一或多个实施例中,2d存储器的范例区块的示意图。

[0039]

图1d为根据本公开的一或多个实施例中,3d存储器的范例区块的示意图。

[0040]

图2a为根据本公开的一或多个实施例中,多层储存单元(multi-level cell,mlc)在不同状态下的阈值电压分布范例图。

[0041]

图2b为本公开中在不同写入/擦除次数(program/erase cycle)下,计数单元的读取输出和读取电压之间的关系图。

[0042]

图3为根据本公开的一或多个实施例中,具有模数转换器的存储器判断存储器读取电压的范例图。

[0043]

图4为根据本公开的一或多个实施例中,在相邻的字线中组合具有不同状态的存储单元以表示新状态的范例图。

[0044]

图5为根据本公开的一或多个实施例中,以模数转换器使用谷追踪(valley-tracking)图表判断读取电压的方法的流程图。

[0045]

图6为根据本公开的一或多个实施例中,以模数转换器使用谷追踪(valley-tracking)图表判断读取电压的另一方法的流程图。

[0046]

附图标记说明

[0047]

100:系统

[0048]

110:装置

[0049]

112:装置控制器

[0050]

113:处理器

[0051]

114:内部存储器

[0052]

116:存储器

[0053]

117:控制器

[0054]

118:模数转换器电路

[0055]

120:主机装置

[0056]

130:存储器界面

[0057]

132:控制逻辑

[0058]

134:数据缓冲器

[0059]

140:纠错码电路

[0060]

140c:二维存储区块

[0061]

141,157:存储单元

[0062]

142:编码器

[0063]

142c,152:单元页面

[0064]

143:串选择晶体管

[0065]

144:译码器

[0066]

144c,154:单元串

[0067]

145:接地选择晶体管

[0068]

146,156:串选择线

[0069]

148,158:接地选择线

[0070]

149,159:共源线

[0071]

150,410:存储单元阵列

[0072]

152:单元页面

[0073]

160:感测放大器

[0074]

200,250,300,(a)320,(b)340,(c)360,(d)380,400:图表

[0075]

202,204,206,208,322,324,342,344,350,361,382,384:曲线

[0076]

203:虚曲线

[0077]

326,346:线段

[0078]

362:第一正向斜坡部分

[0079]

366:第二正向斜坡部分

[0080]

364:平面部分

[0081]

370:部分

[0082]

402,wl:字线

[0083]

404,bl:位线

[0084]

500,600:流程图

[0085]

502,504,506,508,602,604,606,608,610,612,614,616,618,620:步骤

[0086]

a,b,c:编程状态

[0087]

bl0、bl1、...、bl

n-1

、bln:栏位线

[0088]

csl:共源线

[0089]

er:擦除状态

[0090]

gsl:接地选择线

[0091]

gst:接地选择晶体管

[0092]

hvt

initia1

,lvt

initial

:初始阈值电压分布

[0093]

hvt

retentio

,lvt

retention

:阈值电压分布

[0094]isum

:数字电流值

[0095]ii

,i

i-1

:模数转换器输出

[0096]

lsb:最低有效位

[0097]

msb:最高有效位

[0098]

pe0,pe3k,pe5k,pe10k,pe15k,pe20k:数据图表

[0099]

ssl:串选择线:

[0100]

sst:串选择晶体管

[0101]vdisturb

,v

rd1

,v

rd2

,v

rd3

,v

rdpass

,v

wli-1

,v

wli

,v

wlj

:读取电压

[0102]vl0

,v

h0

,v

l1

,v

h1

,v

l2

,v

h2

,v

13

,v

h3

,:阈值电压

[0103]vh0’:限制电压

[0104]vpass

:高电压

[0105]

wl0、wl1、...wl

n-1

、wln:行字线

[0106]

x:第一校准电压

[0107]

y:第二校准电压

[0108]

β:数值

[0109]

δ1,δ2,...,δ

i-1

,δ

j-1

,δ

j-2

:电压间隔

[0110]

δ

th1

:第一阈值电压

[0111]

δ

th2

:第二阈值电压

具体实施方式

[0112]

由于频繁的读写操作,存储器可能遭遇到读取干扰(read disturbance),其中存储单元的状态,例如存储器中的一擦除状态以及一或多个写入状态可能增加或减少阈值电压。读取干扰可能在读取时导致失效位(或错误位)。纠错码(error-correcting code,ecc)译码器可配置为在纠错码方案的纠错能力下译码从存储器读取的数据以侦测和除错。数据可通过比较单元阈值电压和读取电压(或参考读取电压)的方式检测每个存储单元的状态以读取存储单元的数据。

[0113]

三维存储器系统例如:三维与非门快闪存储器(nand flash memory)的一大挑战在于减少错误位以及增加读取效能。然而,三维与非门快闪存储器的阈值电压v

t

分布会受到多种条件的影响,例如层数变化、写入/擦除次数、温度、保留时间以及页面地址,导致最佳的读取电压无法固定。最佳读取电压表示当施加读取电压时获得最小的变化,例如最小数量的错误位。

[0114]

在一些传统技术中,使用一预设读取电压来读取存储器的数据,无论输入参数如何的变化。然而预设读取电压可能与最佳读取电压有落差,导致纠错码译码时额外的负担(overhead)。

[0115]

在另一传统技术中,使用储存多个预设读取电压的查找表,预设读取电压根据与输入参数相互独立的相关优先级以固定顺序使用。数据首先以具有最高优先权的第一预设电压读取,如果读取输出的数据未通过纠错码测试,则具有第二高顺位的第二预设电压被使用。重试读取操作持续进行直到读取输出通过纠错码测试。然而,查找表的建立可能耗费大量的人力资源以及研发时间,工程师可能需要根据输入参数逐一微调最佳读取电压。表格的大小可能因不同的制程技术以及不同的操作条件而变得越来越大。

[0116]

机器学习(machine learning,ml)技术已经被提出使用于判断最佳读取电压,举例来说,机器学习的线下推论(offfine inference)可以使用于判断输入参数以及最佳读取参数之间的关系。然而,为了取得高准确度,这样的线下推论可能造成大量的存储器负担。在线推论(online inference)可能须要额外的运算以及时间负担,从而降低读取延迟。

[0117]

谷搜寻(valley search)法也被提出用于判断最佳读取电压。在谷搜寻技术中,位被以连续不同的电压计数,并且观察由读取电压的变化而导致位计数的变化。在位计数中变化最小的电压可对应至谷的最低点,并且可提供最佳的读取电压。然而由硬件电路所实施的位计数需要很长的时间。

[0118]

整体来说,判断最佳读取电压是费时且冗长的,且随着过程中考量的输入参数的增加,计算的时间和功耗可能会增加。因此,需要开发出一种技术,可以在时变通道中以有限的读取延迟时间准确地读取,并且可以通过最佳读取电压来降低纠错码的负担。

[0119]

本公开的实施例提供一种系统、方法以及技术用于判断存储器系统(例如:非易失性存储器系统)的读取电压(例如:校准读取电压)。该技术可通过模数转换器电路,通过内存芯片的谷搜寻方法来校准(或最佳化)读取电压,以最小化错误位的数量,从而减少纠错

码译码负担、减少额外的存储器负担、减少读取延迟、减少研发成本以及提升读取准确度。此处的术语“校准读取电压”代表通过模数转换器电路,使用内存芯片谷搜寻方法校准的读取电压。校准读取电压可以是对应于最小变化的最佳读取电压,例如:最小值或是最小数量的错误位。

[0120]

在一些实施例中,模数转换器电路实施于存储器中,模数转换器包含一累加电路配置在读取操作时累加多个位的电流以获得电流的总和。累加电路可包含模数转换器配置为将电流总和的模拟信号转换为一数字值。模数转换器电路能够获得更快的计数时间,例如在谷搜寻时,以判断校准读取电压(或最佳化读取电压)。

[0121]

在一些实施例中,存储器储存一预定读取电压,例如:基于经验数据由存储器的制造商来决定。控制器可以实施于模数转换器电路自身或是模数转换器的外部。预定读取电压可以被校准成为特定页面或区块的校准读取电压(或最佳读取电压),举例来说,以预定读取电压作为起始,连续施加不同的读取电压作为谷搜寻的一部分。对于每一个测试电压,模数转换器电路累加页面上多个存储单元所对应字线的电流,获得电流的总和,并且将总和转换为数字值。控制器可比较连续不同读取电压的输出值,以多个数字值以及不同的读取电压判断校准读取电压。特别地,在位计数中提供最小变化的读取电压可对应于谷的底部,且可提供最佳或校准读取电压。为了改善准确度,控制器也可比较相邻读取电压数字值的第一差值或甚至相邻第一差值之间的第二差值来判断谷的底部。

[0122]

在一些实施例中,除了以电流模式操作外,例如累加读取操作中多个位的电流,模数转换器也可配置为以电压模式操作,例如累加读取操作中多个位的电压,或是包含电流模式以及电压模式两者的混合模式。

[0123]

传统的存储器装置或系统中并不包含这样的模数转换器电路或是以这样的方式使用模数转换电路。使用模数转换器电路可累加电流并且输出一数字值以加速快位计数,并以更高的能效和读取时间来减少位计数操作。存储器中实施模数转换器也可允许减少错误位,以获得更高的准确度,并减少纠错码的译码负担。

[0124]

该技术可应用于多种不同的易失性存储器或是非易失性存储器,例如与非门快闪存储器(nand flash memory)、或非门快闪存储器(nor flash memory)、可变电阻式存储器(resistive random-access memory,rram)、相变化存储器(phase-change memory,pcm)例如相变化随机存取存储器(phase-change random-access memory,pcram)、自旋转力矩(spin-transfer torque,stt)磁阻式随机存取存储器(magnetoresistive random-access memory,mram)等。该技术也可应用于电荷捕捉式(charge-trapping)存储器装置,例如:硅-氧化物-氮化物-氧化物-硅(silicon-oxide-nitride-oxide-silicon,sonos)存储器装置以及浮栅式(floating-gate)存储器装置。该技术可应用于二维存储器装置或是三维存储器装置。该技术可应用于多种类型的存储器,例如单层储存单元(single-level cell,slc)、多层储存单元(multi-level cell)例如双层储存单元装置(2-level cell devices)、三层储存单元(triple-level cell,tlc)、四层储存单元(quad-level cell,qlc)或是五层储存单元(penta-level cell,plc)。或者或更甚者,该技术可应用于不同型态的装置或系统,例如安全数字卡(secure digital card,sd)、嵌入式多媒体卡(embedded multimedia cards,emmc)或是固态硬盘(solid-state drives,ssd)、嵌入式系统等。

[0125]

图1a示出一范例性的系统100,其中包含一装置110以及一主机装置120。装置110

包含一装置控制器112以及一存储器116。装置控制器112包含一处理器113以及一内部存储器114。

[0126]

在一些实施例中,装置110为一储存装置,举例来说,装置110可以为一嵌入式多媒体卡(emmc)、一安全数字卡(sd)、一固态硬盘(ssd)或其他合适的储存方式。在一些实施例中,装置110为一智能型手表、一数码相机或是一媒体播放器。在一些实施例中,装置110为一客户端装置耦接至主机装置120,举例来说,装置110是作为主机设备120的数码相机或媒体播放器中的sd卡。

[0127]

装置控制器112为一般用途的微处理器或是特殊应用的微处理器。在一些实施例中,装置控制器112为装置110的存储器控制器。以下段落基于装置控制器112为存储器控制器的实施例描述多种技术。然而在以下段落所描述的技术也可以应用于装置控制器112为不同于存储器控制器的另一种控制器的实施例中。

[0128]

处理器113配置为执行指令以及处理数据,指令包含框架指令及/或其他以框架编码及/或其他编程编码各别储存于第二存储器的其他编程指令。数据包含由处理器113所执行,对应于框架及/或其他编程的编程数据等合适的数据。在一些实施例中,处理器113为一般用途处理器或一特殊应用处理器,处理器113也可为一中央处理单元(cpu)。

[0129]

处理器113存取内部存储器114的指令或数据。在一些实施例中,内部存储器114为一静态随机处理存储器(static random access memory,sram)或是一动态随机处理存储器(dynamic random access memory,dram),举例来说,在一些实施例中,当装置110为一嵌入式多媒体卡、一sd卡或一智慧手表,内部存储器114为静态随机处理存储器。在一些实施例中,当装置110为一数码相机或示一多媒体播放器,内部存储器114为动态随机处理存储器。

[0130]

在一些实施例中,内部存储器为包含于存储器控制器112中的一快取存储器,如图1a所示,内部存储器114储存指令编码,指令编码对应于处理器113所执行的指令,及/或处理器113在运行时所要求的数据。

[0131]

装置控制器112将指令编码及/或数据由存储器116传送至内部存储器114。在一些实施例中,存储器116为一非易失性存储器配置为长期储存指令及/或数据,例如:与非门快闪存储器或是其他适当的非易失性存储器装置。在存储器116为与非门快闪存储器的实施例中,装置110为一快闪存储器装置,例如一快闪存储器卡,且快闪存储器112为一与非门快闪存储器控制器。举例来说,在一些实施例中,当装置110为一嵌入式多媒体卡或一sd卡时,存储器装置116为一与非门快闪存储器;在一些实施例中,当装置110为一数码相机时,存储器116为一sd卡;以及在一些实施例中,当装置110为一媒体播放器时,存储器116为一硬盘。

[0132]

在一些实施例中,装置控制器112配置为传送至主机装置120,或自主机装置120接收数据以及指令,装置控制器112进一步配置为传送数据至存储器116以及自存储器116接收数据。举例来说,装置控制器112配置为传送数据以及写入命令以指示存储器116将数据储存于特定的地址,在另一范例中,装置控制器112配置为自主机装置120接收读取要求(或读取指令),并传送对应的读取指令至存储器116以读取存储器116中特定地址的数据。

[0133]

在一些实施例中,装置控制器112包含一纠错码电路140,纠错码电路140可以包含纠错码编码器142以及纠错码译码器144。纠错码编码器142可配置为接收要储存于存储器116的数据并生成一码字(codeword),例如以纠错码编码方法对数据进行编码。纠错码编码

器112可包含一里德-所罗门编码器(reed solomon encoder)、bch编码器(bose-chaudhuri-hocquenghem encoder)、低密度奇偶校验编码器(low-density parity check,ldpc encoder)、涡轮码编码器(turbo code encoder)或其中的任何组合。纠错码译码器144可配置为在纠错码方案的纠错能力下译码从存储器读取的数据以侦测和除错。在一些实施例中,纠错码电路140包含于存储器116中。在一些实施例中,装置控制器112包含一第一纠错码电路140,且存储器116包含一第二纠错码电路140。

[0134]

如以下进一步讨论的细节,装置110配置为判断自存储器116读取数据的读取电压,例如:回应于来自主机装置120的读取要求。模数转换器电路118可整合至存储器116中,例如:在生产存储器116的过程中。模数转换器118的结果可以用于读取来自存储器116的数据。在一些实施例中,模数转换器电路118也可以被整合至装置控制器112中,模数转换器电路118可包含一累加电路,累加电路可包含模数转换器。存储器116也可包含耦接至模数转换器电路的控制器117,且配置为以模数转换器电路118的输出判断读取电压。

[0135]

图1b示出具有存储单元阵列150的存储器116的示例性配置。存储单元可包含存储晶体管配置为储存元件,存储晶体管可包含硅-氧化物-氮化物-氧化物-硅(sonos)晶体管、浮栅式晶体管、氮化物只读存储器(nitride read only memory,nrom)晶体管,或是任何适当可储存电荷的非易失性存储器金属氧化物装置。存储器116可包含x方向译码器(或行译码器)以及y方向译码器(或栏译码器),每个存储单元可以通过各自的字线耦接至x方向译码器,以及通过各自的位线耦接至y方向译码器。因此,每个存储单元可以通过各自的字线和位线被x方向译码器以及y方向译码器所选择以进行读取或写入。

[0136]

存储器116包含一存储器界面(输入/输出埠)130配置为与装置控制器112通信。存储器116也可包含一控制逻辑(或控制电路)132耦接至存储器界面130以及存储器阵列150,并且配置为控制存储器116的操作。举例来说,控制逻辑132可以通过存储器界面130自装置控制器112接收一读取命令,并读取存储器阵列中对应的数据。存储器116也包含一感测放大器160以数据线连接至y方向解法器,和用于缓冲自感测放大器160至存储器界面130输出信号的数据缓冲器134。

[0137]

在写入操作时,数据寄存器注册来自存储器界面130的输入数据,并且地址产生器产生对应的实体地址以将输入数据储存于存储器阵列150中的特定存储单元。地址产生器连接于x方向译码器以及y方向译码器,x方向译码器以及y方向译码器通过对应的字线以及位线控制以选择指定的存储单元。静态存储器缓冲器可以在有电源供应的情况下将来自数据寄存器的输入数据保留在其存储器中。控制逻辑132处理来自静态存储器缓冲器的写入信号,并将控制信号提供给产生写入电压的电压产生器,并将写入电压提供给x方向译码器以及y方向译码器。y方向译码器配置为输出写入电压至位线以储存写入数据至特定的存储单元。

[0138]

在读取操作时,控制逻辑132提供控制信号至电压产生器以及感测放大器160,电压产生器可提供电压至x方向译码器以及y方向译码器用于选择存储单元。感测放大器160感测来自代表储存于所选择的存储单元的数据位(0或1)的位线的小功率(电压或电流)信号,并且放大小功率信号的震荡至可识别的逻辑电平(logic level),以使数据位可被存储器116外的逻辑适当的判读。数据缓冲器134自感测放大器160接收被放大的电压,并且通过存储器界面130输出放大功率信号至装置控制器112。

[0139]

在一些实施例中,如图1b所示,存储器116包含连接至存储器阵列150的模数转换器电路118,模数转换器118可耦接至控制逻辑,例如控制器117。如以下进一步讨论的细节,控制器117可配置为在读取操作时以模数转换器电路118的输出判断校准(或最佳)读取电压。举例来说,控制器117可对模数转换器的输出,例如对应于多个存储单元的累加电流的数字值于不同的读取电压执行谷搜寻,以判断校准读取电压。控制逻辑132可接着提供控制信号至电压产生器以产生校准读取电压。电压产生器可提供校准读取电压至x方向译码器以及y方向译码器用于选择存储单元以通过感测放大器160读取数据。读出数据可以通过存储器界面130从存储器116送至纠错码译码器144以进行译码和除错。

[0140]

在一些实施例中,控制器117可以包含于模数转换器电路118之中。模数转换器电路118可判断校准读取电压并且提供校准读取电压的信息至控制逻辑132用于产生校准读取电压。控制器可为存储器116中分离的部件或分布于多个示出及/或未示出的部件之间。

[0141]

在一些实施例中,存储器116以施加第一读取电压至一或多个存储阵列150的目标存储单元,以执行第一读取操作,感测模数转换器电路118第一读取操作的第一输出,以及记录第一输出。存储器116以施加第一读取电压至一或多个存储阵列150的目标存储单元,以执行第二读取操作,感测模数转换器电路118第二读取操作的第二输出,以及记录第二输出。第一读取电压与第二读取电压之间的差值可被判定,回应于第一输出以及第二输出之间的差值实质上与零相同,存储器116,例如:模数转换器电路118或控制器117可输出第二读取电压作为校准读取电压。

[0142]

图1c示出当存储器116为二维存储器时二维存储区块140的范例性配置,区块140包含存储单元141耦接至一系列的栏位线bl0、bl1、...、bln-1以及bln组成多个单元串144,以及一系列的行字线wl0、wl1、...、wln-1以及wln组成多个单元页面142。单元串144可包含多个存储单元141,一串选择晶体管(string select transistor,sst)143以及一接地选择晶体管(ground select transistor,gst),其中都是以串联方式耦接。串选择晶体管143的栅极耦接至串选择线(string select line,ssl)146,不同串选择线中的串选择晶体管的栅极也耦接至相同的串选择线。存储单元141的栅极各别地耦接至字线wl0、wl1、...、wln-1、wln,存储单元141通过接地选择晶体管耦接至共源线149(common source line,csl)。接地选择晶体管145耦接至接地选择线(ground select line,gsl)148,不同串中的接地选择晶体管的栅极也耦接至相同的接地选择线。单元页面142可包含多个存储单元141。单元页面142中的存储单元141串联耦接至对应的字线。当输入电压施加于字线时,输入电压也施加至单元页面142中存储单元141的栅极。为了在读取操作中读取区块140中特定的单元页面142,在对应于特定单元页面142的字线施加较低的电压,同时在区块140中的其他单元页面上施加较高的电压。

[0143]

装置110可包含快闪存储器转换层(flash transltion layer,ftl)来管理读取、写入以及擦除操作。快闪存储器转换层可储存于装置控制器112中,例如:在内部存储器114中。快闪存储器转换层使用逻辑对实体地址映射(logical-to-physical address mapping)表储存逻辑区块中的逻辑页面所映射的实体区块中的实体页面。

[0144]

图1d示出存储器116为三维存储器时三维存储器区块150的范例。存储单元157以三维方式作排列,例如直角坐标系(xyz coordinate system),并且耦接至多个字线组成多个单元页面152,以及耦接至多个位线bl《n》、bl《n 1》组合成多个单元串154。单元串154包

含串联耦接的多个存储单元157,其中一存储单元可配置为串选择晶体管(sst)耦接至串选择线(ssl)156,以及一存储单元可配置为接地选择晶体管(gst)耦接至接地选择线(gsl)158。存储单元157通过接地选择晶体管(gst)耦接至共源线(csl)159。

[0145]

存储区块150可包含多个存储层堆栈在一起,例如:垂直地沿着z轴方向每一存储层可为二维平面层,例如:包含多个单元页面152的x-y平面,每一单元页面152可以个别地读取及/或编程。为了在读取操作中读取存储层160中特定的单元页面152,在对应于特定页面单元152的字线施加较低的电压,存储层中的其他单元页面152也施加较低的电压,同时在区块150中的其他存储层上施加较高的电压。

[0146]

存储单元可处于一编程状态或一擦除状态,举例来说,若存储单元为一单层储存单元(slc),存储单元可被编程为“0”的编程状态或是为“1”的擦除状态。若存储单元为可储存二位数据的多层储存单元(mlc),存储单元可被编程为编程状态(0,1)、(0,0)、(1,0)中的其一,或是擦除为(1,1)的擦除状态。

[0147]

一旦被编程或擦除,存储单元具有对应的阈值电压,阈值电压为存储单元的特性。当相等或大于阈值电压的读取电压施加在存储单元的栅极时,存储单元可被开启。当低于阈值电压的读取电压施加在存储单元的栅极时,存储单元可被关闭。读取动作并非编程或是擦除动作,也不旨在改变存储单元的状态。

[0148]

区块中多个存储单元的阈值电压对应于相同的状态,例如:擦除状态或编程状态,可具有一分布,例如在一较低限制电压以及一较高限制电压之间的范围。具有该范围内阈值电压的存储单元会被视为在对应的状态,换句话说,处于状态中的存储单元具有在该范围内的阈值电压。

[0149]

图2a示出阈值电压的分布以及存储器中存储单元在不同状态下的读取电压图表200。存储单元可为图1c中的存储单元141或是图1d中的存储单元157。存储单元可以是与非门快闪存储器。仅用于说明目的,存储单元为可储存二位数据的一多层单元,存储单元可被编程或擦除以具有四个状态er、a、b以及c中的其中之一。在一些范例中,er为擦除状态(1,1),而a、b、c为编程状态(0,1)、(0,0)以及(1,0),状态er、a、b以及c具有逐渐升高的读取电压。多层单元与非门快闪存储器可将字线中每个存储单元的两位划分为两个页面(page),其为一次编程的单位。一条字线所有存储单元的最低有效位(least significant bits,lsbs)形成该字线的最低有效位页面,且字线所有存储单元的最高有效位(most significant bits,msbs)形成该字线的最高有效位页面。

[0150]

一旦被编程或擦除,存储单元具有对应的阈值电压,阈值电压为存储单元的特性。存储单元可为浮栅式晶体管,当高于或与阈值电压相同的读取电压施加在存储单元的栅极时,存储单元可被开启。当低于阈值电压的读取电压施加在存储单元的栅极时,存储单元可被关闭。读取动作并非编程或是擦除动作,也不旨在改变存储单元的状态。

[0151]

每个状态对应于在一较低电压以及一较高电压之间的范围分布的阈值电压。具有该范围内阈值电压的存储单元会被视为在对应的状态,换句话说,处于状态中的存储单元具有在该范围内的阈值电压。举例来说,若存储单元具有位于v10至vh0之间的阈值电压,存储单元在er状态;若存储单元具有vl1至vh1之间的阈值电压,存储单元在a状态;若存储单元具有v12至vh2之间的阈值电压,存储单元在b状态;以及若存储单元具有v13至vh3之间的阈值电压,存储单元在c状态。曲线202、204、206、208各别示出状态er、a、b、c下各自的阈值

电压分布。

[0152]

在读取操作时,一读取电压可被施加在耦接于所选择存储单元栅极的字线,以判断被选择的存储单元为开启或关闭状态。当一大于er的阈值电压但小于a的阈值电压的读取电压v

rd1

被施加时,存储单元在er状态时会被开启,在a、b、c状态时则会被关闭。当一大于a的阈值电压但小于b的阈值电压的读取电压v

rd2

被施加时,存储单元在er或a状态时会被开启,在b或c状态时则会被关闭。当一大于b的阈值电压但小于c的阈值电压的读取电压v

rd3

被施加时,存储单元在er、a或b状态时会被开启,在c状态时则会被关闭。当一大于所有er、a、b、c的阈值电压的读取电压v

rdpass

被施加时,存储单元无论在何种状态下都会被开启。

[0153]

在读取操作时,在同一位线中的其他存储单元上施加一通过电压v

rdpass

且被开启。因此,如果被选择的存储单元在读取电压v

rd

下开启,则对应位线中的存储单元形成导电路径,并且具有可被耦接至字线的电流或电压传感器所侦测的电流或电压变化。如果被选择的存储器被读取电压关闭,则对应位线中的存储单元不会形成导电路径,并且不会具有可被耦接至字线的电流或电压传感器所侦测的电流或电压变化。

[0154]

由于重复的读写操作,读取干扰的现象可能发生,在读取干扰现象中,存储单元的阈值电压不正常地增加。如图2a所示,在一些范例中,擦除状态er的分布曲线202包含虚曲线203,虚曲线203包含较高的阈值电压。举例来说,新的较高限制vh0’比较高限制电压vh0还要高。当新的较高限制电压vh0’位于a状态的阈值电压v11以及vh1的范围内时,擦除状态er与编程状态a重叠。亦即,存储单元有重叠的状态,当读取电压v

disturb

被施加时,具有擦除状态er阈值电压的存储单元转变为关闭状态而非开启状态。因此,通过以特定读取电压侦测存储器为开启或关闭,可以判断存储单元是否遭受读取干扰。在一些范例中,存储单元中具有较低阈值电压的状态,例如er以及a,相较于具有较高阈值电压的状态更容易受到读取干扰的影响。

[0155]

图2b示出在存储器上具在不同写入/擦除次数下(0、3000或3k、5000或5k、10000或10k、15000或15k、20000或20k),多层单元装置的单元计数与读取电压之间的关系数据图表250。图2b显示存储单元的阈值电压分布以及最佳读取电压可以依据一或多个输入参数(例如:存储单元的写入/擦除次数)而变化。pe0数据,当没有写入/擦除次数时,可对应于图2a所示出的阈值电压分布数据。读取电压v1对应于图2a中的读取电压v

rd1

,且可为存储单元读取擦除状态er(1,1)的最佳读取电压。读取电压v2对应于图2a中的读取电压v

rd2

,且可为存储单元读取擦除状态(1,1)以及编程状态(0,1)的最佳读取电压。读取电压v3对应于图2a中的读取电压v

rd3

,且可为存储单元读取擦除状态er(1,1)、编程状态a(0,1)以及编程状态b(0,0)的最佳读取电压,且剩余的存储单元可被判断为具有编程状态c(1,0)。当存储器的写入/擦除次数增加时,最佳化读取电压上升,且数据图表变的更浅。

[0156]

图3示出根据本揭露的一或多个实施例中,具有模数转换器电路的存储器判断存储器读取电压的范例。存储器可为图1a以及图1b中的存储器116,模数转换器电路可为图1a以及图1b中的模数转换器电路118,模数转换器电路可包含于存储器中。存储器可包含控制器,例如图1a以及图1b中的控制器117,配置为以模数转换器的输出判断校准(或最佳)读取电压。控制器可以包含于控制逻辑中,例如图1b的控制逻辑132,模数转换器电路中,或是与控制逻辑以及模数转换器分离。仅用于说明的目的,图3中存储器的存储单元为可储存一位数据(例如:或01)的单层单元装置(slc)。

[0157]

图表(a)320示出存储器的存储单元(例如:单层单元)状态的初始或假定阈值电压分布,类似于图2a所示多层单元状态的阈值电压分布。曲线322显示较低状态(例如:具有位1的擦除状态)下的初始阈值电压分布lvt

initial

,而曲线324显示较高状态(例如:具有位0的编程状态)下的初始阈值电压分布hvt

initial

。线段326显示预设读取电压v

wld

的位置,其位于较低阈值电压以及较高阈值电压之间,预设读取电压v

wld

可以储存于存储器中,例如:控制逻辑或模数转换器电路中。在一些范例中,预设读取电压v

wld

由存储器的制造商在生产存储器时预配置。在一些范例中,预设读取电压v

wld

由一或多个存储器特性来判定(例如:周期性地更新)。

[0158]

如以上所述,存储器可能遭遇读取干扰或保留,其中存储器中存储单元的状态(例如:擦除状态以及一或多个编程状态)可能具有增加或减少的阈值电压。图表(b)340示出存储器中存储单元(例如:单层单元)状态的阈值电压分布在发生数据保留时的范例图。在此范例中,曲线342显示较低状态下(例如:具有位1的编程状态)的阈值电压分布lvt

retention

变化,曲线344绘示与预设读取电压v

wld

重叠的较高状态(例如:具有位0的编程状态)下的阈值电压分布hvt

retention

的变化。因此,若使用预设读取电压v

wld

,原本应该在一状态(例如:具有位0的较高状态)的位会被读取为在另一状态(例如:具有位1的较低状态)。线段346显示最佳(或校准)读取电压v

wl

,其位置位于改变后的较高状态和较低状态的阈值电压之间(例如:曲线342、344所绘示)。

[0159]

为了判断读取存储器页面中存储器单元的最佳读取电压的位置,存储器配置为使用模数转换器电路以读取操作读取存储器页面。模数转换器电路可以对读取电压要被读出的存储器页面的多个字符的电流进行累加,而不是计算读取电压要被读出的存储器页面的多个字符的数量。这可以大幅增加读取速度,进而加快判断速度。

[0160]

图4的图400为根据一或多个实施例中,模数转换器电路如何累积存储单元被读出的电流的示意图。一存储单元阵列410储存一定数量存储单元,每一存储单元耦接至对应的字线402以及对应的位线404。每一存储单元为一对应于字符“1”的擦除状态或是对应于字符“0”的编程状态。一页面,例如图1c的页面142,耦接至字线402。当字线被施加一读取电压时,对应页面中的编程字符可被读出。若字符为1,会有一电流流出,对于每一次的每个读取电压,模数转换器电路会从左到右水平的累加存储单元的电流(位1)。如图4所绘示,对于第一字线402来说,会有6个可造成电流的位“1”,模数转换器电路可以累加6个编程位的电流,并且输出一数字电流值isum,数字电流值可储存于模数转换器电路或是存储器中。相较之下,传统的谷搜寻方法为计算包含位“1”的位数量,且需要计算6次,这可能比使用模数转换器电路一次计算6位数字电流值还要慢。当相同的页面被以第二读取电流读取时,模数转换器可清除先前的电流值并且在第二读取电压下再次累加同一页面的电流。通过这样的方法,可以获得模数转换器电路的输出(例如:数字电流值isum)相对于读取电压变化的数据图表,例如图3中所示的图表(c)360。

[0161]

回到图3,图表(c)360以读取电压的函数绘示模数转换器电路的输出i,曲线可迭代地增加或减少读取电压来产生,例如:由预设的vwld开始。在每个读取电压,一读取操作被执行,并且模数转换器电路用于累加读取存储单元的电流,从而获得累加电流的总和并将其转换为数字值i。如图表(c)360所示,曲线350以在初始状态下(如图表(a)320所示)存储单元的页面的读取电压的函数示出模数转换器电路的输出i。其中可看出模数转换器电

路的输出i随着存储单元的数据保留而改变。如上所述,在所有读取操作中,一高电压v

pass

施加在被读出的页面之外的字线。

[0162]

如图(c)360所示,曲线361包含第一正向斜坡部分362、一平面部分364以及一第二正向斜坡部分366。在平面部分364之下且在第一正向斜坡部分之中,随着更少的位“1”被读出,模数转换器电路的输出减少,这减少了模数转换器的输出,例如数字值i。在平面区域364之上且在第二正向斜坡部分366之中,随着更多的编程位“0”被错误读出为位“1”,模数转换器电路的输出增加。因此,通过将读取电压置于平面部分364内,读取错误可被减少,例如:最小化。如图表(c)360所示,平面区域364位于阈值电压范围342、344之间。在平面区域364中,模数转换器电路的输出实质上为平坦的,且为读取电压的函数,其指示最佳读取电压v

wl

在平面区域364之内。

[0163]

为了更精准的判断最佳读取电压的位置,位于曲线361包含平面区域364的部分370中的数据可被进一步的处理。图(d)380以读取电压的函数示出模数转换器输出的导数。举例来说,图(c)380的曲线382可由迭代地减少读取电压,例如:使用电压v

wl1

,v

wl2

、...、v

wlk-1

、v

wlk

,并且使用较准步骤计算连续(或相邻)读取电压v

wli-1

、v

wli

的模数转换器输出ii-1、ii之间的差值δi,例如δi=ii-ii-1。当差值近似于零或为最小值时,曲线382的底部被识别出来,且从而判断出最佳读取电压。也就是说,曲线382中的最小值(例如:在实际时间限制下尽可能接近最小值、运算功率、电路封装、电压位阶大小等)提供了校准读取电压,例如最佳读取电压v

wl

。为了进行比较,图(c)380中的曲线384也是以曲线350中的部分370所产生,其中显示最佳v

wl

小于先前的最佳v

wl

,而先前的最佳v

wl

小于预设v

wld

,这指示了数据保留会使最佳读取电压逐渐变小。

[0164]

在一些实施例中,存储器,例如:控制器,可预判断一寻找范围,例如:图3的图(d)中所示的寻找范围386。寻找范围386可由初始电压,例如:预设电压v

wld

,至预设定阈值电压,例如:v

wli

所组成。读取电压可由初始电压逐渐地增加(例如:以电压间隔δv)至预设定阈值电压。若读取电压仍然在寻找范围内,读取电压持续减少以获得模数转换器电路的新输出值。若读取电压在寻找范围之外或是超过预设定阈值电压,也就是说,横跨整个寻找范围的读取电压都已被使用,存储器,例如:控制器,可以模数转换器电路各自的输出值以及一系列的读取电压判断页面的校准读取电压。在判断校准读取电压后,存储器接着可以校准读取电压读取储存在页面中的数据。

[0165]

在一些实施例中,寻找范围可由一初始电压至一大于初始电压的阈值电压。在一些实施例中,寻找范围可由一初始电压至一小于初始电压的阈值电压。在一些实施例中,寻找范围可介于第一以及第二阈值电压之间,并且初始电压大于第一阈值电压且小于第二阈值电压。存储器可改变读取电压首先从初始电压至第一阈值电压,接着由初始电压至第二阈值电压。存储器也可改变读取电压首先从初始电压至第二阈值电压,接着由初始电压至第一阈值电压。

[0166]

图5示出根据本揭露一或多个实施例中,具有模数转换器电路的存储器判断校准读取电压方法的流程图500。存储器可为图1a以及图1b中的存储器116,模数转换器电路可为图1a以及图1b中的模数转换器电路118。存储器可包含控制器,例如图1a以及图1b中的控制器117,配置为基于模数转换器电路的输出判断校准(或最佳)读取电压。控制器可包含在模数转换器电路中的控制逻辑,例如:图1b中的控制逻辑132,或是可与控制逻辑以及模数

转换器电路分离。流程500可由存储器执行。仅用于说明的目的,存储器中的存储单元以单层单元(slc)做范例。

[0167]

存储器可以在包含多个存储单元的页面上储存数据。页面,例如图1c中的页面142以及图1d中的页面152,对应于存储器中的字线。存储单元可以在不同的状态,例如:具有位“1”的擦除状态以及具有位“0”的编程状态。

[0168]

流程500开始,例如:当存储器接收一读取要求读取页面上的数据,存储器接着可使用流程500以判断页面的一校准读取电压以读出页面的数据,流程500接着执行迭代步骤,该迭代步骤执行页面读取(步骤502)以及记录模数转换器电路的输出值(步骤504)。

[0169]

如图3所示,迭代的页面读取可通过在页面的字线施加一系列连续的读取电压来提供。迭代地页面读取可以从预设定的读取电压起始,例如:存储器中存在的预设读取电压。为了迭代地页面读取,读取电压可以逐渐地从预设定读取电压增加或减少,例如:以电压间隔δv。在一些实施例中,电压间隔δv在顺序的读取电压之间为固定的。在一些实施例中,电压间隔δv为不固定且可动态的更新。举例来说,若读取操作需要更快的速度,例如:存储器倾向高速,电压间隔δv可为较大,若读取做需要更高的精确度,例如:接近最佳读取电压的位置,电压间隔δv可为较小。

[0170]

如上述图4所示,对于每个读取电压页面中多个位(例如:位1)的电流被模数转换器电路累加,并且转换为对应模数转换器电路输出的数字值。在储存模数转换器电路的输出后,存储器例如:控制器,判断读取电压是否超出寻找范围(例如:图3中的寻找范围386)(步骤506)。寻找范围可为预设定的,例如:基于经验数据或可接受的读取电压变化。若读取电压仍然在寻找范围内,则读取电压被增加或减少,例如:以电压间隔δv,并且流程500回到步骤502。若读取电压在寻找范围之外,也就是说,横跨整个寻找范围的读取电压都已被使用,存储器例如:控制器,以模数转换器电路各自的输出值以及一系列的读取电压判断页面的校准读取电压(步骤508),例如:图3所示。在判断完校准读取电压后,流程500结束,存储器可接着以校准读取电压读取储存在页面中的数据。

[0171]

为了寻找或判断校准读取电压,一系列的读取电压可配置以不同的方式实施。在一些实施例中,读取电压逐渐地由预设定读取电压增加。在一些实施例中,读取电压逐渐地由预设定读取电压减少。在一些实施例中,读取电压首先逐渐地由预设定读取电压减少至较低电压,接着由预设定读取电压增加至更高的电压。在一些实施例中,读取电压首先逐渐地由预设定读取电压增加至较高电压,接着由预设定读取电压减少至较低电压,例如:如图6所示的进一步细节。

[0172]

图6示出根据本公开的一或多个实施例中,具有模数转换器电路的存储器判断校准读取电压的另一示例性流程图600。存储器可为图1a以及图1b中的存储器116。模数转换器电路可为图1a以及图1b中的模数转换器电路118。存储器可包含控制器,例如图1a以及图1b中的控制器117,配置为以模数转换器电路的输出判断校准(或最佳)读取电压。控制器可包含在模数转换器电路中的控制逻辑,例如:图1b中的控制逻辑132,或是可与控制逻辑以及模数转换器电路分离。流程600可由存储器执行。

[0173]

与图5的流程图500相似,流程600开始,例如:当存储器接收一读取要求读取页面的数据,存储器可以使用初始读取电压v

wl_initial

执行初始读取,并获得初始读出数据。若纠错码,例如:图1a中的纠错码译码器144,成功地解密读出数据,例如:任何数据中呈现的错

误位都可被侦测以及修正,则存储器不需要再执行流程600进一步的步骤,这代表初始读取电压可用于读取页面的数据。然而若纠错码译码读出数据失败,存储器可接着继续执行流程600以判断用于页面的校准读取电压以读出页面的数据。流程600寻找校准读取电压,通过首先逐渐地由初始读取电压v

wl_initia1

增加至位于较高寻找区域的较高电压x,例如:如步骤604、606、608、610所示,接着逐渐地从初始电压v

wl_initial

减少至位于较低寻找区域的较低电压y,例如:如步骤612、614、616、618所示。接着,可以基于在寻找期间所使用的读取电压的模数转换器电路的输出值,或是基于x以及y来判断校准读取电压。

[0174]

初始读取电压v

wl_initial

可为预设定值,例如:由存储器生产商基于经验或是已知的存储器特性预设。初始读取电压也可基于先前已知的最佳或校准读取电压做更新。在一些实施例中,由于每次写入/擦除次数会初始化页面,初始读取电压由存储器生产商设定为预设定值。

[0175]

与图5的步骤502以及504相似,在步骤602中,存储器以初始读取电压v

wl_initial

读取页面。若纠错码译码失败,则存储器触发模数转换器电路以累加页面中多个存储单元对应字线的电流以获得电流的总和,其可被模数转换器电路转换以及记录为数字电流值i1。

[0176]

接着读取电压增加,例如:以电压间隔δv。如以上所描述,电压间隔可为固定或是动态地更新,基于不同的准则。步骤604类似于步骤602,除了增加的读取变压用于读取同一页面。模数转换器电路累加页面上多个存储单元的电流以获得对应的数字电流值ii。

[0177]

在步骤606中,为了增加判断的准确度,模数转换器电路的两连续(或相邻)读取电压v

wli

、v

wli-1

的输出数字电流值ii、i

i-1

之间的差值δ

i-1

被取得,例如δ

i-1

=i

i-i

i-1

,其中i为大于1的整数。在步骤608,输出数字电流值ii以及i

i-1

之间的差值δ

i-1

与第一预设定阈值δ

th1

(例如基于经验数据)做比较。举例来说,第一预设定阈值实质上与0相同。若差值δ

i-1

不小于预设定阈值,其表示读取电压还未达到最佳(或校准)读取电压,读取电压可被进一步的增加,例如:以电压间隔δv。流程600接着回到步骤604,且执行新的读取操作。电压间隔可以和先前读取电压v

wli

的电压间隔相同,或可以小于或大于先前的电压间隔。接着流程600重复步骤606以及608,例如:如图所5示直到读取电压超出寻找范围。

[0178]

若差值δ

i-1

小于预设定阈值δ

th1

,其表示读取电压v

wli

实质上接近较高电压寻找区域中的最佳读取电压,在步骤610中,存储器(例如:控制器)判断第一校准读取电压x与读取电压v

wli

相同。

[0179]

流程600接着从初始读取电压开始,在较低电压寻找区域中执行寻找。初始读取电压可以逐渐地减少,例如:以电压间隔δv,电压间隔δv可以和较高电压寻找区域中使用的相同或不同。在步骤612中,与步骤604相似,页面以减少的读取电压v

wlj

读取,其中j为大于1的整数。模数转换器电路接着被触发以累加页面中多个存储单元对应字线的电流以获得电流的总和,其可被模数转换器电路转换以及记录为数字电流值ij。在步骤614中,与步骤606相似,模数转换器电路的两连续(或相邻)读取电压v

wlj

、v

wj-1

的输出数字电流值ij、i

j-1

之间的差值δ

j-1

被取得,例如:δ

j-1

=i

j-i

j-1

。

[0180]

在一些实施例中,与步骤608相似,输出数字电流值ij、i

j-1

之间的差值δ

j-1

可以和预设定阈值,例如:基于经验数据,做比较。若差值不小于预设定阈值,读取电压可被进一步的增加,并且流程600回到步骤612。若差值小于预设定阈值,存储器(例如:模数转换器电路或是控制器)可判断读取电压v

wlj

实质上接近较低电压寻找区域中的最佳读取电压。

[0181]

在一些实施例中为了进一步的提升准确性,如图6所示,在步骤616中,第一连续读取电压v

wlj

、v

wlj-1

的第一差值δ

j-1

以及相邻于第一连续读取电压的第二连续读取电压v

wlj-1

,v

wlj-2

的第二差值δ

j-2

两者之间的差值判断为|δ

j-1-δ

j-2

|。接着差值|δ

j-1-δ

j-2

|与可为预设定,例如:基于经验数据,的第二阈值电压δ

th2

做比较。若差值不小于第二阈值电压δ

th2

,则读取电压可进一步的减少,流程600接着回到步骤612。若差值小于第二阈值电压δ

th2

,则存储器(例如:模数转换器电路或控制器)可判断读取电压v

wlj

实质上接近较低电压寻找区域中的最佳读取电压。在步骤610中,存储器(例如:控制器)判断第二校准读取电压y与读取电压v

wlj

相同。在一些实施例中,也可根据用于判断y的步骤616和618来判断x。

[0182]

在步骤620中,最佳读取电压由至少一第一校准电压x或第二校准电压y来判断。举例来说,基于电压间隔δv的大小,y可以在最佳读取电压的左侧,而x可以在最佳读取电压的右侧。如图6所示,最佳读取电压可表示为:

[0183]vwl

=β(x-y) y

[0184]

若有任何的畸变(distortion),β可为0.4或0.6。在一些实施例中,若电压间隔δv足够小,x可被判断为最佳读取电压,β为1,或可y可被判断为最佳读取电压,β为0。

[0185]

本发明所公开的内容和实施例可应用于一或多个计算机程序产品,举例来说在一数据处理设备中,一或多个计算机程序指令模块编码于一计算机可读取介质中,用以执行或控制数据处理,该计算机可读取介质可为一机器可读取储存装置、一计算机可读取介质储存基体、一存储装置或者是以上的一或多个上述装置的结合。术语“数据处理设备”包括所有用于数据处理的设备、装置及机器,举例但不受限于,一可编程处理器、一计算机、多个处理器或多个计算机。该设备除了硬件外,还可包含为计算机程序提供一执行环境的编码,例如:组成处理器固件的编码、一协议栈(protocol stack)、一数据库管理系统、一执行中的系统或以上一或多个的结合。

[0186]

本发明中所公开的系统包括所有用于数据处理的设备、装置及机器,举例但不受限于一可编程处理器、一计算机、多个处理器或多个计算机。一系统除了硬件外,还可包含为计算机程序提供一执行环境的编码,例如:组成处理器固件的编码、一协议栈、一数据库管理系统、一执行中的系统或以上一或多个的结合。

[0187]

本发明所公开的计算机程序(亦被称为程序、软件、应用软件、脚本或编码)可以任何形式的程序语言编写,包含编码或译码语言,亦可以任何形式进行调配,例如:独立运作的程序或是一模块、一组件、一子程序或其他用于计算机运算环境的单元。本发明所公开的计算机程序并非一定对应于一档案系统中的单一档案,一程序可被储存在一包含其他程序或数据的档案中(例如:一或多个储存在标记式语言档案的脚本),该档案可为专属于该程序的单一档案,或多个互相配合的档案(例如:储存一或多个模块、子程序或部分编码的档案)。计算机程序可调配运行位于一或多处以通讯网路相连接的一或多台计算机。

[0188]

本发明示出的步骤与流程图能以一或多个可编程处理器运行一或多个计算机程序来执行所述的功能,该步骤与流程图的仪器也能以一特殊用途的逻辑电路,例如:一现场可编程逻辑门阵列(field programmable gate array,fpga)或一专用集成电路(application specific integrated circuit,asic)来实施。

[0189]

适用于运行该计算机程序的处理器包含,举例来说,通用或特殊用途的微处理器,或是一或多个数字计算机的一或多个处理器。一般来说,处理器会从一只读存储器或一随

机存取存储器中的其一或两者接收指令和数据,一计算机的必要元件包含一用于运行指令的处理器和一或多个用于储存指令和数据的存储装置。一般来说,一计算机包含或耦接一用于接收数据、传送数据至一或多个大量储存装置,例如:磁盘或磁光盘,进行数据储存,然而,该计算机不一定需要此装置。适用于储存计算机程序指令和数据的计算机可读取介质包含各种形式的非易失性存储器、媒体和存储装置,举例来说半导体存储装置,例如:可擦除可规划只读存储器(eprom)、电子擦除式可复写只读存储器(eeprom)、快闪存储装置和磁盘。该处理器与存储器可以特殊用途的逻辑电路加以辅助或合并使用。

[0190]

虽然本发明已以实施例公开如上,然其仅用于描述特定实施例中的技术特征,并非用以限定本发明的保护范围。在个别实施例中所描述的技术特征能相结合并应用于单一实施例中,相反的,单一实施例中所描述的多个技术特征亦能应用于个别或以次组合方式的多个实施例中。更进一步来说,虽然上述的技术特征的初始要求或是操作方法显示其需以特定方式做结合,然所要求结合的一或多个技术特征可以从中移除,其中要求结合可以是指次组合或是其相关的变形。相似地,图示中虽以特定顺序示出步骤,其并非要求该步骤一定要以特定步骤执行,或是所示出的所有步骤需全部执行,方能达到所述的结果。

[0191]

以上仅公开可能实施的多个范例,在不脱离本发明的范围内,当可作各种的更改、修改及增进。因此,本发明的保护范围视随附的权利要求书范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。