1.本发明实施例涉及半导体制造领域,尤其涉及一种半导体结构及其形成方法。

背景技术:

2.磁性随机存取存储器(magnetic random access memory,mram)是一种非挥发性的磁性随机存储器,所谓“非挥发性”是指关掉电源后,仍可以保持记忆完整。mram器件拥有静态随机存储器(sram)的高速读取写入能力,以及动态随机存储器(dram)的高集成度,而且基本上可以无限次地重复写入,磁性随机存取存储器是一种“全动能”的固态存储器。因而,其应用前景非常可观,有望主导下一代存储器市场。

3.mram是一种包括mram单元阵列的存储器件,每一个该mram单元使用电阻值而非电荷存储数据位。每个mram单元包括磁隧道结(mtj)单元,该磁隧道结(mtj)单元的电阻可以被调整,以代表逻辑“0”或逻辑“1”。该mtj单元包括固定磁层,隧穿势垒层以及磁自由磁层。该mtj单元的电阻,可以通过改变该磁自由磁层的磁矩相对于固定磁层的方向被调整。特别的,当磁自由磁层的磁矩与固定磁层的磁矩平行的时候,该mtj单元的电阻是低的,对应于逻辑0,反之,当该磁自由磁层的磁矩与固定磁层的磁矩不平行的时候,该mtj单元的电阻是高的,对应于逻辑1。该mtj单元在顶部和底部电极之间连接,并且可以检测到从一个电极到另一个流过该mtj单元的电流,以确定电阻,进而确定逻辑状态。

4.磁隧道结(mtj)中的隧道磁阻(tmr)效应是开发磁阻随机存取存储器(mram),磁传感器和新型可编程逻辑器件的关键。

技术实现要素:

5.本发明实施例解决的问题是提供一种半导体结构及其形成方法,提升半导体结构中磁隧道结单元的磁阻比,从而提升半导体结构的电学性能。

6.为解决上述问题,本发明实施例提供一种半导体结构的形成方法,包括:提供固定磁层;在所述固定磁层上形成隧穿势垒层;在所述隧穿势垒层上形成自由磁层;在所述自由磁层上形成第一盖帽层,所述第一盖帽层的材料包括二维材料。

7.可选的,形成所述自由磁层的步骤包括:在所述隧穿势垒层上形成第一自由分层;在所述第一自由分层上形成间隔层;在所述间隔层上形成第二自由分层。

8.可选的,采用原子层沉积工艺、化学气相沉积工艺或者电化学电镀工艺形成所述间隔层。

9.可选的,形成所述间隔层采用的反应物包括醇类前驱体。

10.可选的,所述间隔层的材料包括所述二维材料。

11.可选的,所述二维材料包括:石墨烯、二硫化钼和硅烯中的一种或多种。

12.可选的,形成所述间隔层的步骤中,所述间隔层的厚度为0.2纳米至1纳米。

13.可选的,形成所述第一盖帽层的步骤中,所述第一盖帽层的厚度为2纳米至3纳米。

14.可选的,采用原子层沉积工艺、化学气相沉积工艺或者电化学电镀工艺形成所述

第一盖帽层。

15.可选的,所述半导体结构的形成方法还包括:形成所述自由磁层后,形成所述第一盖帽层前,在所述自由磁层上形成第二盖帽层。

16.可选的,所述第二盖帽层的材料包括mgo、alo、aln和alon中的一种或多种。

17.可选的,所述半导体结构的形成方法包括:形成所述第二盖帽层后,在所述自由磁层上形成第一盖帽层前,在所述自由磁层上形成界面层。

18.可选的,所述界面层的厚度为1纳米至3纳米。

19.可选的,所述界面层的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。

20.可选的,采用原子层沉积工艺、化学气相沉积工艺或者电化学电镀工艺形成所述界面层。

21.相应的,本发明实施例还提供一种半导体结构,包括:固定磁层;隧穿势垒层,位于所述固定磁层上;自由磁层,位于所述隧穿势垒层上;第一盖帽层,位于所述自由磁层上,所述第一盖帽层的材料包括二维材料。

22.可选的,自由磁层包括第一自由分层、位于所述第一自由分层上的间隔层以及位于所述间隔层上的第二自由分层。

23.可选的,所述间隔层的材料包括所述二维材料。

24.可选的,所述半导体结构还包括:第二盖帽层,位于所述自由磁层和所述第一盖帽层之间。

25.可选的,所述第二盖帽层的材料包括mgo、alo、aln和alon中的一种或多种。

26.可选的,所述半导体结构还包括:界面层,位于所述第一盖帽层和所述第二盖帽层之间。

27.可选的,所述界面层的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。

28.与现有技术相比,本发明实施例的技术方案具有以下优点:

29.本发明实施例所提供的半导体结构的形成方法中,在所述自由磁层上形成第一盖帽层,第一盖帽层能够提供额外的垂直各向异性,所述第一盖帽层的材料包括二维材料,二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,有利于实现半导体结构的微型化,且二维材料具有较长的自选扩散长度,有利于提高半导体结构的写入效率,有利于提高半导体结构的电学性能。

30.可选方案中,形成所述自由磁层的步骤包括:在所述隧穿势垒层上形成第一自由分层;在所述第一自由分层上形成间隔层;在所述间隔层上形成第二自由分层。通常在形成所述第一盖帽层后,对所述固定磁层、隧穿势垒层以及自由磁层进行退火处理。所述间隔层形成在第一自由分层和第二自由分层之间,所述间隔层的材料结构稳定,在对所述退火处理的过程中,间隔层中的原子不易扩散至第一自由分层和第二自由分层中,第一自有分层和第二自由分层中的原子不易扩散至间隔层中,第一自由分层和第二自由分层中晶体原子排列的方向不易发生改变,使得所述半导体结构具有较高的磁各向异性和较高的隧道磁阻效应。

附图说明

31.图1示出了一种半导体结构的结构示意图;

32.图2示出了另一种半导体结构的结构示意图;

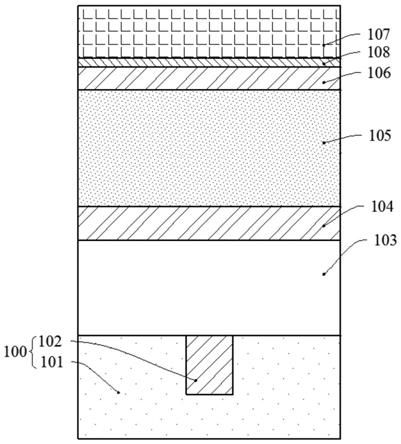

33.图3至图6是本发明半导体结构的形成方法第一实施例中各步骤对应的结构示意图;

34.图7是本发明半导体结构的形成方法第二实施例中各步骤对应的结构示意图;

35.图8是本发明半导体结构的形成方法第三实施例中各步骤对应的结构示意图。

具体实施方式

36.目前所形成的半导体结构仍有性能不佳的问题。现结合一种半导体结构的结构示意图分析半导体结构性能不佳的原因。

37.图1,示出了一种半导体结构的结构示意图。

38.如图1所示,所述半导体结构包括:固定磁层1;隧穿势垒层2,位于所述固定磁层1上;自由磁层3,位于所述隧穿势垒层2上;第一盖帽层4,位于所述自由磁层3上。

39.所述第一盖帽层4能够提供额外的垂直各向异性,使得半导体结构具有较大的磁阻比,提高半导体结构的电学性能,但所述第一盖帽层4的材料通常为mgo等非磁介电材料,导致半导体结构的电阻率较高,在半导体结构工作时,写入的功耗较高,且写入的速率不佳。

40.图2,示出了另一种半导体结构的结构示意图。

41.如图2所示,所述半导体结构包括:固定磁层10;隧穿势垒层20,位于所述固定磁层10上;自由磁层70,位于所述隧穿势垒层20上,所述自由磁层70包括第一自由分层30、位于所述第一自由分层30上的间隔层40以及位于所述间隔层40上的第二自由分层50;第一盖帽层60,位于所述自由磁层70上。

42.所述分隔层40位于所述第一自由分层30和第二自由分层50之间。所述分隔层40的材料通常为非磁金属,分隔层40能够增强第一自由分层30和第二自由分层50的铁磁耦合,有利于提高自由磁层70的垂直各向异性。通常所述第一自由分层30和第二自由分层50的材料均包括cofeb,所述分隔层40的材料包括ta,所述半导体结构的形成过程通常包括退火处理,在所述退火处理的过程中,第一自由分层30和第二自由分层50中的b易扩散入分隔层40中,所述分隔层40中的ta易扩散如第一自由分层30和第二自由分层50中,导致第一自由分层和第二自由分层中晶体原子排列的方向发生改变,降低所述半导体结构的磁各向异性和隧道磁阻效应。

43.为了解决所述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:提供固定磁层;在所述固定磁层上形成隧穿势垒层;在所述隧穿势垒层上形成自由磁层;在所述自由磁层上形成第一盖帽层,所述第一盖帽层的材料包括二维材料。

44.本发明实施例所提供的半导体结构的形成方法中,本发明实施例所提供的半导体结构的形成方法中,在所述自由磁层上形成第一盖帽层,第一盖帽层能够提供额外的垂直各向异性,所述第一盖帽层的材料包括二维材料,二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,有利于实现半导体结构的微型化,且二维材料具有较长的自选扩散长度,有利于提高半导体结构的写入效率,有利于提高半导体结构的电学性能。

45.为使本发明实施例的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

46.图3至图6是本发明实施例半导体结构的形成方法第一实施例中各步骤对应的结构示意图。

47.参考图3,提供固定磁层103。

48.所述固定磁层103具有固定的磁方向。后续在所述固定磁层103上形成隧穿势垒层、在所述隧穿势垒层上形成自由磁层,固定磁层103、隧穿势垒层以及自由磁层作为形成磁隧道结(mtj)单元。

49.本实施例中,所述固定磁层103为单一的膜层结构。其他实施例中,固定磁层可以为叠层结构,所述固定磁层包括被反铁磁层(antiferro-magnetic,afm)(图中未示出)和位于所述反铁磁层上的被钉扎层(fix layer)(图中未示出)。

50.本实施例中,采用物理气相沉积工艺(physical vapor deposition,pvd)形成所述固定磁层103。物理气相沉积工艺具有沉积温度低(常在550℃以下)、沉积速度快、沉积层的成分和结构可以控制、操作简单、高效率、低成本的优点,且物理气相沉积工艺与现有机台和工艺流程的兼容度高。其他实施例中,还可以采用化学气相沉积(chemical vapor deposition,cvd)或者原子层沉积工艺(atomic layer deposition,ald)形成所述固定磁层。

51.具体的,所述固定磁层103的材料包括:fecob、cofeta、nife和fept中的一种或多种。本实施例中,所述固定磁层103的材料包括fecob。其他实施例中,固定磁层还可以为亚铁磁层。

52.所述半导体结构的形成方法还包括:提供所述固定磁层103前,提供基底,所述基底100包括介质层101和位于所述介质层101中的导电结构102;提供固定磁层103的步骤中,所述固定磁层103的底部与所述导电结构102连接。

53.所述基底100用于为后续形成磁隧道结单元提供工艺平台。

54.本实施例中,所述介质层101底部形成有晶体管、电阻结构以及导电结构等功能结构。其中,所述晶体管可以为nmos晶体管和pmos晶体管中的一种或两种,具体的,所述晶体管包括栅极结构、位于栅极结构两侧的源漏掺杂区等功能结构。

55.所述介质层101用于实现导电结构102之间的电隔离,以及介质层101底部的器件与后续形成的磁隧道结单元之间的电隔离。

56.具体地,所述介质层101的材料为低k介质材料(低k介质材料指相对介电常数大于或等于2.6且小于等于3.9的介质材料)、超低k介质材料(超低k介质材料指相对介电常数小于2.6的介质材料)、氧化硅、氮化硅或氮氧化硅等介电材料。

57.本实施例中,所述介质层101的材料为低k介质材料,有利于降低后段互连结构之间的寄生电容,进而有利于减小后段rc延迟。在其他实施例中,根据实际的工艺,所述介质层还可以为金属层间介质层(imd)。

58.导电结构102底端与所述介质层101底部的所述晶体管中的源漏掺杂区连接,所述导电结构102的顶端用于与后续形成的磁隧道结单元的电连接。

59.本实施例中,所述导电结构102的材料为铜。在其他实施例中,所述导电结构的材料还可以为钴、钨等其他导电材料。

60.参考图4,在所述固定磁层103上形成隧穿势垒层104。

61.隧穿势垒层104用于固定磁层103和后续形成的自由磁层之间的电隔离,同时在适当的条件下允许电子隧穿通过隧穿势垒层104。

62.具体的,所述隧穿势垒层104的材料包括mgo、alo、aln或alon。本实施例中,所述隧穿势垒层104的材料包括mgo。

63.本实施例中,采用电子束蒸发工艺(electron beam evaporation,ebe)形成所述隧穿势垒层104。电子束蒸发工艺是采用电子束加热单晶的金属氧化物从而使所述单晶的金属氧化物熔融或升华气化,沉积于固定磁层103上经冷却后获得高纯度的隧穿势垒层104。其他实施例中,还可以采用等离子增强原子层沉积工艺、化学气相沉积工艺或物理气相沉积工艺形成所述隧穿势垒层。

64.参考图5,在所述隧穿势垒层104上形成自由磁层105。

65.所述自由磁层105、隧穿势垒层104以及固定磁层103为构成磁隧道结单元做准备。

66.所述自由磁层105具有自由的磁取向,在磁隧道结单元工作时,通常使用自旋转移力矩(stt)效应来改变或切换自由磁层105的磁极性,与所述固定磁层103的磁化方向平行或相反,从而使得磁隧道结单元能够处于低阻态或高组态。根据stt效应,电流流经磁隧道结单元,以感应自固定磁层103至自由磁层105的电子流。随着电子穿过固定磁层103,电子的自旋被极化。当自旋极化的电子到达自由磁层105时,自旋极化的电子将力矩施加于自由磁层105并且切换自由磁层105的状态。

67.具体的,自由磁层105的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述自由磁层105的材料包括cofeb。

68.本实施例中,采用物理气相沉积工艺形成所述自由磁层105。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述自由磁层。

69.所述半导体结构的形成方法还包括:在形成所述自由磁层105后,对所述固定磁层103、隧穿势垒层104以及自由磁层105进行退火处理。

70.退火处理使得固定磁层103中的fecob以及自由磁层105中的fecob由非晶态的转变成单晶态,所述隧穿势垒层104中的mgo由多晶态转变成单晶态,使得磁隧道结单元的隧道磁阻(tmr)效应较强;且退火处理能够使得固定磁层103和自由磁层105中的磁性粒子被磁化,使得所述固定磁层103和自由磁层105中的磁性粒子的自旋方向有序,使得形成的磁隧道结单元的隧道磁阻(tmr)效应较强。

71.具体的,通过强磁场退火的方式进行所述退火处理。

72.参考图6,在所述自由磁层105上形成第一盖帽层107,所述第一盖帽层107的材料包括二维材料。

73.本发明实施例中,在所述自由磁层105上形成第一盖帽层107,第一盖帽层107能够提供额外的垂直各向异性,所述第一盖帽层107的材料包括二维材料,二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,有利于实现半导体结构的微型化,且二维材料具有较长的自选扩散长度,有利于提高半导体结构的写入效率,有利于提高半导体结构的电学性能。

74.此外,在半导体结构工作时,第一盖帽层107,能够使得自由磁层105中的电子旋向,不易受到后续形成在第一盖帽层107上的膜层结构中载流子的影响,还能使得磁场和电

场被包含在自由磁层105与固定磁层103之间。

75.需要说明的是,所述二维材料的自旋扩散长度不宜过小。若所述二维材料的自旋扩散长度过小,导致磁性随机存储器的读写速率过慢。

76.具体的,所述二维材料包括:石墨烯、二硫化钼和硅烯中的一种或多种。本实施例中,所述二维材料包括:石墨烯。

77.本实施例中,采用原子层沉积形成所述第一盖帽层107。原子层沉积工艺包括进行多次的原子层沉积循环,有利于提高第一盖帽层107的厚度均一性、成分均匀性;此外,选用原子层沉积工艺有利于对第一盖帽层107的厚度进行精确控制。其他实施例中,还可以采用化学气相沉积工艺或者电化学电镀工艺形成所述第一盖帽层。

78.需要说明的是,形成所述第一盖帽层107的步骤中,所述第一盖帽层107的厚度不宜过大也不宜过小。形成所述第一盖帽层107的步骤中,若所述第一盖帽层107过厚,易降低磁隧道结单元的磁阻比,此外,会花费过多的工艺时间形成所述第一盖帽层107,导致所述第一盖帽层107的形成效率不高,还导致半导体结构在垂直于介质层101表面法线方向上的尺寸过大,导致半导体结构的电学性能不佳。形成所述第一盖帽层107的步骤中,若所述第一盖帽层107过薄,第一盖帽层107增加的垂直各向异性不显著,且所述第一盖帽层107的导通电阻较大,不易显著的降低半导体结构工作时的写入的功耗,半导体结构的写入的效率也较低;在半导体结构工作时,第一盖帽层107,不能很好的保护自由磁层105中的电子旋向不受到后续形成在第一盖帽层107上的膜层结构中载流子的影响,导致半导体结构的电学性能不佳。本实施例中,形成所述第一盖帽层107的步骤中,所述第一盖帽层107的厚度为2纳米至3纳米。

79.所述半导体结构的形成方法还包括:形成所述自由磁层105后,形成所述第一盖帽层107前,在所述自由磁层105上形成第二盖帽层106。

80.所述第二盖帽层106能够提供额外的垂直各向异性,且还能起到保护所述磁隧道结单元顶部的作用,在半导体结构工作时,磁隧道结单元具有较大的磁阻比,使得所述半导体结构具有优良的电学性能。

81.本实施例中,采用物理气相沉积工艺(physical vapor deposition,pvd)形成所述第二盖帽层106。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述第二盖帽层。

82.本实施例中,所述第二盖帽层106的材料包括mgo、alo、aln和alon中的一种或多种。

83.所述半导体结构的形成方法包括:形成所述第二盖帽层106后,在所述自由磁层105上形成第一盖帽层107前,在所述自由磁层105上形成界面层108。

84.所述界面层108用于为形成所述第一盖帽层107提供良好的生长界面,提高所述第一盖帽层107的形成质量,此外,所述界面层108还能够提高半导体结构的垂直各向异性。

85.具体的,所述界面层108的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述界面层108的材料包括fe、co、ni的合金。

86.需要说明的是,所述界面层108不宜过厚也不宜过薄。若所述界面层108过厚,会花费过多的工艺时间形成所述界面层108,还导致半导体结构在垂直于介质层101表面法线方向上的尺寸过大,导致半导体结构的垂直各向异性不佳。若所述界面层108过薄,所述界面

层108不能为形成第一盖帽层107提供良好的界面态,相应的所述第一盖帽层107的形成质量不佳,从而半导体结构工作时的写入的功耗较大,半导体结构的写入效率较低,导致提高半导体结构的电学性能不佳。本实施例中,所述界面层108的厚度为1纳米至3纳米。

87.本实施例中,采用原子层沉积工艺形成所述界面层108。原子层沉积工艺包括进行多次的原子层沉积循环,有利于提高界面层108的厚度均一性、成分均匀性;此外,选用原子层沉积工艺有利于对界面层108的厚度进行精确控制。其他实施例中,还可以采用化学气相沉积工艺或者电化学电镀工艺形成所述界面层。

88.参考图7,是本发明实施例半导体结构的形成方法第二实施例对应的结构示意图。

89.本发明实施例与第一实施例的相同之处在此不再赘述,本发明实施例与第一实施例的不同之处在于:

90.形成所述自由磁层205的步骤包括:在所述隧穿势垒层上形成第一自由分层2051;在所述第一自由分层2051上形成第二自由分层2052。

91.本实施例中,第一自由分层2051和第二自由分层2052之间能够直接形成铁磁耦合,有利于提高所述自由磁层205的垂直各向异性,且所述第一自由分层2051与第二自由分层2052间形成磁力线闭合,所述磁力线闭合可以避免外漏的磁力线造成磁隧道结单元之间磁化方向受影响,有利于提高所述磁隧道结单元的磁阻比。

92.具体的,所述第一自由分层2051的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述第一自由分层2051的材料包括cofeb。

93.本实施例中,采用物理气相沉积工艺形成所述第一自由分层2051。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述第一自由层。

94.所述第二自由分层2052的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,第二自由分层2052的材料包括co。

95.本实施例中,采用物理气相沉积工艺形成所述第二自由分层2052。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述第二自由层。

96.参考图8,是本发明实施例半导体结构的形成方法第三实施例对应的结构示意图。

97.本发明实施例与第一实施例的相同之处在此不再赘述,本发明实施例与第一实施例的不同之处在于:

98.形成所述自由磁层305的步骤包括:在所述隧穿势垒层上形成第一自由分层3051;在所述第一自由分层3051上形成间隔层3053;在所述间隔层3053上形成第二自由分层3052。

99.本实施例中,第一自由分层3051和第二自由分层3052之间能够直接形成铁磁耦合,有利于提高所述自由磁层305的垂直各向异性,且所述第一自由分层3051与第二自由分层3052间形成磁力线闭合,所述磁力线闭合可以避免外漏的磁力线造成磁隧道结单元之间磁化方向受影响,有利于提高所述磁隧道结单元的磁阻比。形成所述第一盖帽层后,会对自由磁层305、隧穿势垒层304以及固定磁层303进行退火处理,所述间隔层3053形成在第一自由分层3051和第二自由分层3052之间,所述间隔层3053的材料结构稳定,在对所述退火处理的过程中,间隔层3053中的原子不易扩散至第一自由分层3051和第二自由分层3053中,第一自有分层3051和第二自由分层3053中的原子不易扩散至间隔层3053中,间隔层3053、第一自由分层3051和第二自由分层3052中晶体原子排列的方向不易发生改变,使得所述半

导体结构具有较高的磁各向异性和较高的隧道磁阻效应。

100.具体的,第一自由分层3051和第二自由分层3052的材料均包括cofeb。在退火处理的过程中,第一自由分层3051和第二自由分层3052中的b不易扩散入所述间隔层3053中;且因为间隔层3053的结构稳定,所述间隔层3052中的原子不易扩散入第一自由分层3051和第二自由分层3052,第一自由分层3051和第二自由分层3052中晶体原子排列的方向不易发生改变,使得自由磁层305具有较高的垂直各向异性,增强磁隧道结单元的磁阻比。

101.具体的,所述第一自由分层3051的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述第一自由分层3051的材料包括cofeb。

102.本实施例中,采用物理气相沉积工艺形成所述第一自由分层3051。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述第一自由层。

103.本实施例中,所述间隔层3053的材料包括所述二维材料。

104.二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,有利于实现半导体结构的微型化,且二维材料具有较长的自选扩散长度,有利于提高半导体结构的写入效率,有利于提高半导体结构的电学性能。

105.需要说明的是,所述二维材料的自旋扩散长度不宜过小。若所述二维材料的自旋扩散长度过小,导致磁性随机存储器的读写速率过慢。

106.具体的,所述二维材料包括:石墨烯、二硫化钼和硅烯中的一种或多种。本实施例中,所述二维材料包括:石墨烯。

107.本实施例中,采用原子层沉积工艺、化学气相沉积工艺或者电化学电镀工艺形成所述间隔层3053。

108.需要说明的是,形成所述间隔层3053的步骤中,所述间隔层3053不宜过厚也不宜过薄。若所述间隔层3053过厚,相应的会花费过多的工艺时间形成所述间隔层3053,此外还导致半导体结构在垂直于介质层101表面法线方向上的尺寸过大,易导致第一自由分层3052和第二自由分层3051之间的铁磁耦合较弱,半导体结构易受外界干扰,导致数据保存的稳定性差。若所述间隔层3053过薄,第一自由分层3052和第二自由分层3051之间易形成反铁磁耦合,导致间隔层3053提供的垂直各向异性不显著,不易显著的降低半导体结构工作时的写入的功耗,且半导体结构的写入的效率较低,导致半导体结构的电学性能不佳。本实施例中,所述间隔层3053的厚度为0.2纳米至1纳米。

109.具体的,形成所述间隔层3053的反应物包括醇类前驱体。例如:甲醇、乙醇。

110.所述第二自由分层3052的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,第二自由分层3052的材料包括co。

111.本实施例中,采用物理气相沉积工艺形成所述第二自由分层3052。其他实施例中,还可以采用化学气相沉积或者原子层沉积工艺形成所述第二自由层。

112.相应的,本发明实施例还提供一种半导体结构。参考图6,示出了本发明半导体结构第一实施例的结构示意图。

113.所述半导体结构包括:固定磁层103;隧穿势垒层104,位于所述固定磁层103上;自由磁层105,位于所述隧穿势垒层104上;第一盖帽层107,位于所述自由磁层105上,所述第一盖帽层107的材料包括二维材料。

114.本发明实施例所提供的半导体结构中,第一盖帽层107位于所述自由磁层105上,

第一盖帽层107能够提供额外的垂直各向异性,所述第一盖帽层107的材料包括二维材料,二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,有利于实现半导体结构的微型化,且二维材料具有较长的自选扩散长度,有利于提高半导体结构的写入效率,有利于提高半导体结构的电学性能。

115.所述固定磁层103具有固定的磁方向。所述固定磁层103与隧穿势垒层104以及自由磁层105的作为磁隧道结(mtj)单元。

116.本实施例中,所述固定磁层103为单一的膜层结构。其他实施例中,固定磁层可以为叠层结构,所述固定磁层包括被反铁磁层(antiferro-magnetic,afm)(图中未示出)和位于所述反铁磁层上的被钉扎层(fix layer)(图中未示出)。

117.具体的,所述固定磁层103的材料包括:fecob、cofeta、nife和fept中的一种或多种。本实施例中,所述固定磁层103的材料包括fecob。其他实施例中,固定磁层还可以为亚铁磁层。

118.所述半导体结构还包括:基底位于所述固定磁层103的底部。

119.所述基底100包括介质层101和位于所述介质层101中的导电结构102;提供固定磁层103的步骤中,所述固定磁层103的底部与所述导电结构102连接。

120.所述基底100用于为磁隧道结单元提供工艺平台。

121.本实施例中,所述介质层101底部形成有晶体管、电阻结构以及导电结构等功能结构。其中,所述晶体管可以为nmos晶体管和pmos晶体管中的一种或两种,具体的,所述晶体管包括栅极结构、位于栅极结构两侧的源漏掺杂区等功能结构。

122.所述介质层101用于实现导电结构102之间的电隔离,以及介质层101底部的器件与磁隧道结单元之间的电隔离。

123.具体地,所述介质层101的材料为低k介质材料(低k介质材料指相对介电常数大于或等于2.6且小于等于3.9的介质材料)、超低k介质材料(超低k介质材料指相对介电常数小于2.6的介质材料)、氧化硅、氮化硅或氮氧化硅等介电材料。

124.本实施例中,所述介质层101的材料为低k介质材料,有利于降低后段互连结构之间的寄生电容,进而有利于减小后段rc延迟。在其他实施例中,根据实际的工艺,所述介质层还可以为金属层间介质层(imd)。

125.导电结构102底端与所述介质层101底部的所述晶体管中的源漏掺杂区连接,所述导电结构102的顶端用于与磁隧道结单元的电连接。

126.本实施例中,所述导电结构102的材料为铜。在其他实施例中,所述导电结构的材料还可以为钴、钨等其他导电材料。

127.隧穿势垒层104用于固定磁层103和自由磁层105之间的电隔离,同时在适当的条件下允许电子隧穿通过隧穿势垒层104。

128.具体的,所述隧穿势垒层104的材料包括mgo、alo、aln或alon。本实施例中,所述隧穿势垒层104的材料包括mgo。

129.所述自由磁层105具有自由的磁取向,在磁隧道结单元工作时,通常使用自旋转移力矩(stt)效应来改变或切换自由磁层105的磁极性,与所述固定磁层103的磁化方向平行或相反,从而使得磁隧道结单元能够处于低阻态或高组态。根据stt效应,电流流经磁隧道结单元,以感应自固定磁层103至自由磁层105的电子流。随着电子穿过固定磁层103,电子

的自旋被极化。当自旋极化的电子到达自由磁层105时,自旋极化的电子将力矩施加于自由磁层105并且切换自由磁层105的状态。

130.具体的,自由磁层105的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述自由磁层105的材料包括cofeb。其他实施例中,自由磁层还可以为亚铁磁层。

131.本发明实施例中,在所述自由磁层105上形成第一盖帽层107,第一盖帽层107能够提供额外的垂直各向异性,所述第一盖帽层107的材料包括二维材料,二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,提高写入的效率,且二维材料具有较长的自选扩散长度,有利于器件的微型化、低功耗,有利于提高半导体结构的电学性能。

132.此外,在半导体结构工作时,第一盖帽层107,能够使得自由磁层105中的电子旋向,不易受到后续形成在第一盖帽层107上的膜层结构中载流子的影响,还能使得磁场和电场被包含在自由磁层105与固定磁层103之间。

133.需要说明的是,所述二维材料的自旋扩散长度不宜过小。若所述二维材料的自旋扩散长度过小,会导致半导体结构的读写速率过小。

134.具体的,所述二维材料包括:石墨烯、二硫化钼和硅烯中的一种或多种。本实施例中,所述二维材料包括:石墨烯。

135.需要说明的是,所述第一盖帽层107的厚度不宜过大也不宜过小。若所述第一盖帽层107过厚,相应的会花费过多的工艺时间形成所述第一盖帽层107,此外还导致半导体结构在垂直于介质层101表面法线方向上的尺寸过大,降低磁隧道结单元的磁阻比。若所述第一盖帽层107过薄,第一盖帽层107增加的垂直各向异性不显著,且所述第一盖帽层107的导通电阻较大,不易显著的降低半导体结构工作时的写入的功耗,,半导体结构的写入的效率较低;在半导体结构工作时,第一盖帽层107,不能很好的保护自由磁层105中的电子旋向不受到后续形成在第一盖帽层107上的膜层结构中载流子的影响,导致半导体结构的电学性能不佳。本实施例中,所述第一盖帽层107的厚度为2纳米至3纳米。

136.所述半导体结构还包括:第二盖帽层106,位于所述自由磁层105和所述第一盖帽层107之间。

137.所述第二盖帽层106能够提供额外的垂直各向异性,且还能起到保护所述磁隧道结单元顶部的作用,在半导体结构工作时,磁隧道结单元具有较大的磁阻比,使得所述半导体结构具有优良的电学性能。

138.本实施例中,所述第二盖帽层106的材料包括mgo、alo、aln和alon中的一种或多种。

139.所述半导体结构还包括:界面层108,位于所述第一盖帽层107和所述第二盖帽层106之间。

140.所述界面层108用于为形成所述第一盖帽层107提供良好的生长界面,提高所述第一盖帽层107的形成质量,此外,所述界面层108还能够提高半导体结构的垂直各向异性。

141.具体的,所述界面层108的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述界面层108的材料包括fe、co、ni的合金。

142.需要说明的是,所述界面层108不宜过厚也不宜过薄。若所述界面层108过厚,会花费过多的工艺时间形成所述界面层108,还导致半导体结构在垂直于介质层101表面法线方

向上的尺寸过大,导致半导体结构的垂直各向异性不佳。若所述界面层108过薄,所述界面层108不能为形成第一盖帽层107提供良好的界面态,相应的所述第一盖帽层107的形成质量不佳,从而半导体结构工作时的写入的功耗较大,半导体结构的写入效率较低,导致提高半导体结构的电学性能不佳。本实施例中,所述界面层108的厚度为1纳米至3纳米。

143.参考图7,示出了本发明半导体结构第二实施例的结构示意图。

144.本发明实施例与第一实施例的形同之处在此不再赘述,本发明实施例与第一实施的不同之处在于:

145.所述自由磁层205包括第一自由分层2051和第二自由分层2052。

146.本实施例中,第一自由分层2051和第二自由分层2052之间能够直接形成铁磁耦合,有利于提高所述自由磁层205的垂直各向异性,且所述第一自由分层2051与第二自由分层2052间形成磁力线闭合,所述磁力线闭合可以避免外漏的磁力线造成磁隧道结单元之间磁化方向受影响,有利于提高所述磁隧道结单元的磁阻比。

147.具体的,所述第一自由分层2051的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,所述第一自由分层2051的材料包括cofeb。其他实施例中,第一自由分层还可以为亚铁磁层。

148.所述第二自由分层2052的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,第二自由分层2052的材料包括co。其他实施例中,第二自由分层还可以为亚铁磁层。

149.参考图8,示出了本发明半导体结构第三实施例的结构示意图。

150.本发明实施例与第一实施例的形同之处在此不再赘述,本发明实施例与第一实施的不同之处在于:

151.自由磁层305包括第一自由分层3051、位于所述第一自由分层3051上的间隔层3053以及位于所述间隔层3053上的第二自由分层3051。

152.本实施例中,第一自由分层3051和第二自由分层3052之间能够直接形成铁磁耦合,有利于提高所述自由磁层305的垂直各向异性,且所述第一自由分层3051与第二自由分层3052间形成磁力线闭合,所述磁力线闭合可以避免外漏的磁力线造成磁隧道结单元之间磁化方向受影响,有利于提高所述磁隧道结单元的磁阻比,所述半导体结构的形成过程中,会对自由磁层305、隧穿势垒层304以及固定磁层303进行退火处理,所述间隔层3053形成在第一自由分层3051和第二自由分层3052之间,所述间隔层3053的材料结构稳定,在对所述退火处理的过程中,间隔层3053中的原子不易扩散至第一自由分层3051和第二自由分层3053中,第一自有分层3051和第二自由分层3053中的原子不易扩散至间隔层3053中,第一自由分层3051和第二自由分层3052中晶体原子排列的方向不易发生改变,使得所述半导体结构具有较高的磁各向异性和较高的隧道磁阻比。

153.具体的,第一自由分层3051和第二自由分层3052的材料均包括cofeb。在退火处理的过程中,第一自由分层3051和第二自由分层3052中的b不易扩散入所述间隔层3053中;且因为间隔层3053的结构稳定,所述间隔层3052中的原子不易扩散入第一自由分层3051和第二自由分层3052,第一自由分层3051和第二自由分层3052中晶体原子排列的方向不易发生改变,使得自由磁层305具有较高的垂直各向异性,增强磁隧道结单元的磁阻比。

154.具体的,所述第一自由分层3051的材料包括feco、coni、cofeb、feb、fept、fepd,以

及fe、co、ni的合金。本实施例中,所述第一自由分层3051的材料包括cofeb。其他实施例中,第一自由分层还可以为亚铁磁层。

155.本实施例中,所述间隔层3053的材料包括所述二维材料。

156.且二维材料具有较低的电阻率,能够降低半导体结构工作时写入的功耗,提高写入的效率,且二维材料具有较长的自选扩散长度,有利于器件的微型化、低功耗以及数据保存可靠性的需求,有利于提高半导体结构的电学性能。

157.需要说明的是,所述二维材料的自旋扩散长度不宜过小。若所述二维材料的自旋扩散长度过小,隧道磁阻(tmr)效应较弱,导致读写速率过小。

158.具体的,所述二维材料包括:石墨烯、二硫化钼和硅烯中的一种或多种。本实施例中,所述二维材料包括:石墨烯。

159.需要说明的是,所述间隔层3053不宜过厚也不宜过薄。若所述间隔层3053过厚,相应的会花费过多的工艺时间形成所述间隔层3053,此外还导致半导体结构在垂直于介质层101表面法线方向上的尺寸过大,降低所述磁隧道结单元的磁阻比。若所述间隔层3053过薄,间隔层3053提供的垂直各向异性不显著,不易显著的降低半导体结构工作时的写入的功耗,且半导体结构的写入的效率较低,导致半导体结构的电学性能不佳。本实施例中,所述间隔层3053的厚度为0.2纳米至1纳米。

160.所述第二自由分层3052的材料包括feco、coni、cofeb、feb、fept、fepd,以及fe、co、ni的合金。本实施例中,第二自由分层3052的材料包括co。其他实施例中,第二自由分层还可以为亚铁磁层。

161.本实施例所述半导体结构可以采用前述实施例所述的形成方法所形成,也可以采用其他形成方法所形成。对本实施例所述半导体结构的具体描述,可参考前述实施例中的相应描述,本实施例在此不再赘述。

162.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。