1.本发明涉及计算机的技术领域,具体地,涉及面向处理器的数据传送指令实现方法及系统,尤其涉及一种面向专用处理器的多数据传送指令实现方法。

背景技术:

2.在计算机发展的早期,存储器的成本较高,因而希望通过尽可能少的指令以实现尽可能多的计算机操作,从而降低计算器程序所消耗的存储资源,这就导致了cisc设计风格的形成,即依靠增加指令复杂度及功能来提高计算机性能。基于cisc架构的处理器有着较强的处理高级语言的能力,因而代码量小,但为了应对不同的计算机操作,通常硬件设计复杂度较高。随着计算机技术的发展,统计数据表明在cisc架构下,在程序中各种指令的使用率相差悬殊(80%以上的指令在程序中很少使用),这就催生了risc架构的产生。risc是精简指令集计算机的缩写,其在cisc架构的基础上通过减少指令数量、规范指令格式、简化寻址方式和大量采用寄存器操作等简化了处理器的结构,从而大幅度提高了处理器性能、并行处理能力和性价比。

3.在risc架构中,采用load/store指令结构,减少了cisc架构中设置的存储器-存储器操作指令。risc指令系统中,只有load/store指令可以访问内存,其他指令均在寄存器之间对数据进行操作,由于处理器可在单周期内完成对寄存器的读写操作,这很好的平衡了cpu和内存存取的速度差异,提高了处理器的运行效率。但传统risc指令集中load/store指令通常灵活性较差,数据吞吐量小,无法发挥内存与处理器之间高速总线的性能。另一方面,随着技术的发展,对数据通信及处理速度提出了越来越高的要求,特别是在特定嵌入式专用处理器领域,如网络处理器中,在短时间内通常会发生大量的数据交换,因此传统的load/store指令将无法满足由此引发的实时性要求。为了解决该问题,提出了一种高速多数据存取的指令结构,对risc指令集中的load/store进行了扩展,该扩展提供了一种灵活的多数据搬移操作,提高了处理器对数据的存取速度和灵活性,进而实现快速响应、高速外部硬件控制和专用数据处理操作,以适用于实时性强的专用处理器设计。

4.在公开号为cn101364214a的专利文献中公开了一种由动态可重构集成电路组成的动态可重构指令计算机处理器,动态可重构集成电路连接动态可重构集成电路的配置电路、用户数据输入/输出电路、随机存储器、键盘、鼠标、显示器;动态可重构集成电路包括多个可重构单元,每个可重构单元由带配置队列的sram可重构电路和配置时钟构成;当对应的配置单元的配置时钟允许时对配置单元进行配置,即更新对应的指令;当配置时钟禁止时,不对配置单元配置数据进行更新,保留原有的配置,即保留原有的可重构指令。

5.计算机指令:计算机能够直接识别的以用来完成特定操作的命令。通常包括操作码和操作数,操作码决定要完成的操作,操作数指示参与运算的数据及其所在的单元地址等信息。

6.寄存器相对寻址:指操作数的地址由两部分组成,一部分存在于cpu的寄存器中,另一部分存在于计算机指令中,两者之和为操作数的地址。

7.基址变址寻址:指操作数的地址由两部分组成,两部分均存在于cpu的寄存器中,两项之和为操作数的地址。其中,一个寄存器中存储的地址为基址,另一个寄存器中存储变址。

8.asic:application specific integrated circuit,专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

9.cisc架构:complex instruction set computer架构,即复杂指令集计算机架构,在cisc架构中,指令格式和长度通常是可变的,指令相对较多,且指令执行周期不固定。

10.risc架构:reduced instrucion set computer架构,即精简指令集计算机架构,在risc架构中,指令格式和长度通常是固定的,指令相对较少,且大多数指令在一个周期内可以执行完毕。

11.哈佛结构:指指令和数据存储在不同的存储器中,两个存储器编址和访问独立,从而避免了cpu运行过程中指令和数据相互阻塞的情况。

12.已提出的risc指令集中load/store指令要么数据吞吐量较小,无法发挥高速总线的性能,要么灵活性较差,无法满足专用处理器的需求。随着技术的发展,对数据通信及处理速度提出了越来越高的要求,特别是在特定嵌入式专用处理器领域,如网络处理器,在短时间内通常会发生大量的不确定性的数据交换,因此传统的load/store指令将无法满足由此引发的实时性要求。因此,需要提出一种技术方案以改善上述技术问题。

技术实现要素:

13.针对现有技术中的缺陷,本发明的目的是提供一种面向处理器的数据传送指令实现方法及系统。

14.根据本发明提供的一种面向处理器的数据传送指令实现方法,所述方法包括如下步骤:

15.步骤s1:risc专用处理器译码得到读内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从内存搬移到指定的多个寄存器中;

16.步骤s2:risc专用处理器译码得到写内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从寄存器搬移到指定的内存地址中。

17.优选地,基于risc架构,以risc中load/store指令为基础进行扩展,内存寻址方式采用了寄存器相对寻址和基址变址寻址。

18.优选地,采用lmr和smr分别指示读内存和写内存指令,其中l和s分别代表load和store,m代表多个字节存取操作,r代表内存基址来自寄存器。

19.优选地,得到两种指令:lmr reg.m.i,reg.n(a),b和smr reg.m.i,reg.n(a),b;其中reg.m代表要读写的首个寄存器,i对应该寄存器内的第i个字节为读写起始位置,value(reg.n) a为要存取的内存的首地址,value(reg.n)代表对应寄存器内的数值,a为地址偏移量,来自寄存器或者立即数;b为存取的字节数,来自寄存器或立即数。

20.优选地,操作码lmr/smr的位域宽度为4,对应指令码中的bit[3:0];操作数reg.m.i的位域宽度为7,对应指令码中的bit[31:25]。

[0021]

优选地,操作数reg.n的位域宽度为5,对应指令码中的bit[24:20];操作数a和b的位域宽度8,分别对应指令码中的bit[19:12]和bit[11:4]。

[0022]

优选地,操作数reg.m.i采用字节寻址方式;reg.n采用32位寄存器的数值作为基地址,以最大化寻址空间;a和b可采用单字节数值或32位寄存器中的数值和立即数,增加了寻址空间或搬移的字节范围。

[0023]

优选地,将技术方案中的reg.n置换为con.n,由此引入两个新的指令lmc reg.m.i,con.n(a),b和smc reg.m.i,con.n(a),b;其中,指令中的c代表内存首地址来自常量表,con.n代表内存首地址来自于常量表中的第n项。

[0024]

优选地,32位risc cpu为哈佛harvard结构,指令采用流水线实现,流水线分为5级:

[0025]

取指:处理器将指令存储器中的内容保存到指令寄存器中;

[0026]

译码:对本发明的多数据操作指令进行译码,以区分不同的指令,并确定存取的寄存器和内存基址、偏移地址及存取的字节数;

[0027]

执行:根据内存基址及偏移地址计算实际内存首地址;

[0028]

访存:根据译码得到的指令对总线发起请求,进行多数据搬移操作;

[0029]

写回:对于load类指令,将内存中返回的数据写入寄存器。

[0030]

本发明还提供一种面向处理器的数据传送指令实现系统,所述系统包括如下模块:

[0031]

模块m1:risc专用处理器译码得到读内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从内存搬移到指定的多个寄存器中;

[0032]

模块m2:risc专用处理器译码得到写内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从寄存器搬移到指定的内存地址中。

[0033]

与现有技术相比,本发明具有如下的有益效果:

[0034]

1、本发明提供了一种适用于risc专用处理器的指令扩展,实现了多数据的快速搬移操作;

[0035]

2、本发明提供了一种可行的指令域划分方案具有寻址范围大,寻址方式灵活等优势,从而提高了多数据传送指令的运行效率,这有益于专用处理器应用中的多数据搬移操作,特别是网络处理器领域,通常需要快速的顺序搬移大量数据,该指令将极大地提高专用处理器的运行效率;

[0036]

3、本发明引入了常量表寄存器,通过引入常量表寄存器,进一步提高了指令运行效率和数据处理速度,这种效率的提高来自于risc架构下,不同设备所对应的内存基址通常是固定不变的,将使用率较高的寄存器基址存于常量表寄存器中,在执行多数据搬移指令时将不用设置通用寄存器的数值,减少了指令数,从而提高了专用处理器的指令运行效率和数据处理速度。

附图说明

[0037]

通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

[0038]

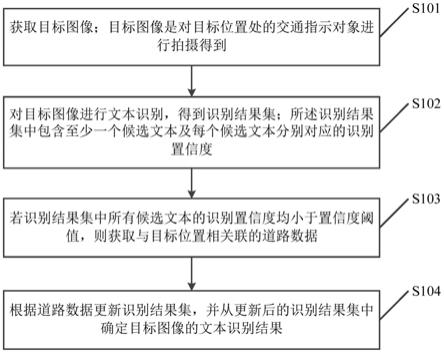

图1为本发明risc顶层模块结构示意图;

[0039]

图2为本发明汇编指令中各个字段的含义图;

[0040]

图3为本发明一种可行的指令位域划分方案图。

reg.m.i,con.n(a),b。其中,指令中的c代表内存首地址来自常量表,在具体是实施过程中,可根据需要在常量表中填入特定值以方便汇编程序调用。con.n代表内存首地址来自于常量表中的第n项。此时,图3中的操作码将由lmc和smc决定,而位域中第20到第24位的数值将指示常量表的第n项,其余部分保持不变。根据图3所示,本发明的指令域划分方案最多支持32个常量表寄存器。至此,本发明共给出了四个用于专用处理器的多数据搬移指令,具体总结为:

[0049]

lmr reg.m.i,reg.n(a),b;

[0050]

smr reg.m.i,reg.n(a),b;

[0051]

lmc reg.m.i,con.n(a),b;

[0052]

smc reg.m.i,con.n(a),b。

[0053]

参照图3,本发明给出一种具体的电路实施例。本实施例中的32位risc cpu假定为哈佛harvard结构,指令采用流水线实现,流水线分为5级:

[0054]

取指:处理器将指令存储器中的内容保存到指令寄存器中;

[0055]

译码:对本发明的多数据操作指令进行译码,以区分不同的指令,并确定存取的寄存器和内存基址、偏移地址及存取的字节数;

[0056]

执行:根据内存基址及偏移地址计算实际内存首地址;

[0057]

访存:根据译码得到的指令对总线发起请求,进行多数据搬移操作;

[0058]

写回:对于load类指令,将内存中返回的数据写入寄存器。

[0059]

本发明还提供一种面向处理器的数据传送指令实现系统,所述系统包括如下模块:模块m1:risc专用处理器译码得到读内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从内存搬移到指定的多个寄存器中;模块m2:risc专用处理器译码得到写内存指令,根据指令中给出的内存地址和寄存器首地址将特定长度字节的数据从寄存器搬移到指定的内存地址中。

[0060]

本发明提供了一种适用于risc专用处理器的指令扩展,实现了多数据的快速搬移操作;本发明提供了一种可行的指令域划分方案具有寻址范围大,寻址方式灵活等优势,从而提高了多数据传送指令的运行效率,这有益于专用处理器应用中的多数据搬移操作,特别是网络处理器领域,通常需要快速的顺序搬移大量数据,该指令将极大地提高专用处理器的运行效率。

[0061]

本发明引入了常量表寄存器,通过引入常量表寄存器,进一步提高了指令运行效率和数据处理速度,这种效率的提高来自于risc架构下,不同设备所对应的内存基址通常是固定不变的,将使用率较高的寄存器基址存于常量表寄存器中,在执行多数据搬移指令时将不用设置通用寄存器的数值,减少了指令数,从而提高了专用处理器的指令运行效率和数据处理速度。

[0062]

本领域技术人员知道,除了以纯计算机可读程序代码方式实现本发明提供的系统及其各个装置、模块、单元以外,完全可以通过将方法步骤进行逻辑编程来使得本发明提供的系统及其各个装置、模块、单元以逻辑门、开关、专用集成电路、可编程逻辑控制器以及嵌入式微控制器等的形式来实现相同功能。所以,本发明提供的系统及其各项装置、模块、单元可以被认为是一种硬件部件,而对其内包括的用于实现各种功能的装置、模块、单元也可以视为硬件部件内的结构;也可以将用于实现各种功能的装置、模块、单元视为既可以是实

现方法的软件模块又可以是硬件部件内的结构。

[0063]

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本技术的实施例和实施例中的特征可以任意相互组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。